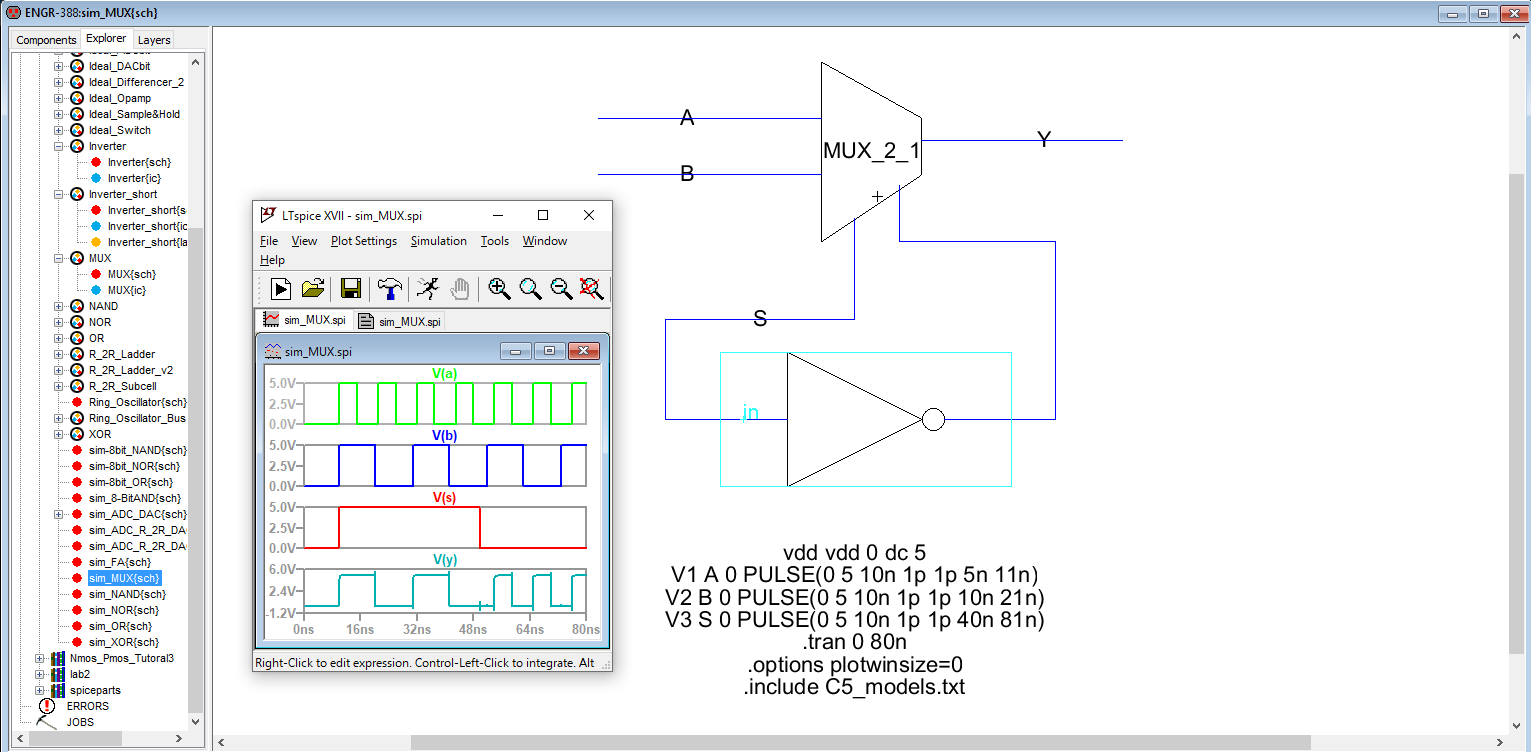

Figure 1: Simulated and Constructed 1-bit MUX.

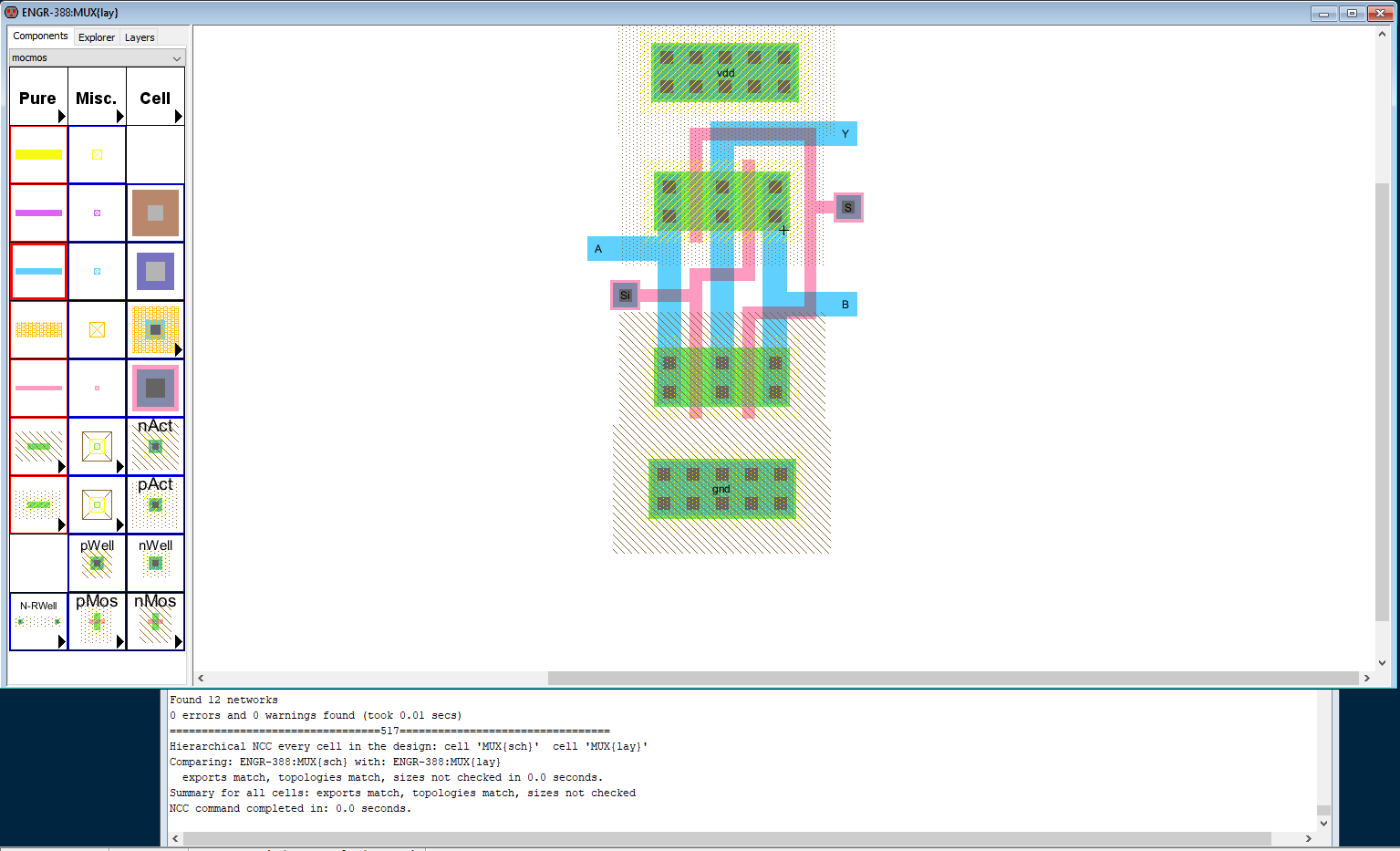

Figure 2: Layout for 1-bit MUX.

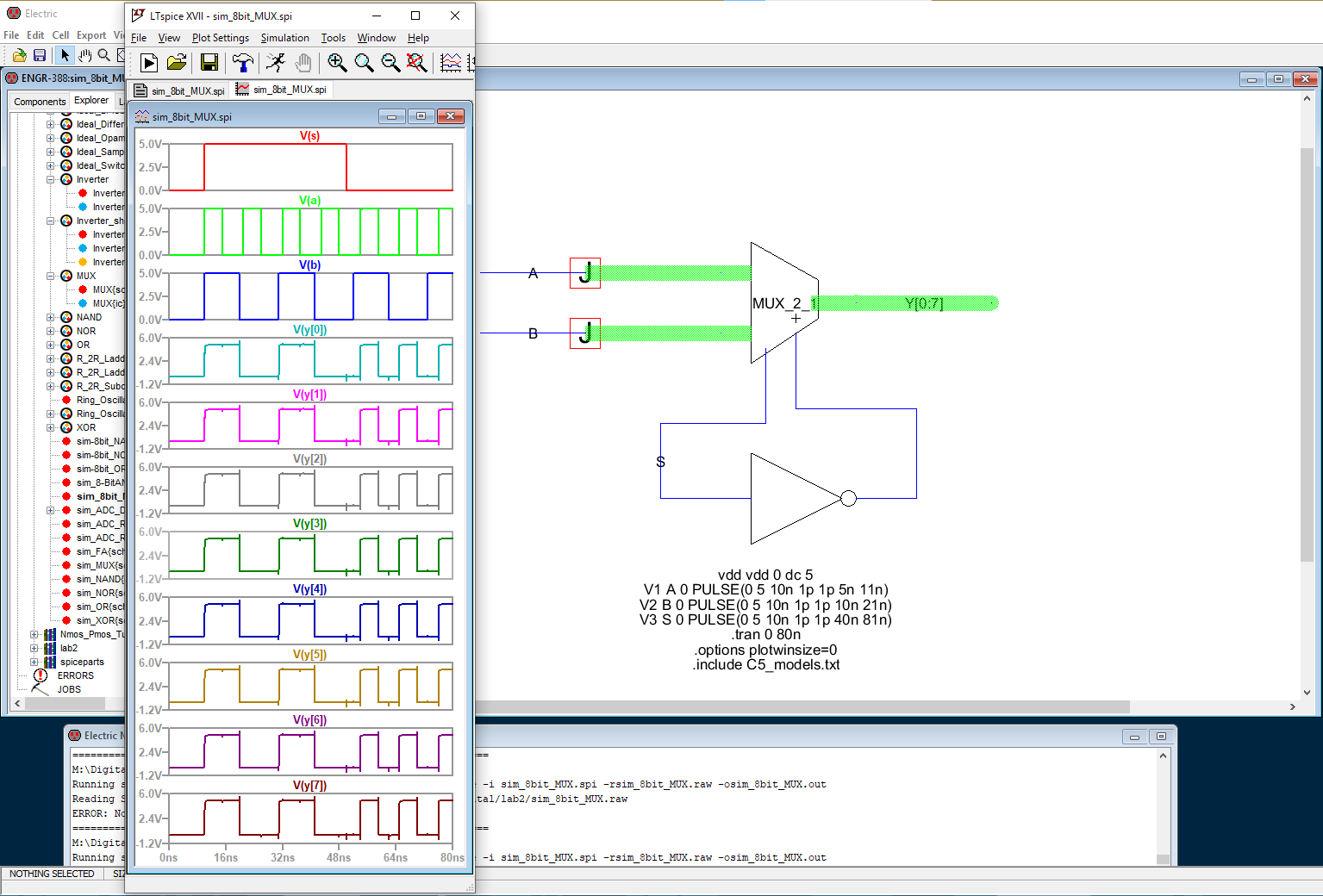

Figure 3: Simulated schematic of an 8-bit MUX.

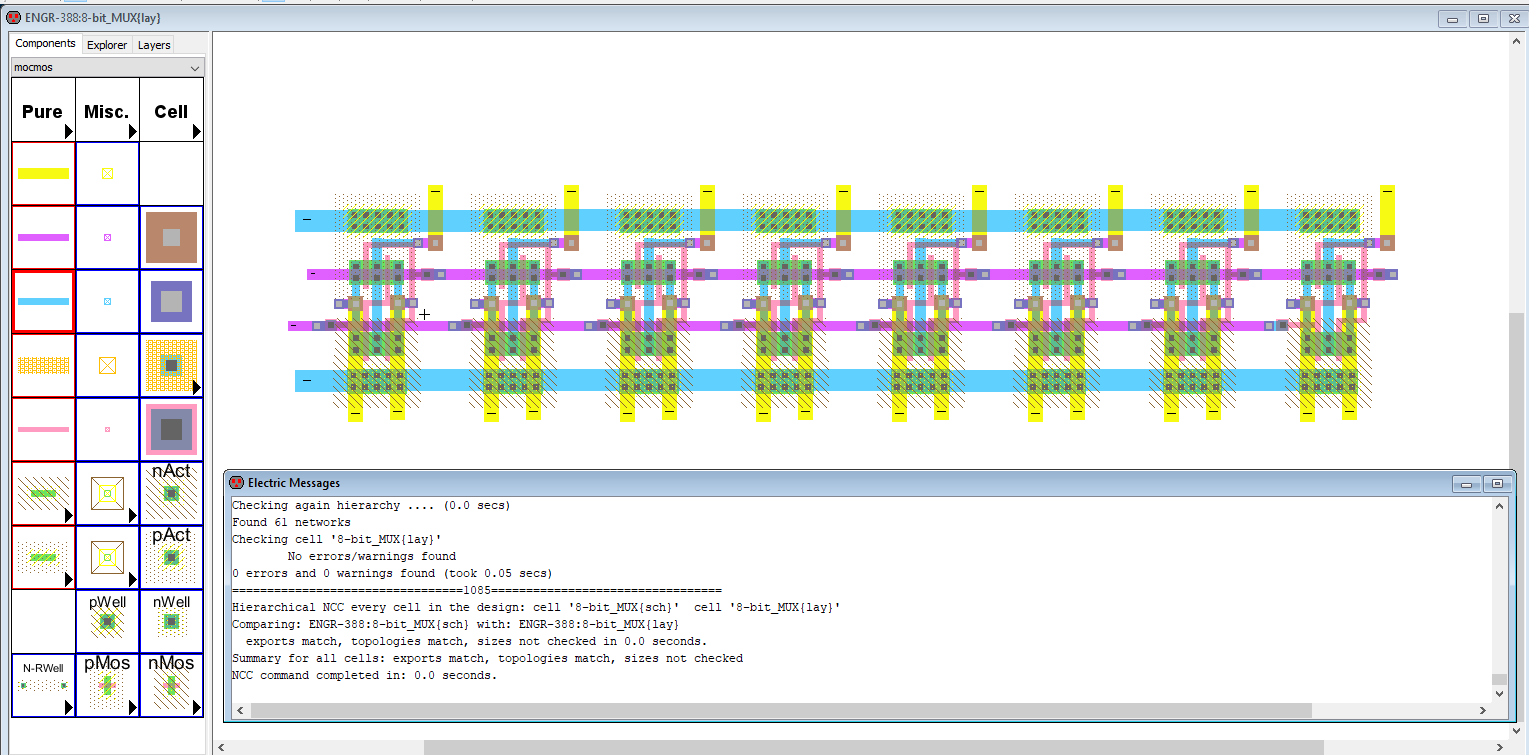

Figure 4: 8-bit MUX layout.

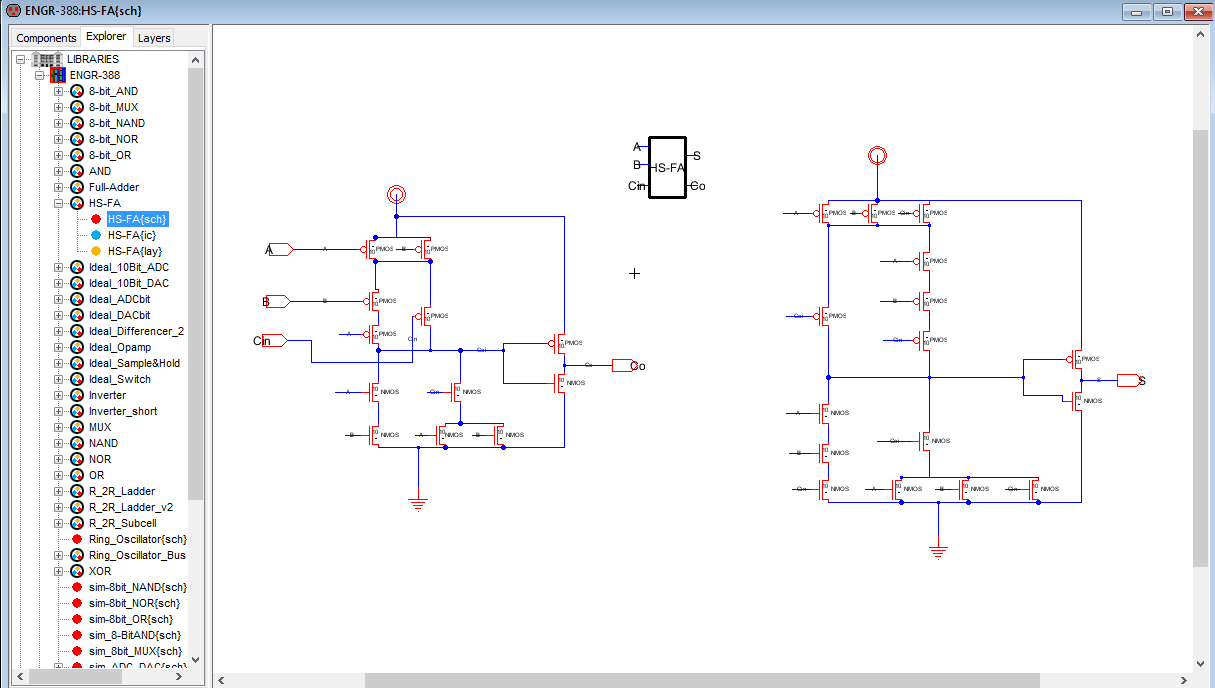

Task 2: Build a 1-bit high-speed full adder.

Figure 5: Schematic for high-speed full adder.

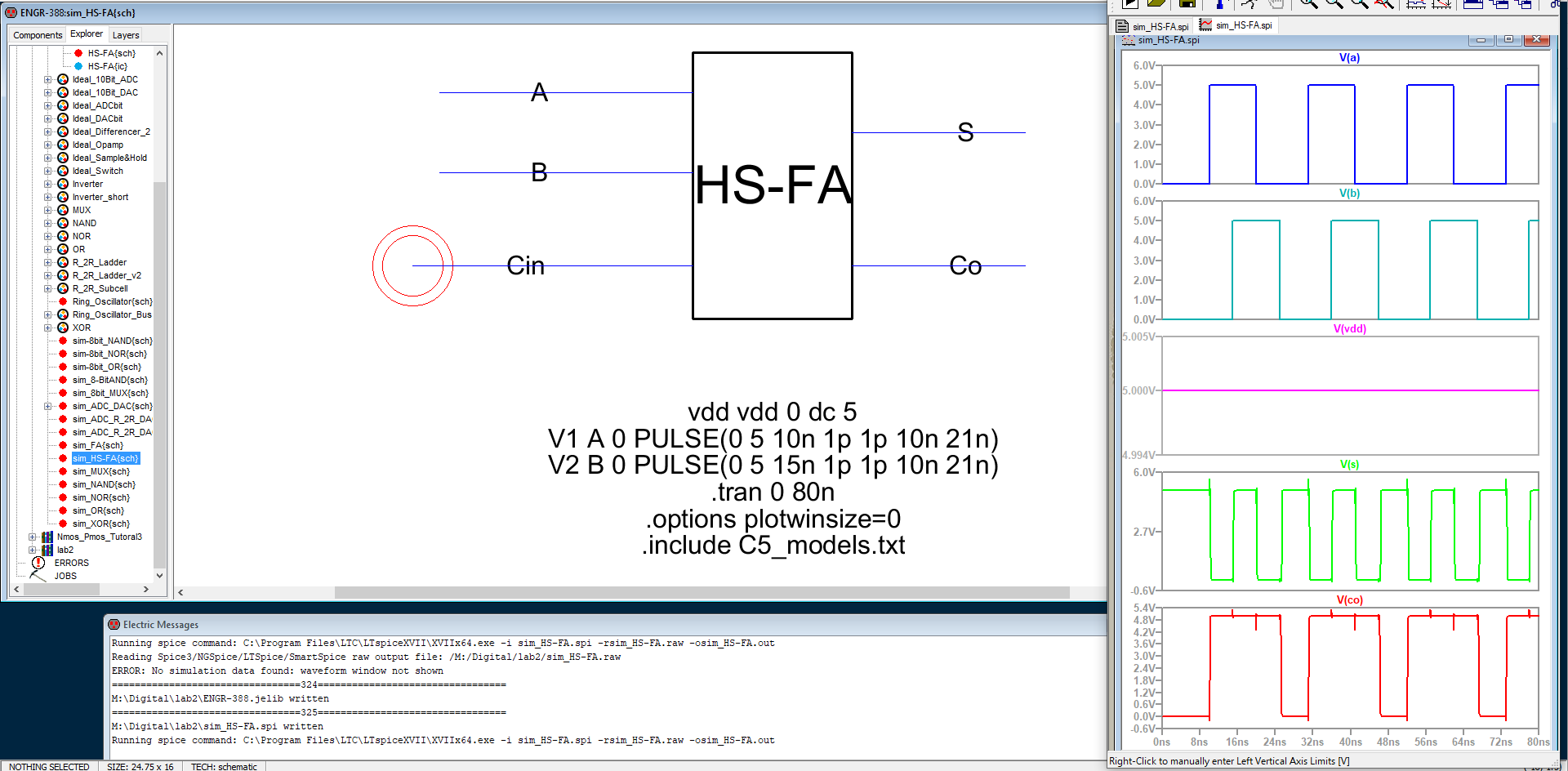

Figure 6: Simulated high-speed full adder.

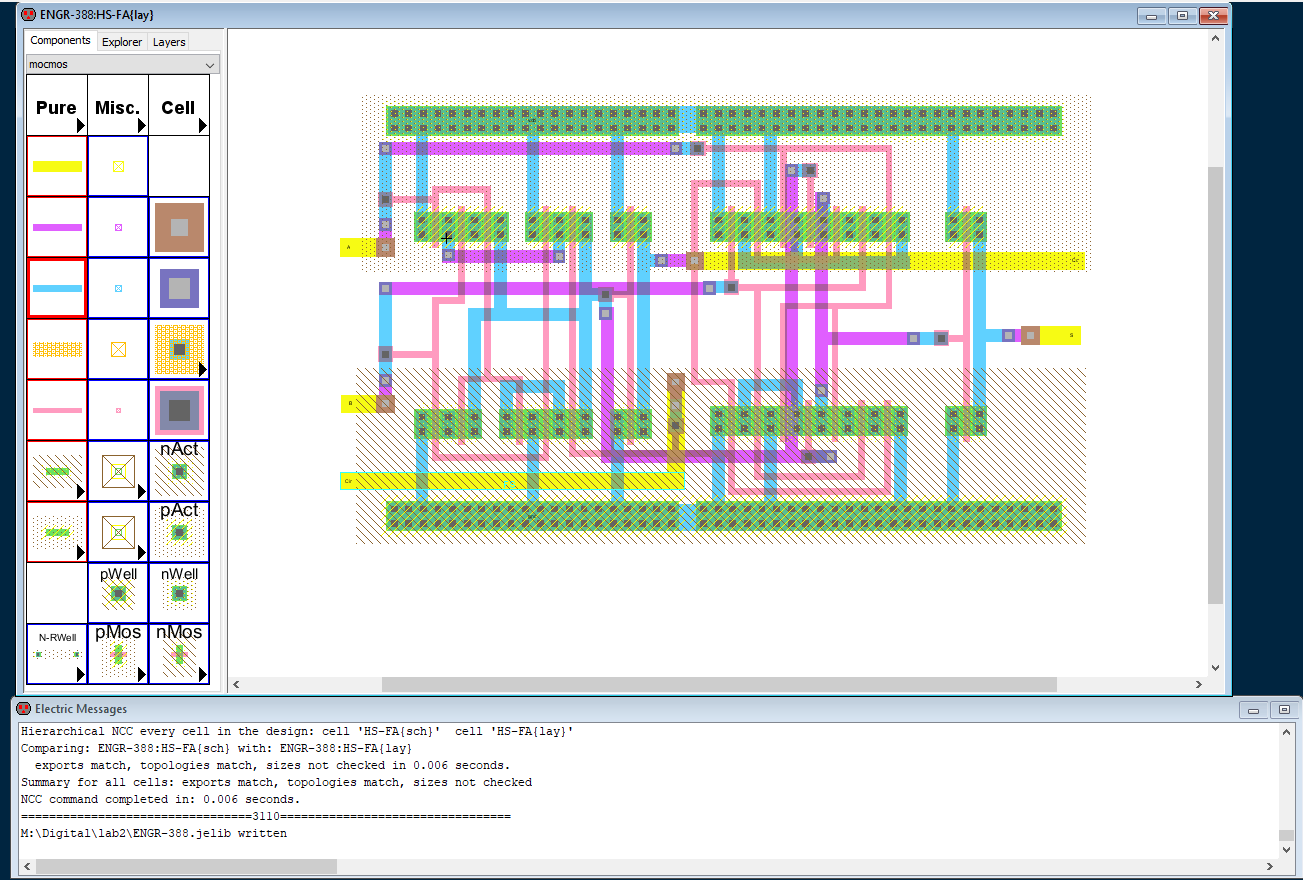

Figure 7: Layout for the high-speed full adder.

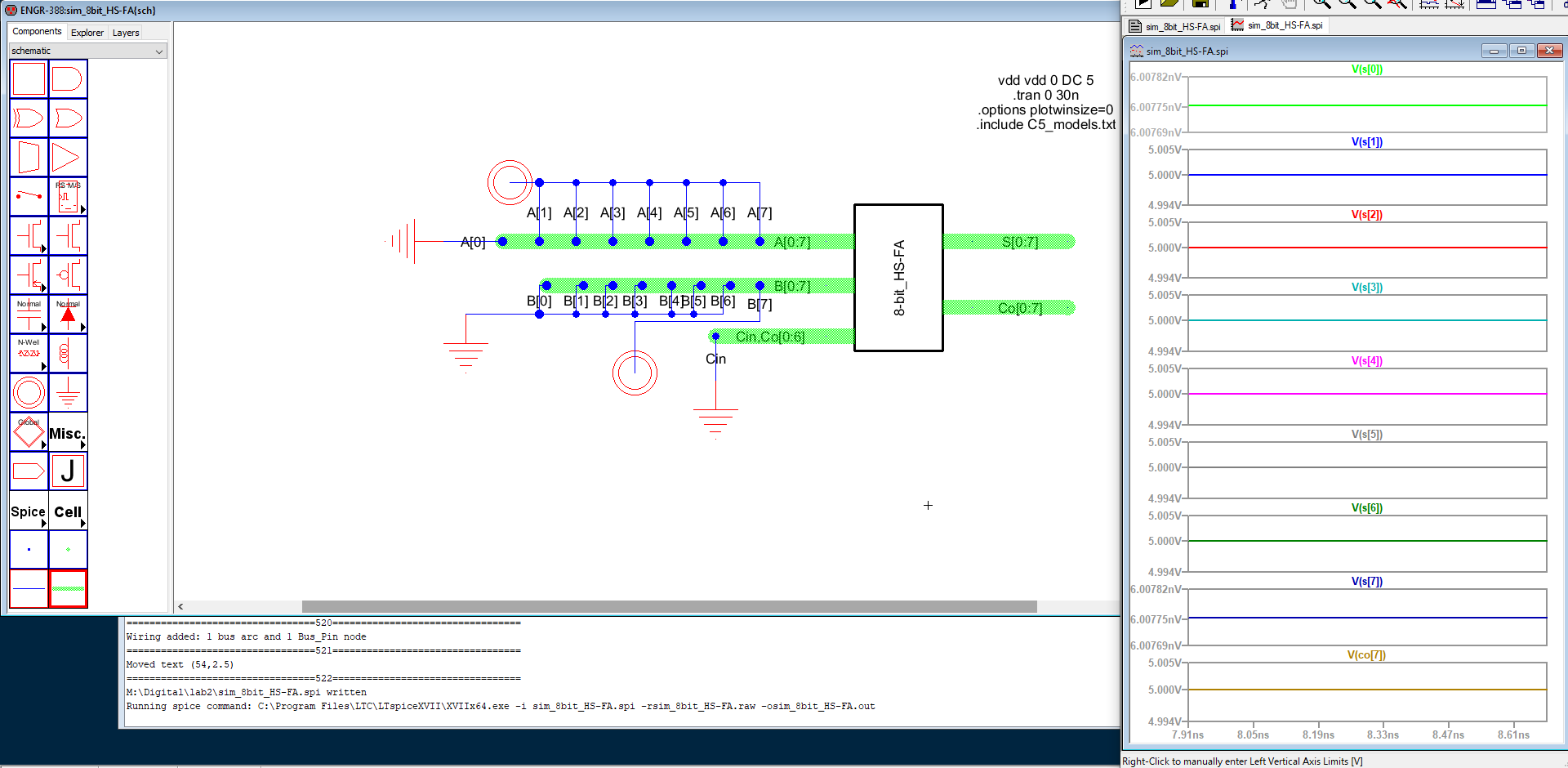

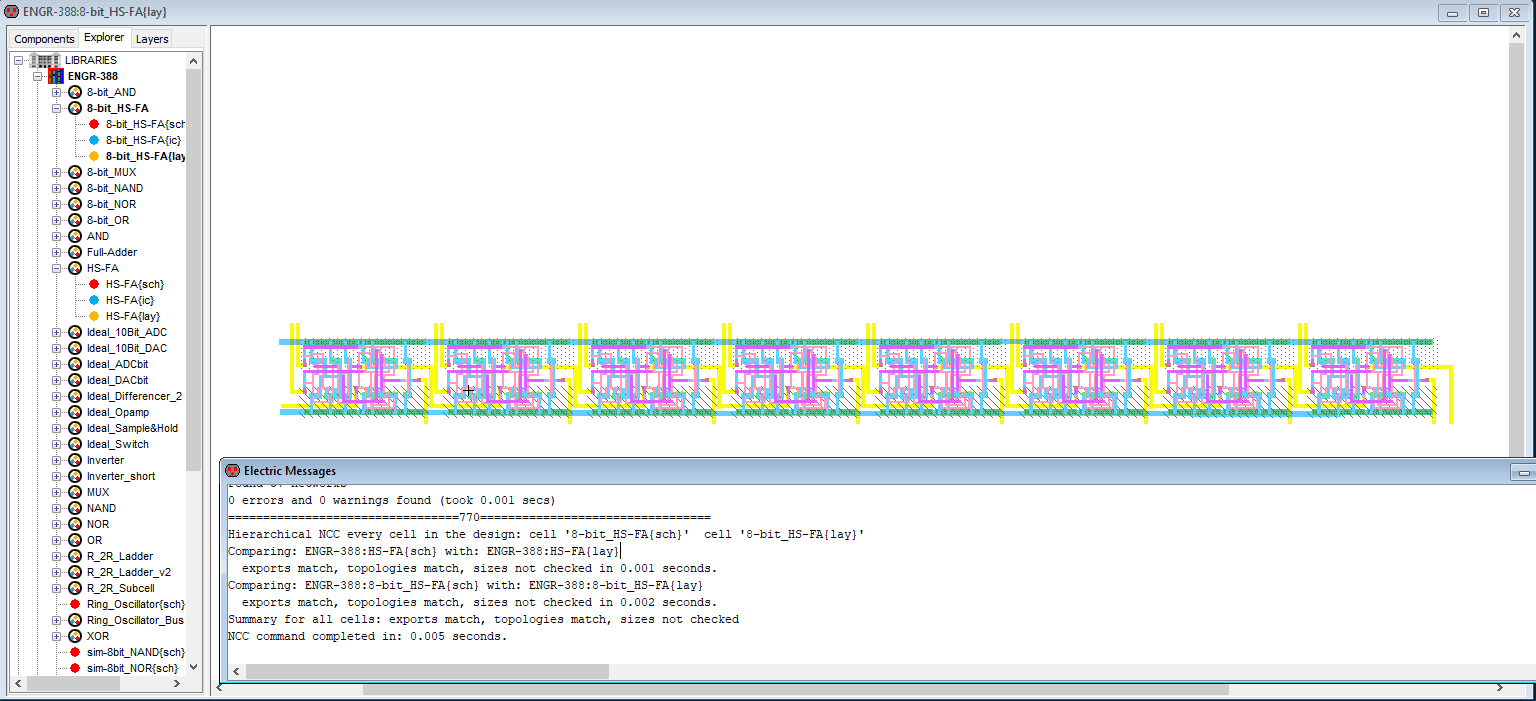

Task 3: 8-bit high-speed full adder.

Figure 8: Simulated schematic for 8-bit full adder

Figure 9: Layout for high-speed full adder.