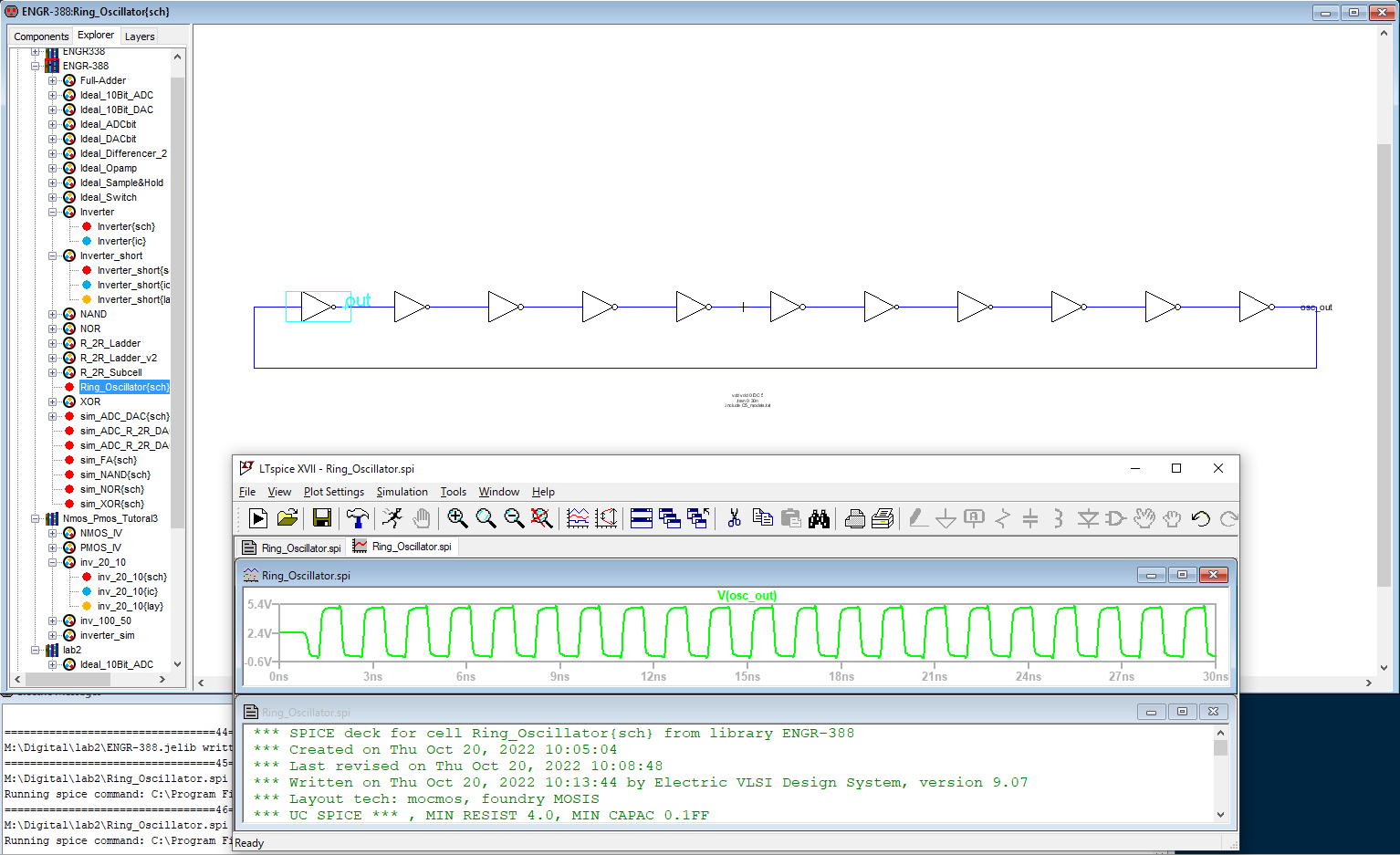

Figure 1: Ring Oscillator Schematic.

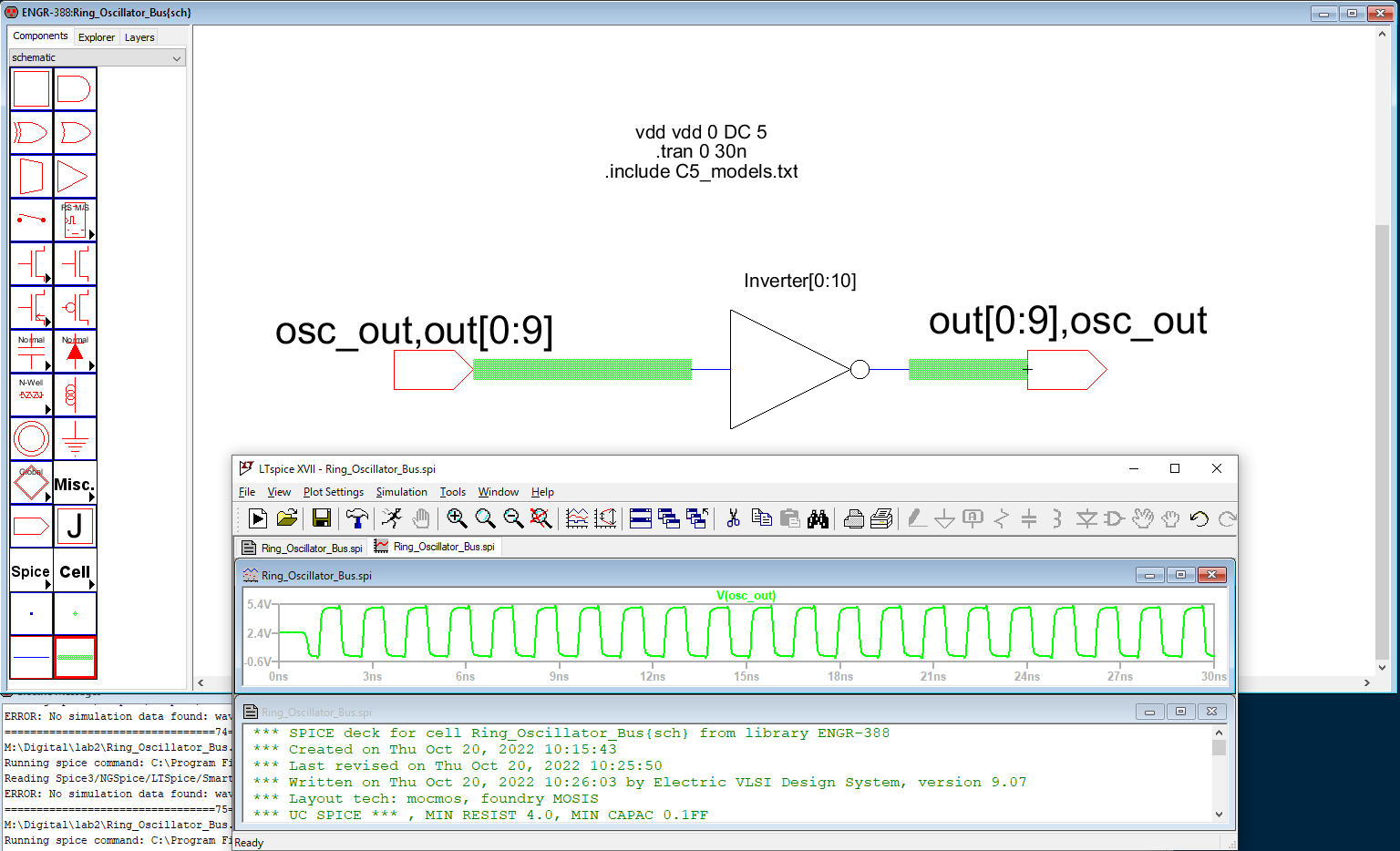

Figure 2: Ring Oscillator Bus Schematic.

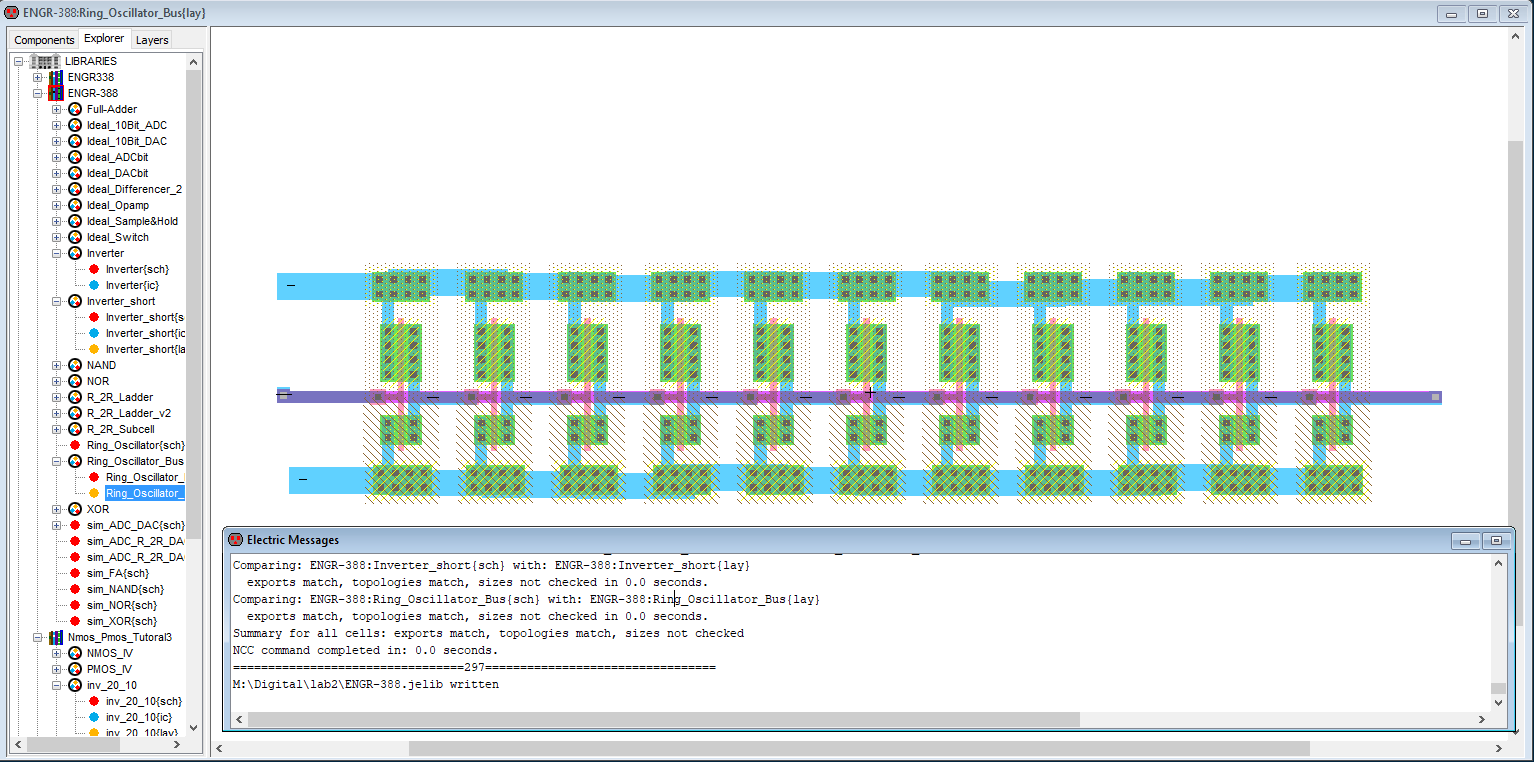

Figure 3: Ring Oscillator Bus Layout.

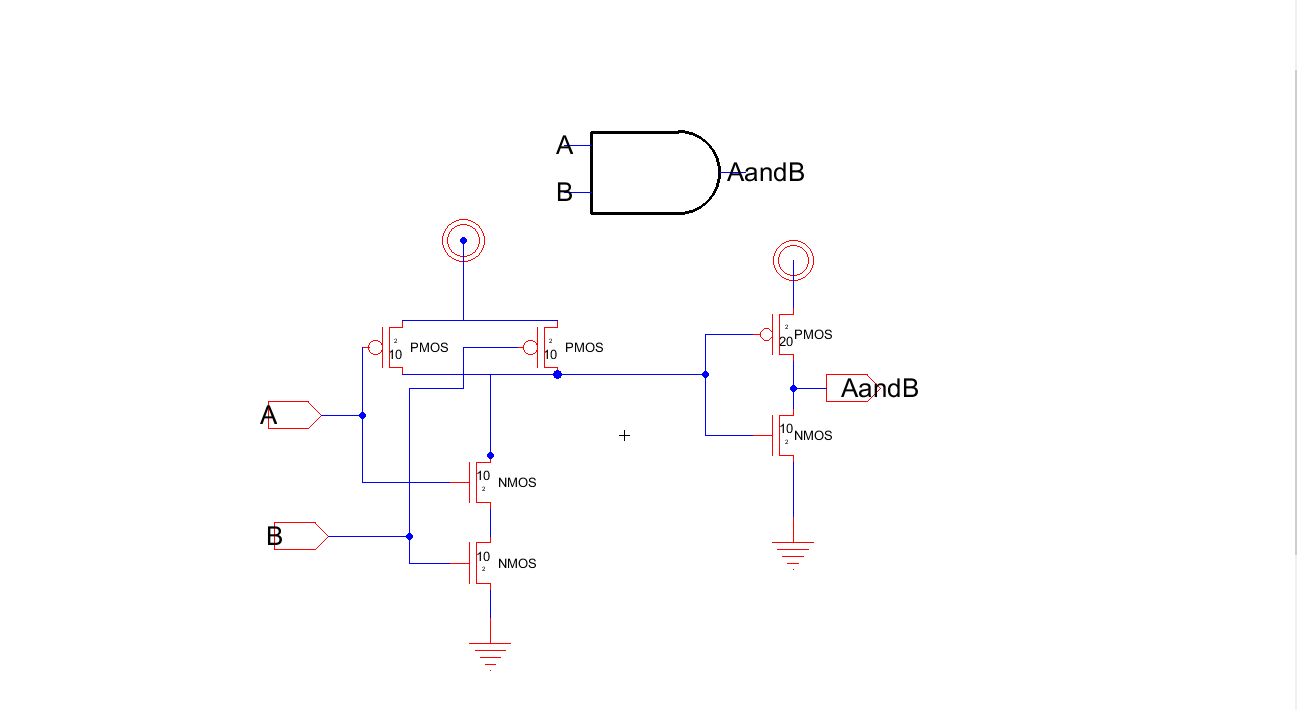

Task 2: 8-bit AND gate

Figure 4: AND Schematic.

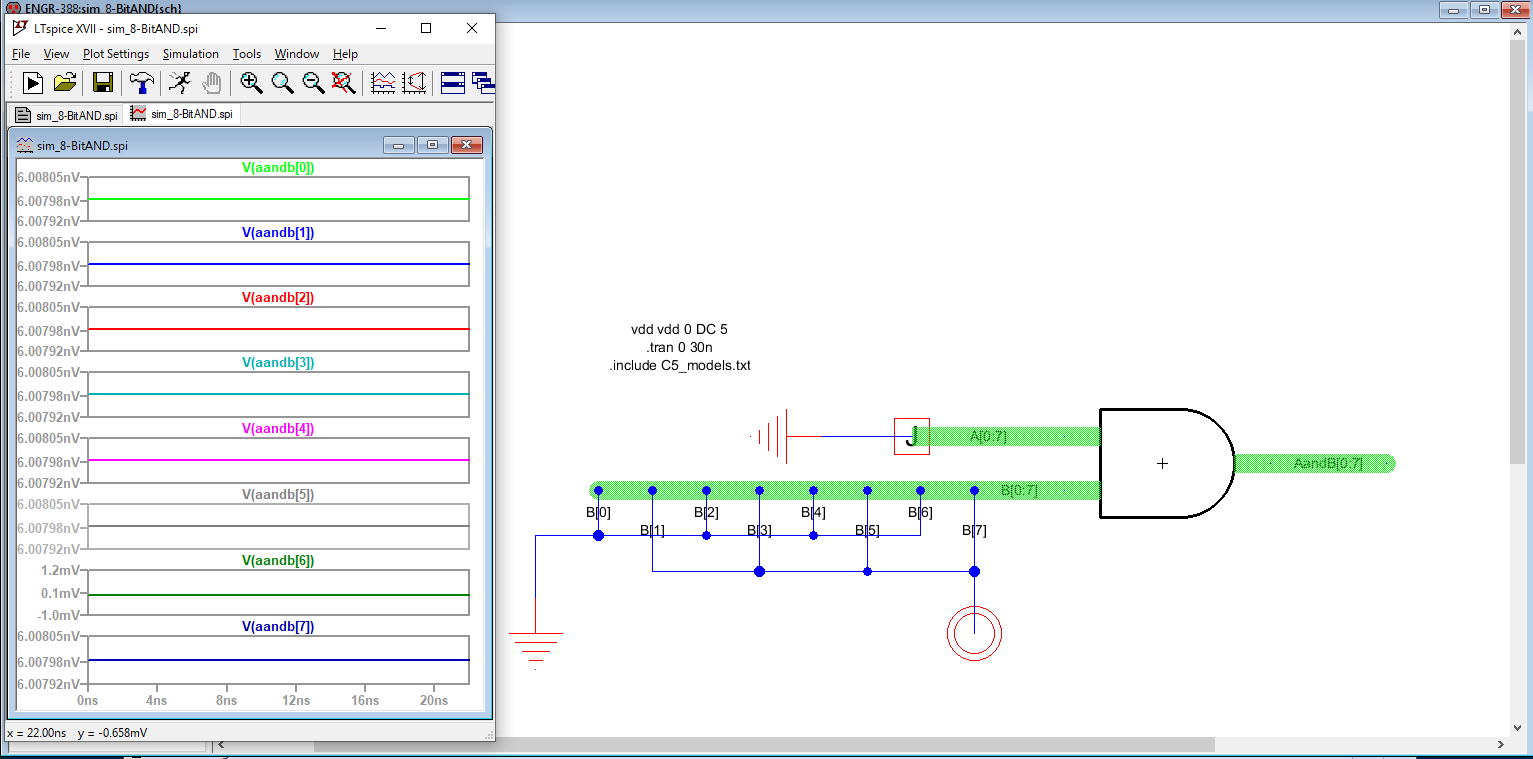

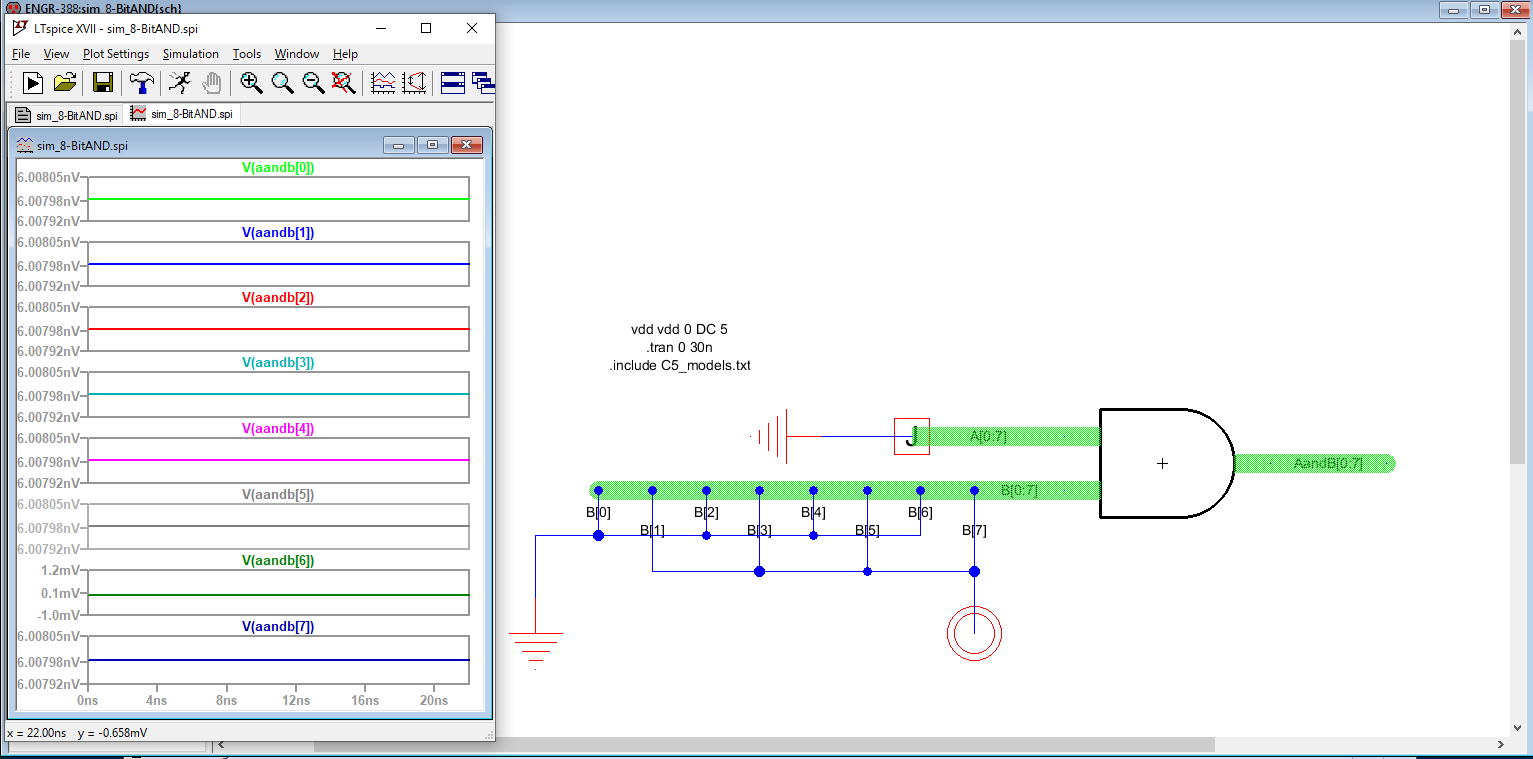

Figure 5: 8-Bit AND Voltage Source.

Figure 6: 8-Bit AND GND.

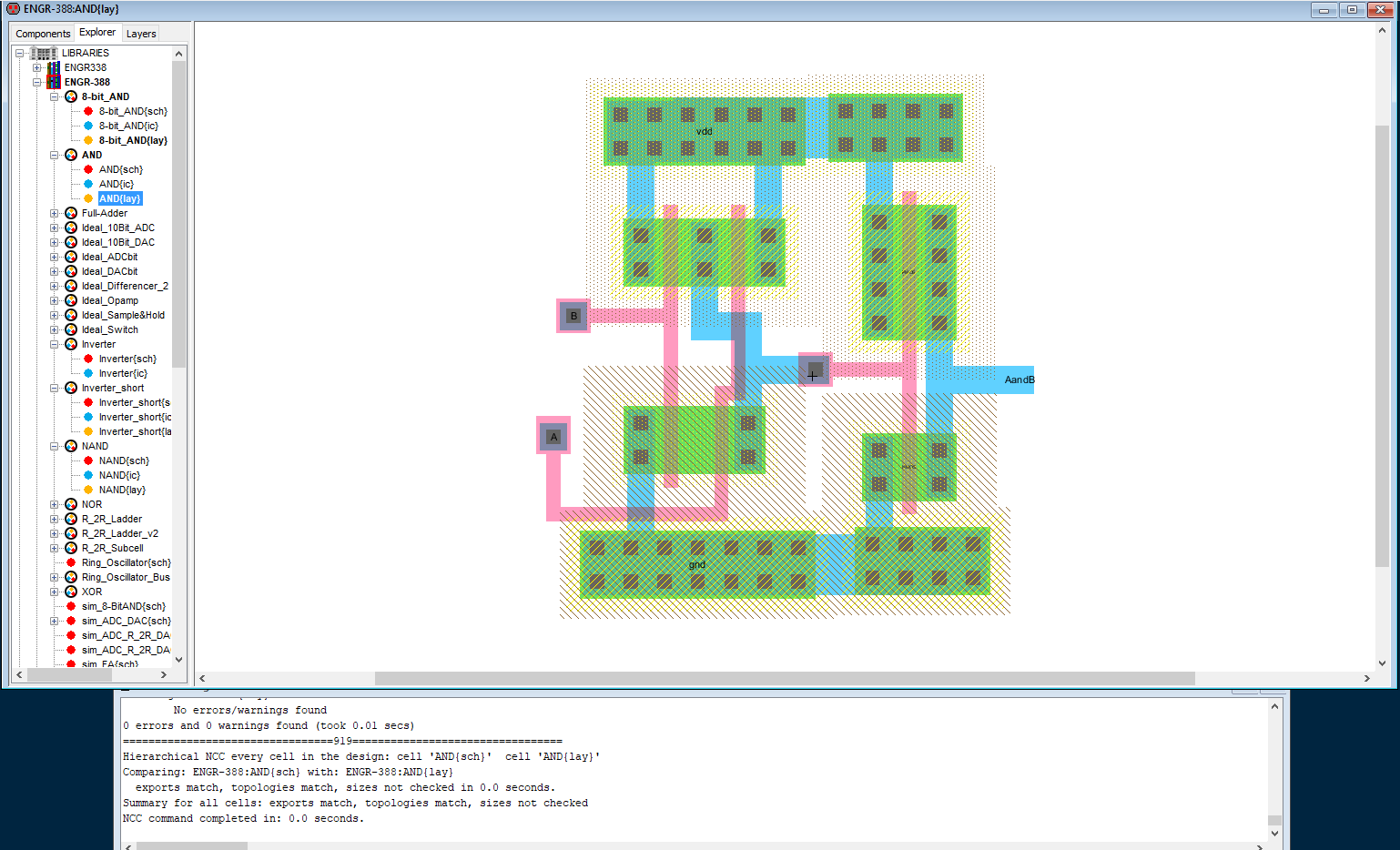

Figure 7: AND Layout.

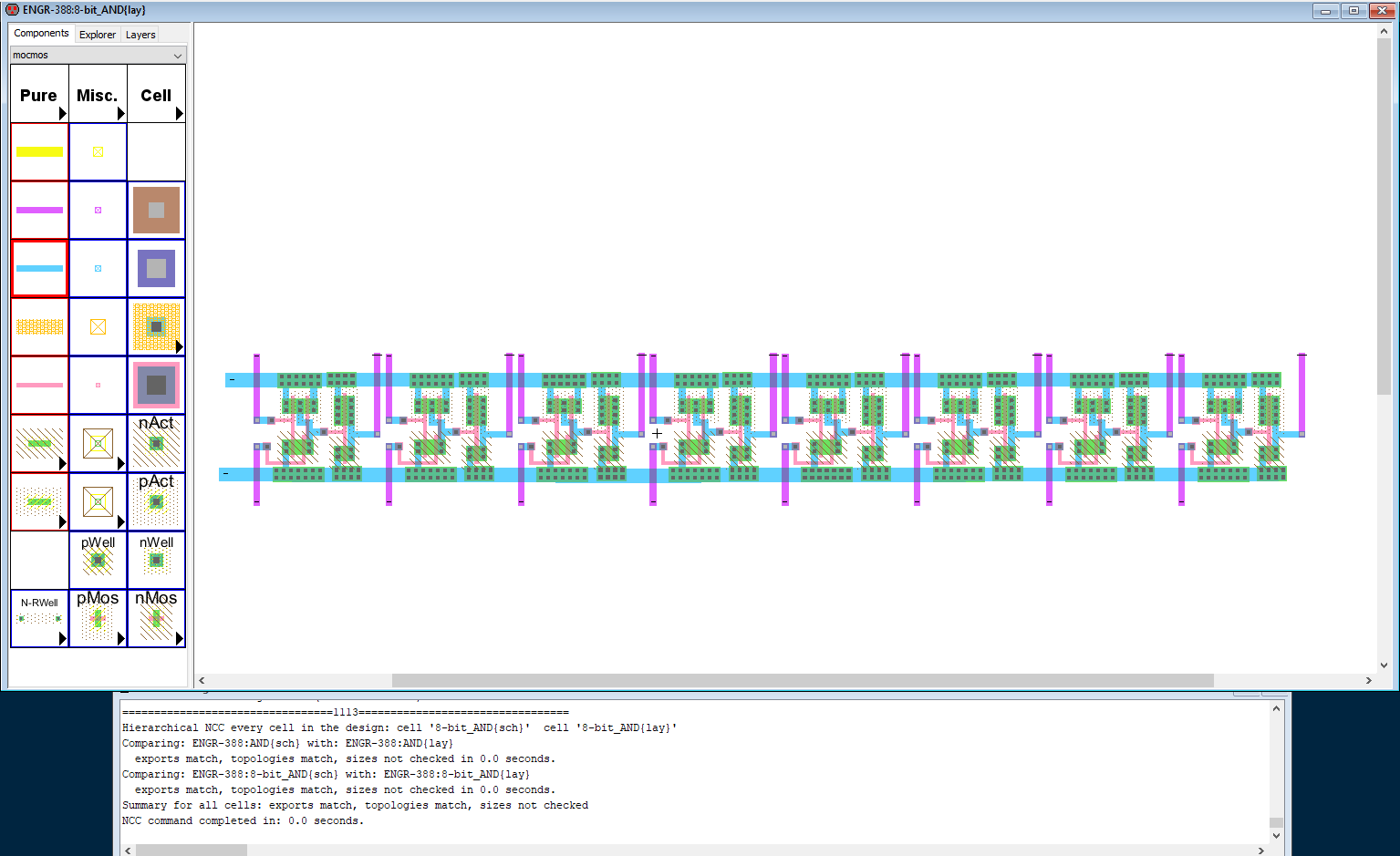

Figure 8: 8-Bit And Layout.

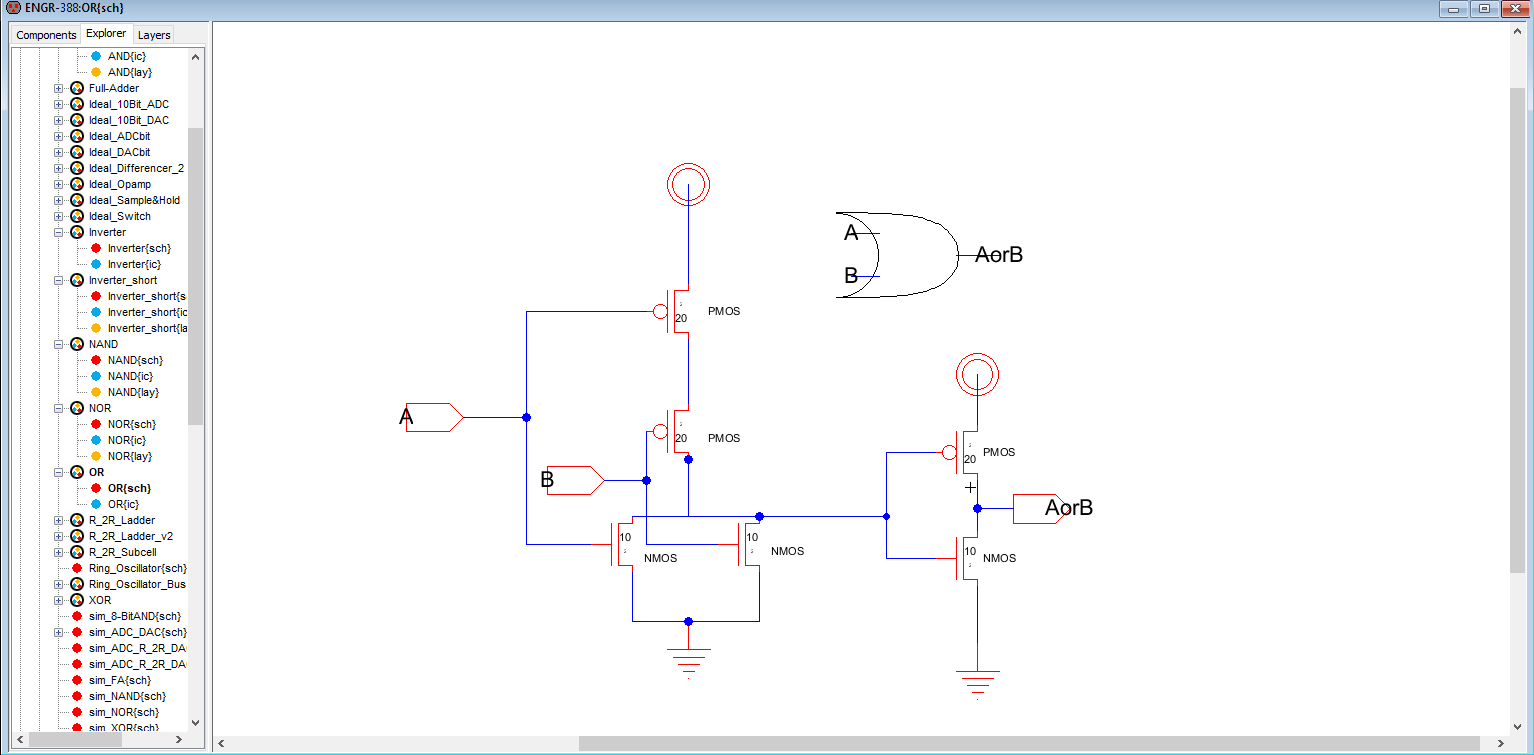

Task 3: 8-bit OR gate

Figure 9: OR Schematic.

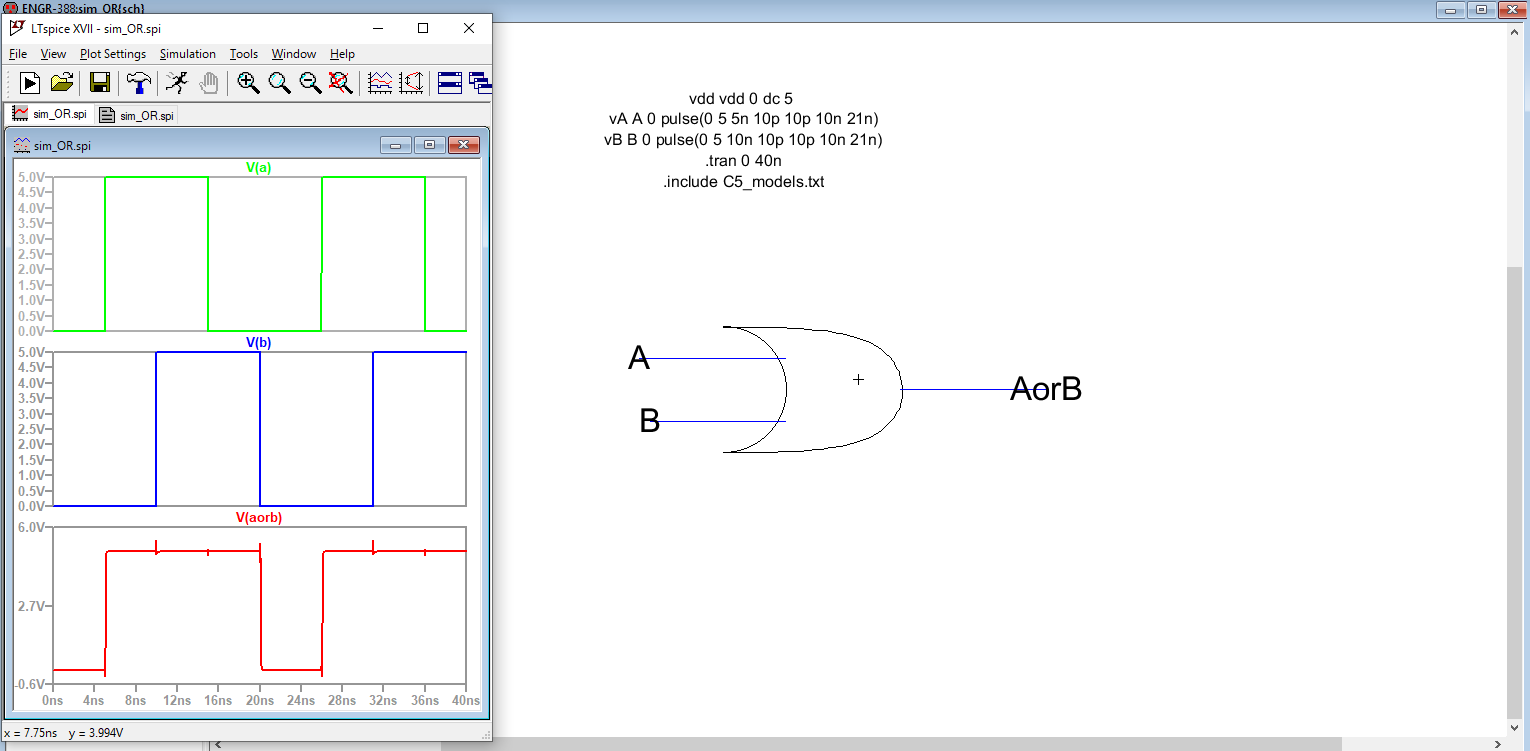

Figure 10: OR Spice Simulation.

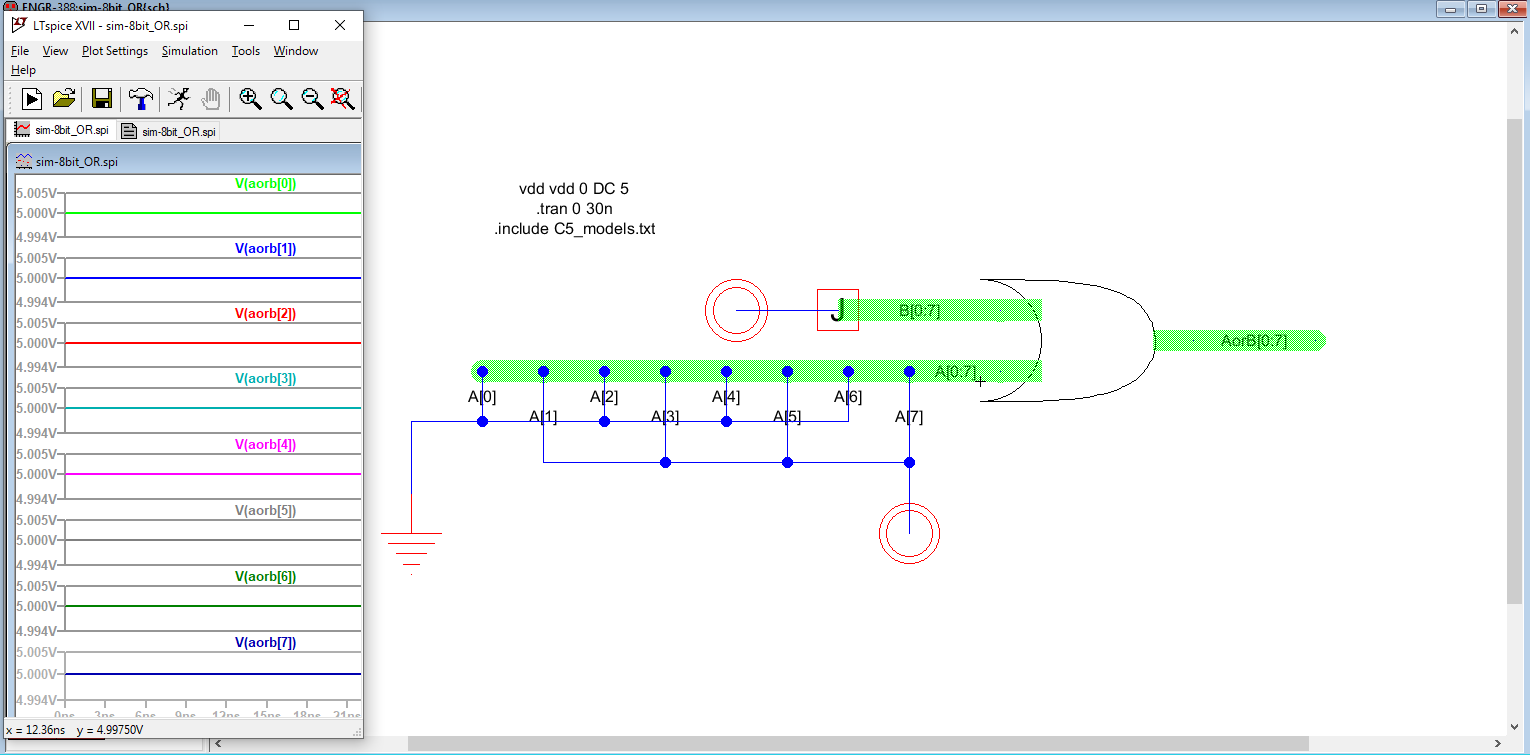

Figure 11: OR 8Bit Voltage Source.

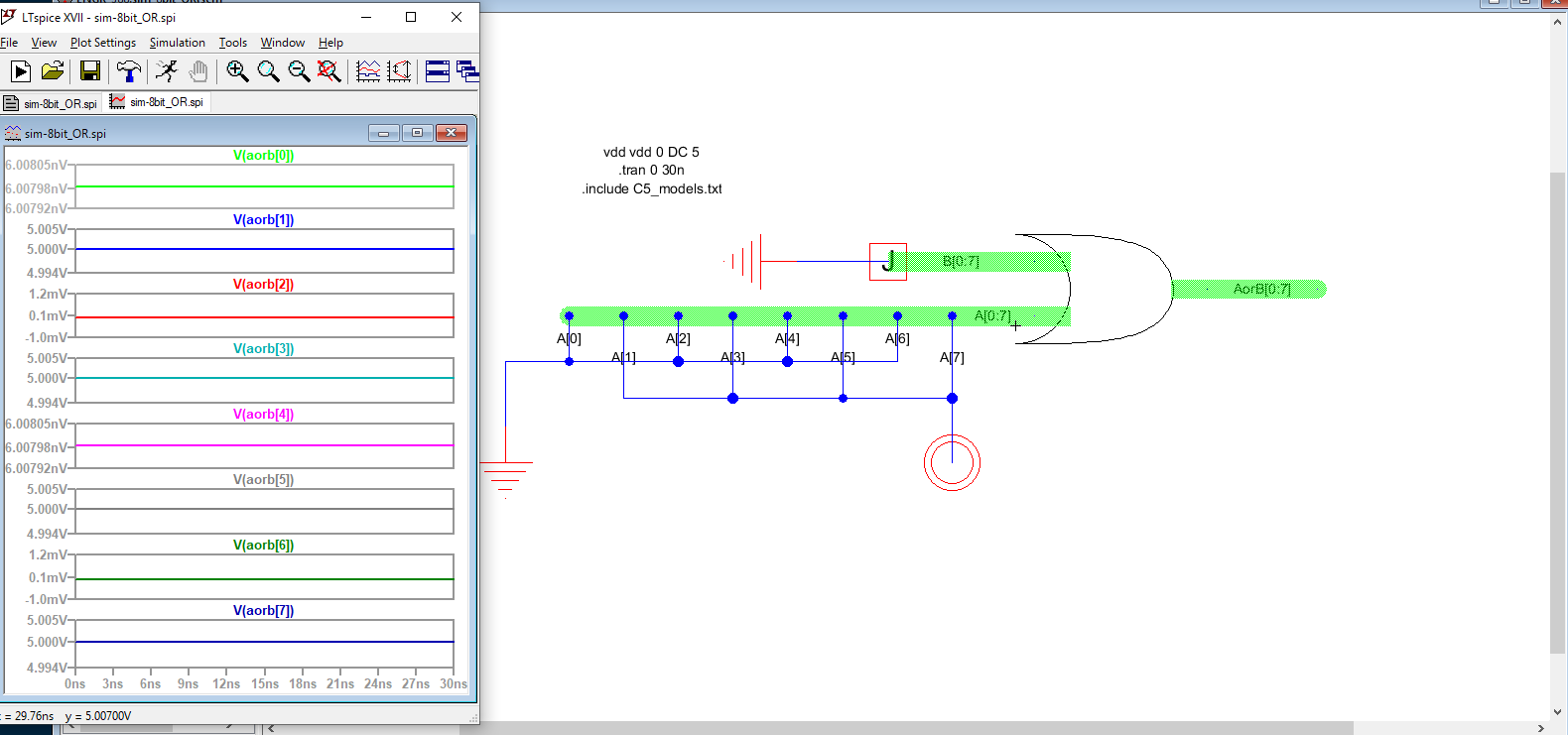

Figure 12: OR 8-Bit GND.

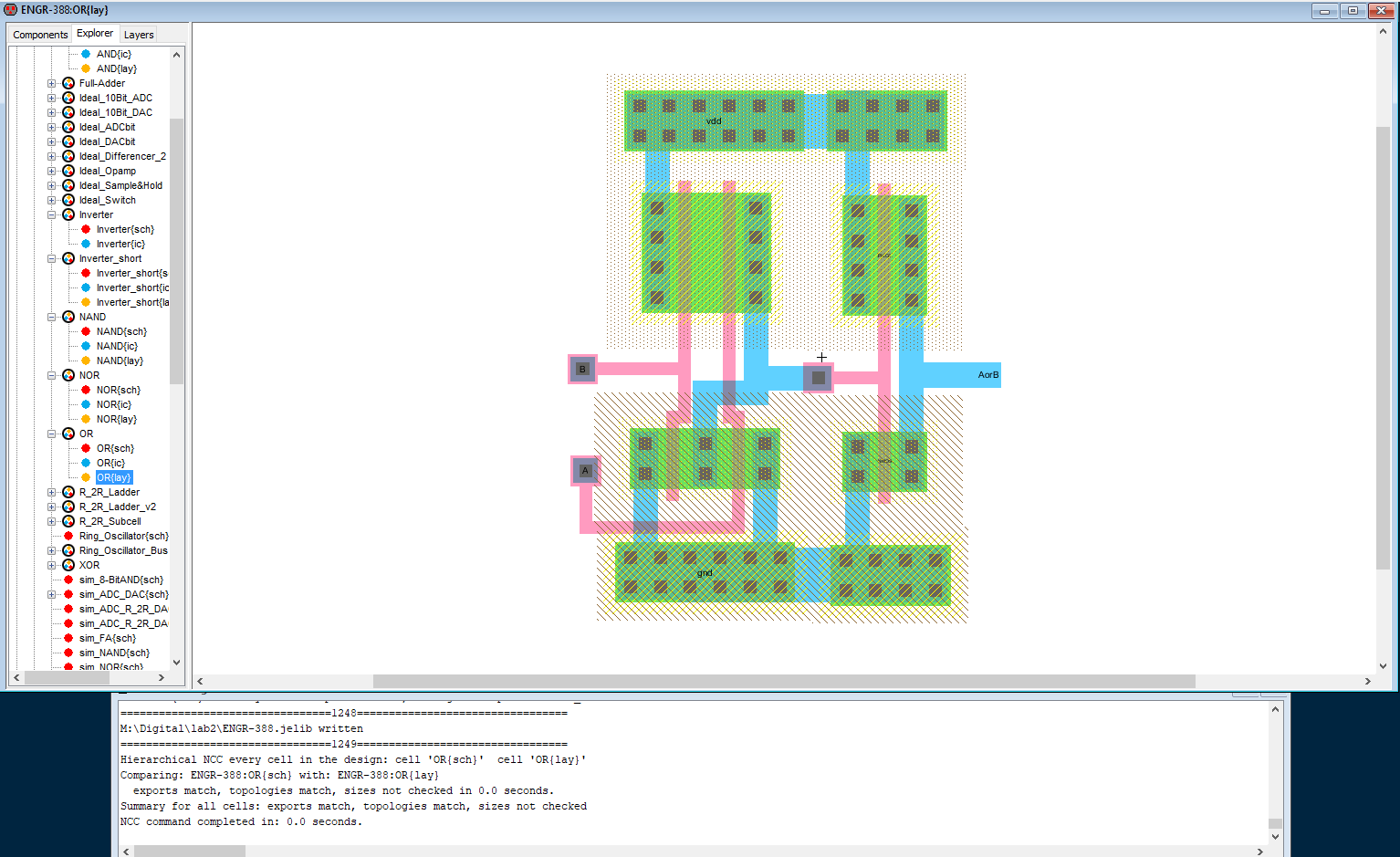

Figure 13: OR Layout.

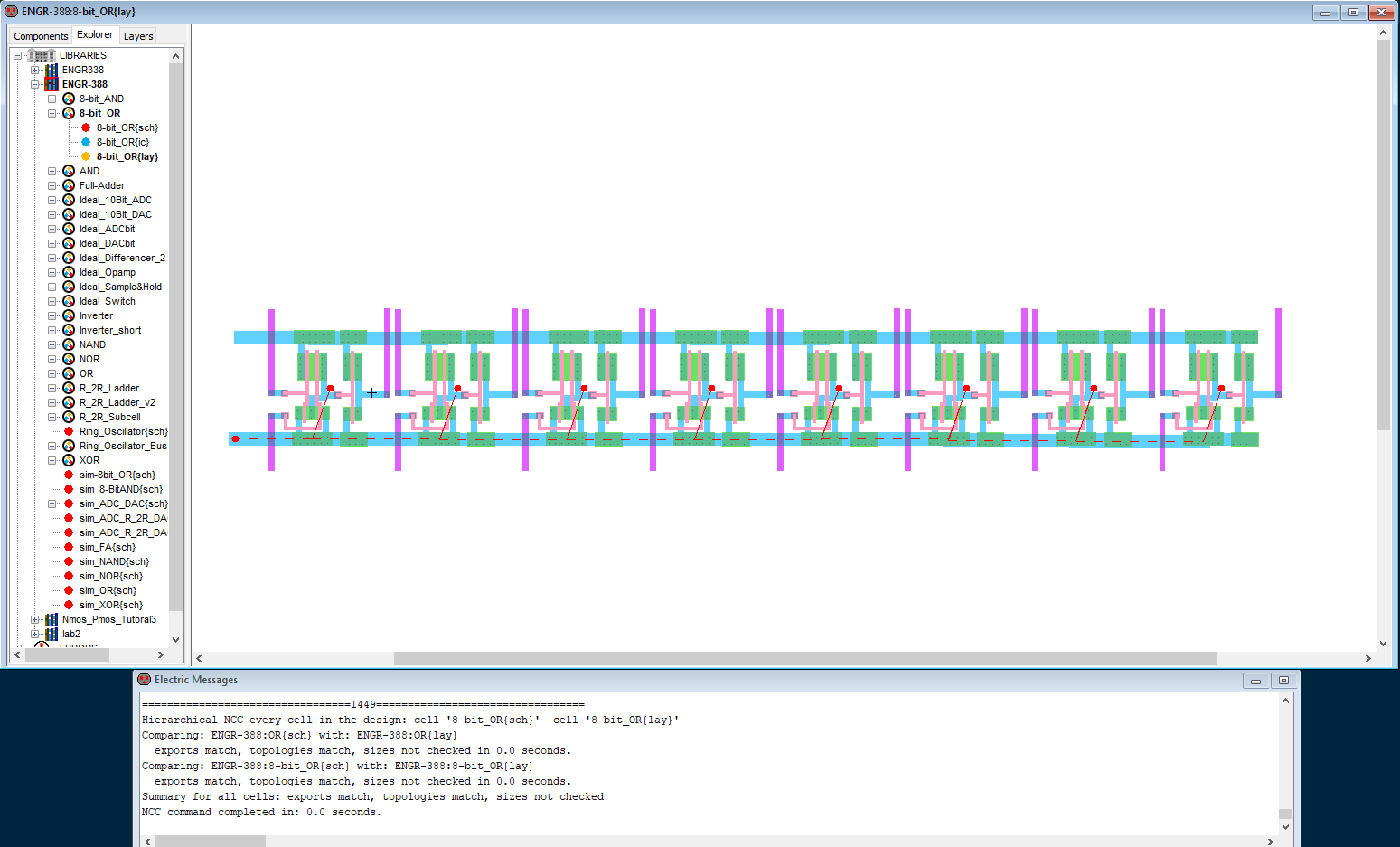

Figure 14: OR 8Bit Layout.

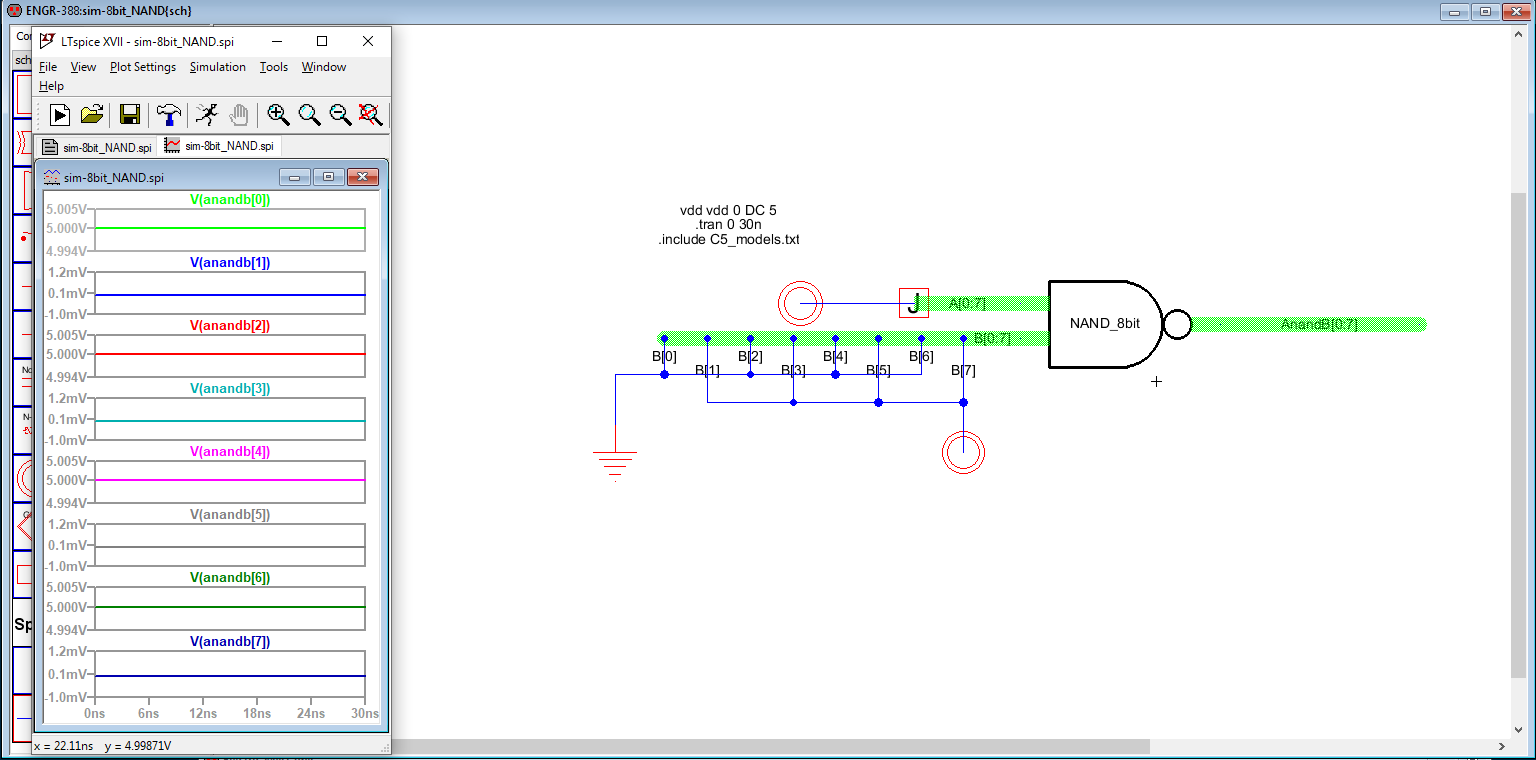

Figure 15: NAND 8-Bit Voltage.

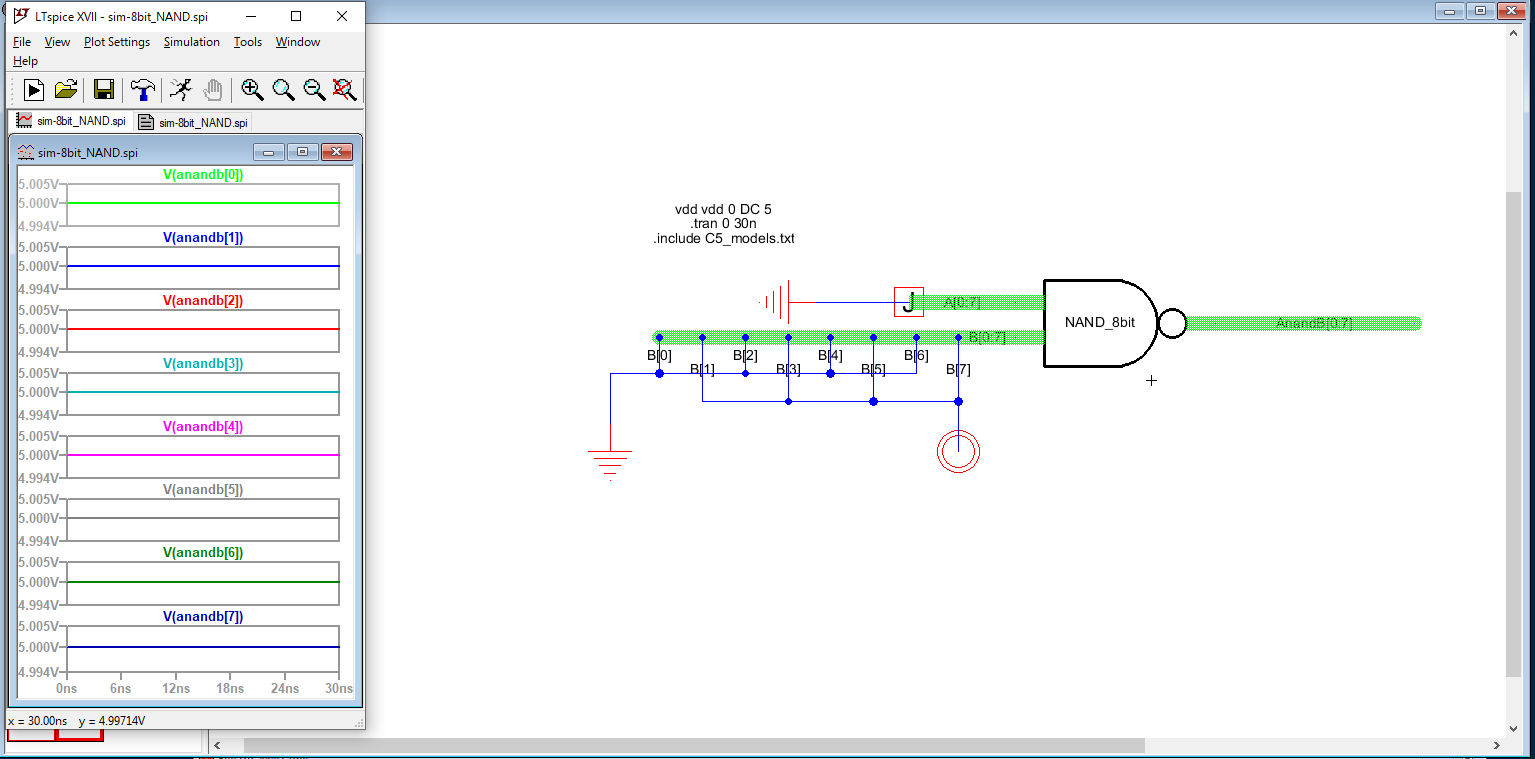

Figure 16: NAND 8-Bit GND.

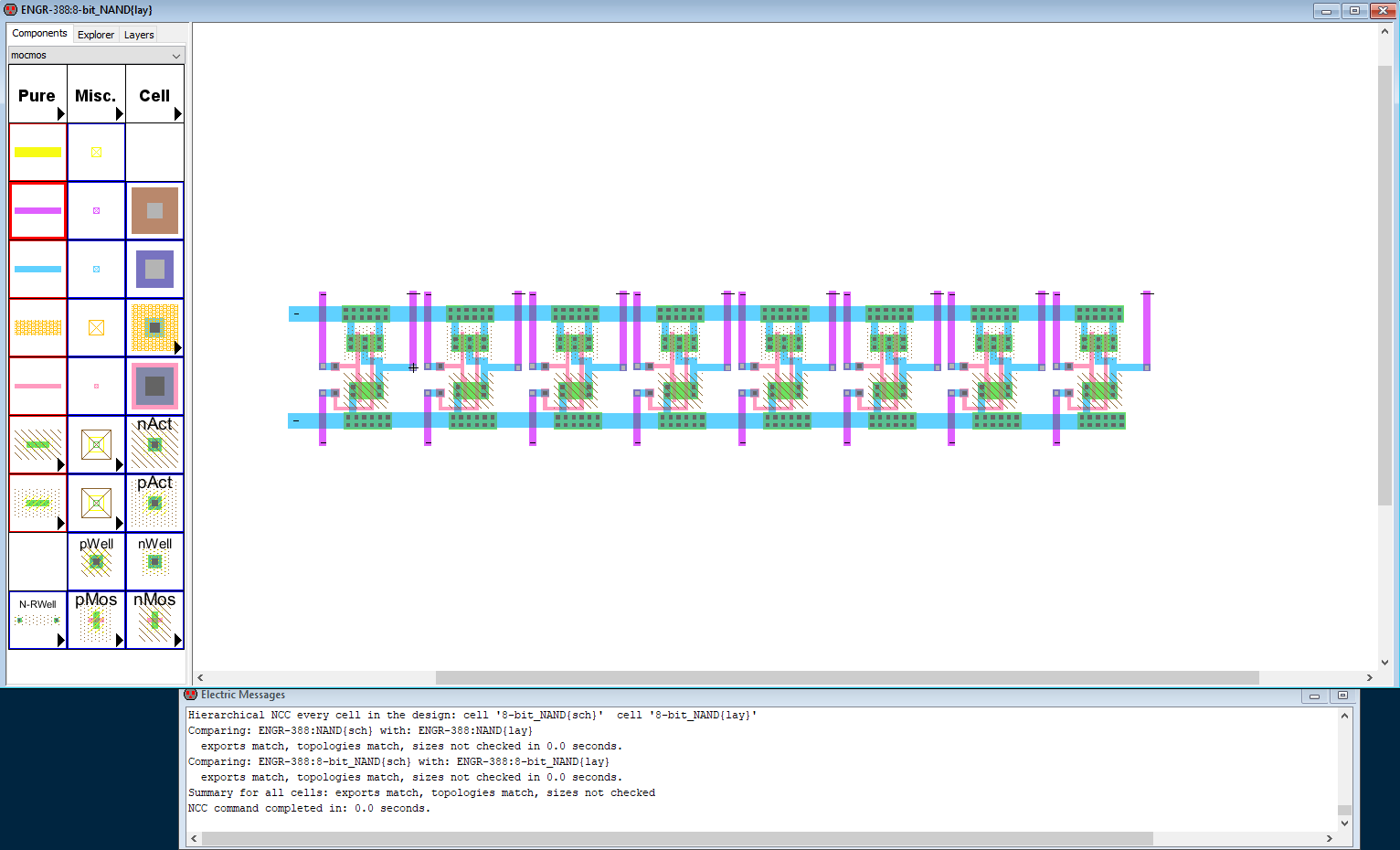

Figure 17: NAND 8-Bit Layout.

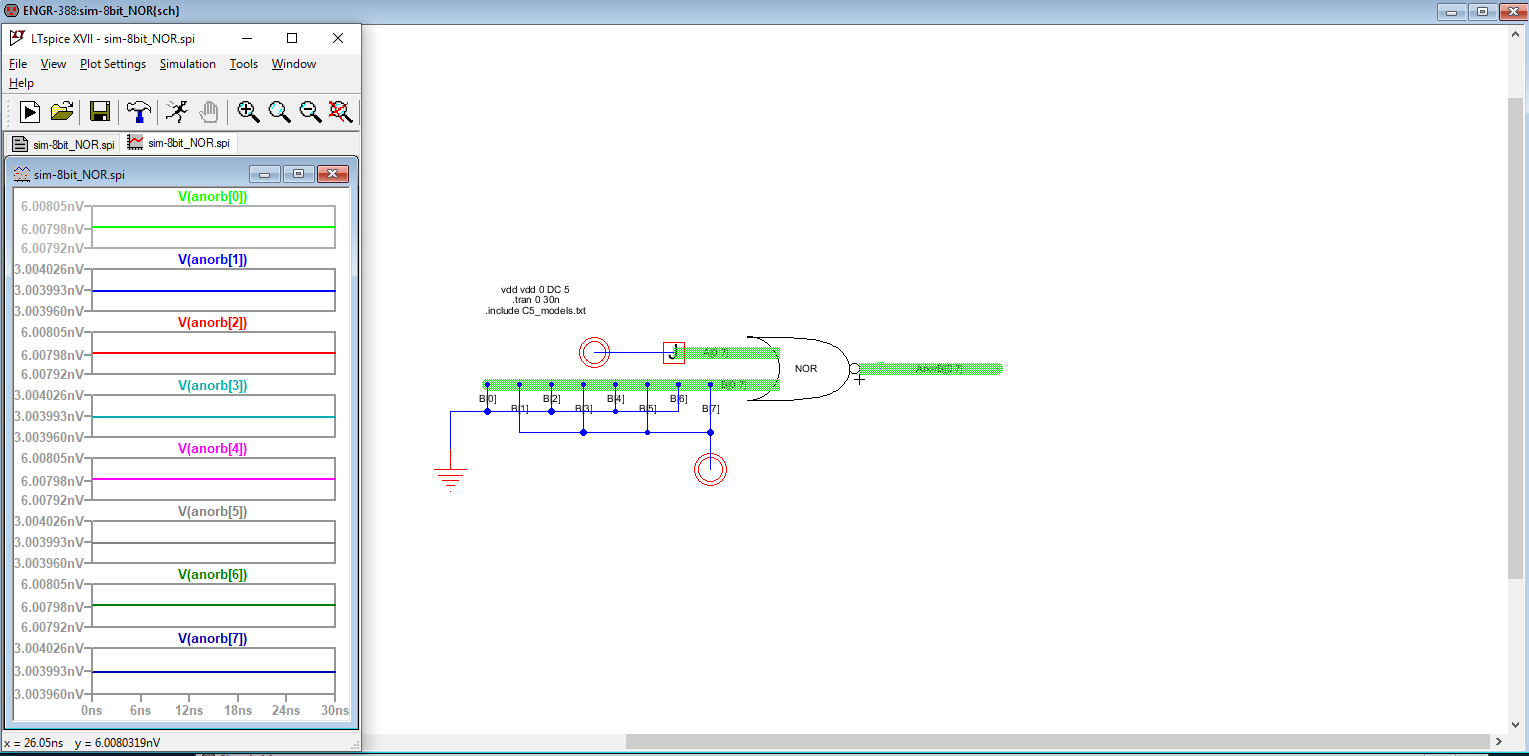

Figure 18: NOR 8-Bit Voltage.

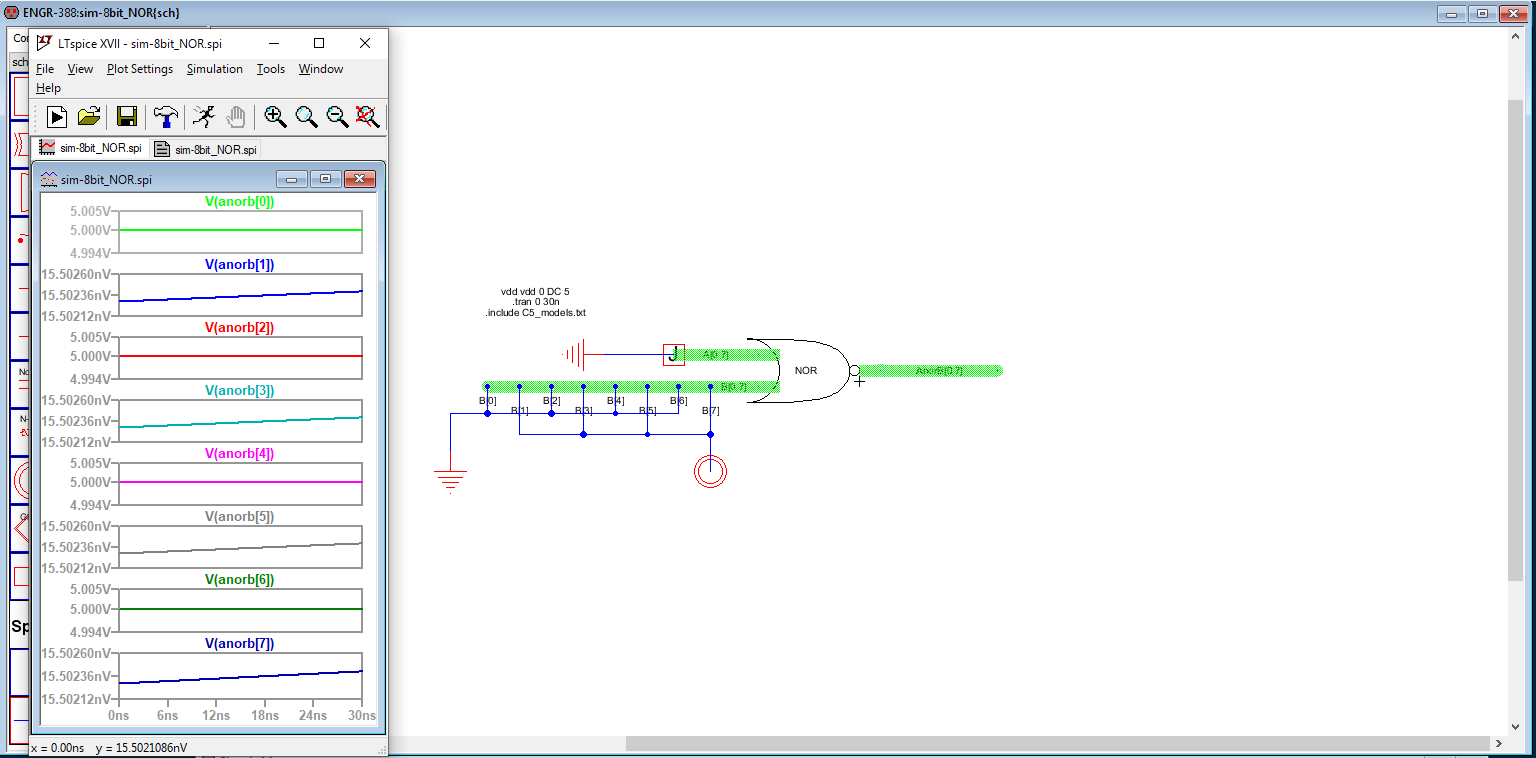

Figure 19: NOR 8-Bit GND.

Task5_NOR-8Bit-Schematic.pngTask5_NOR-8Bit-Schematic.png

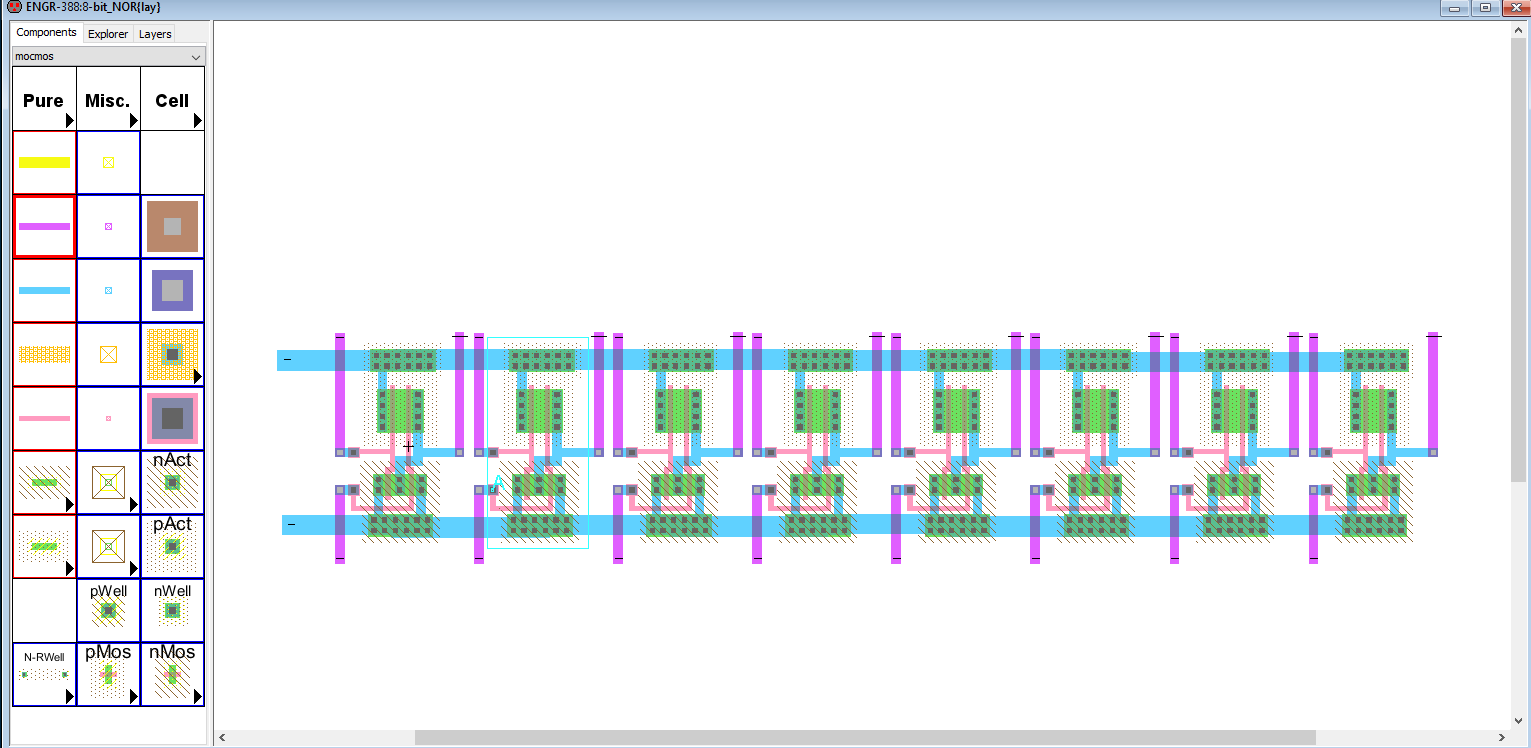

Figure 20: NOR 8-Bit Layout.