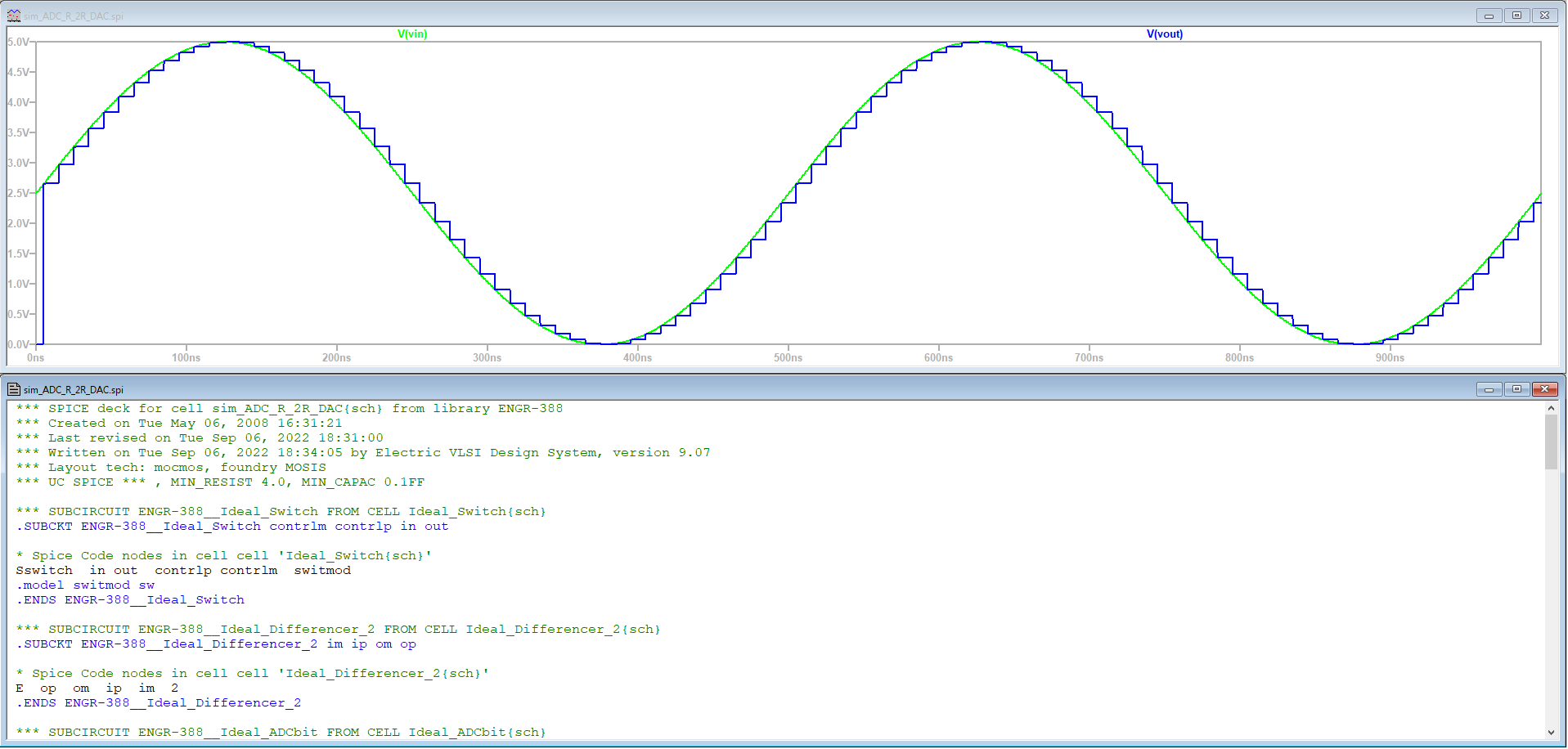

Figure 1: Ideal output for a 10-bit DAC; Simulated using Electric VLSI and LTSpice integrated circuit design.

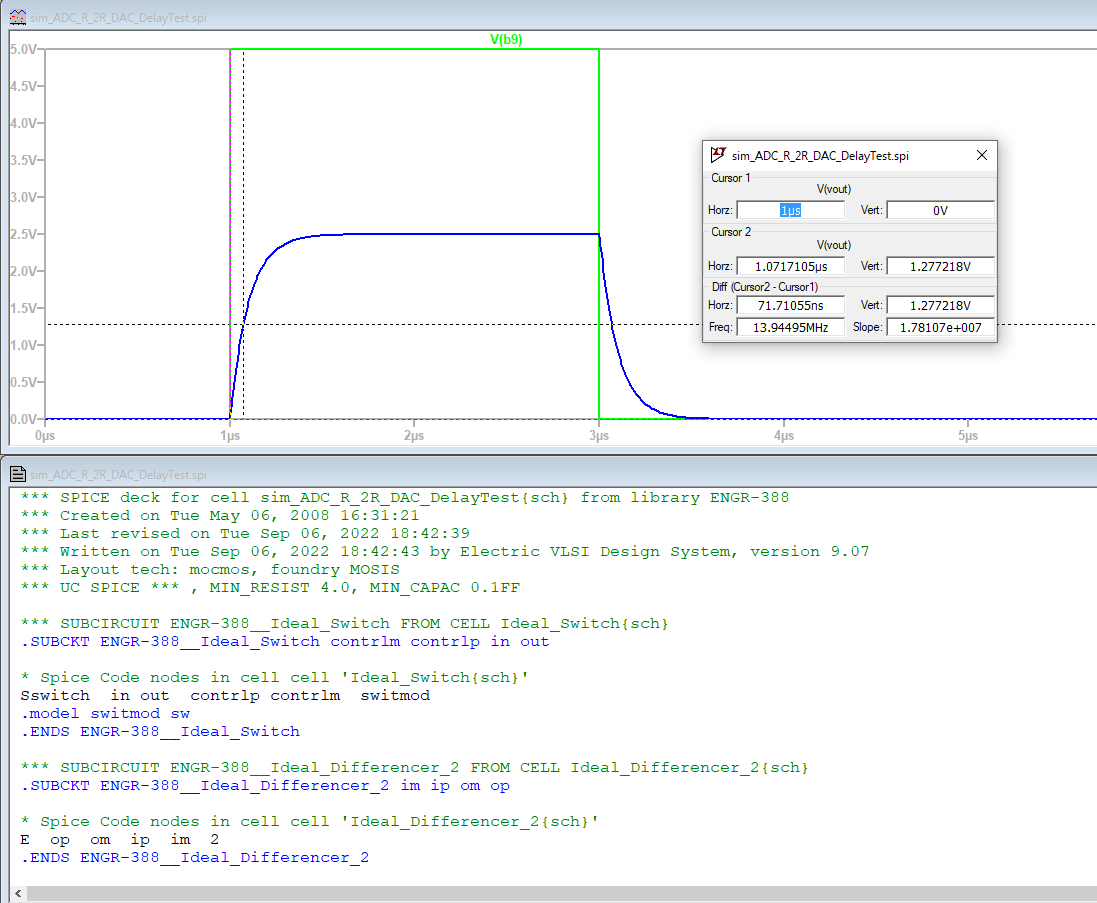

Figure 2: Constructed R-2R DAC ouput; Simulated using Electric VLSI and LTSpice integrated circuit design.

Figure 3: Time delay from B9 pin when the DAC drives a 10pF load; Simulated using Electric VLSI and LTSpice integrated circuit design.

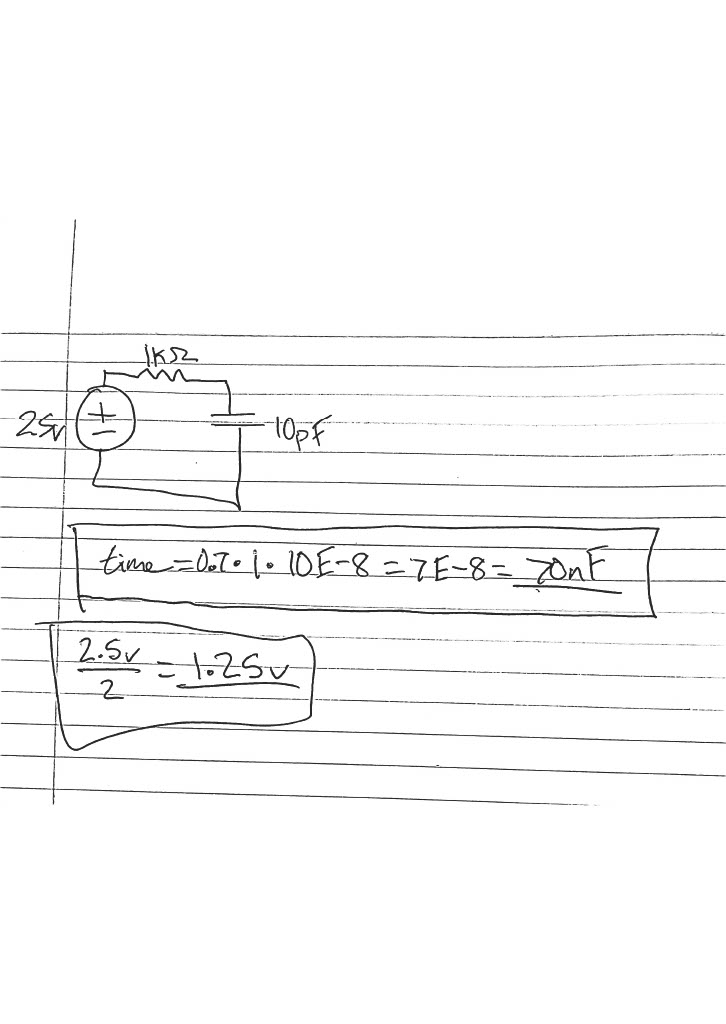

Figure 4: Hand calculations for the how long it takes the capacitor to charge half way; Thevenin's Cirucit.

The calculation for how long it would take the capacitor to charge half way matched with the simulation resutls.