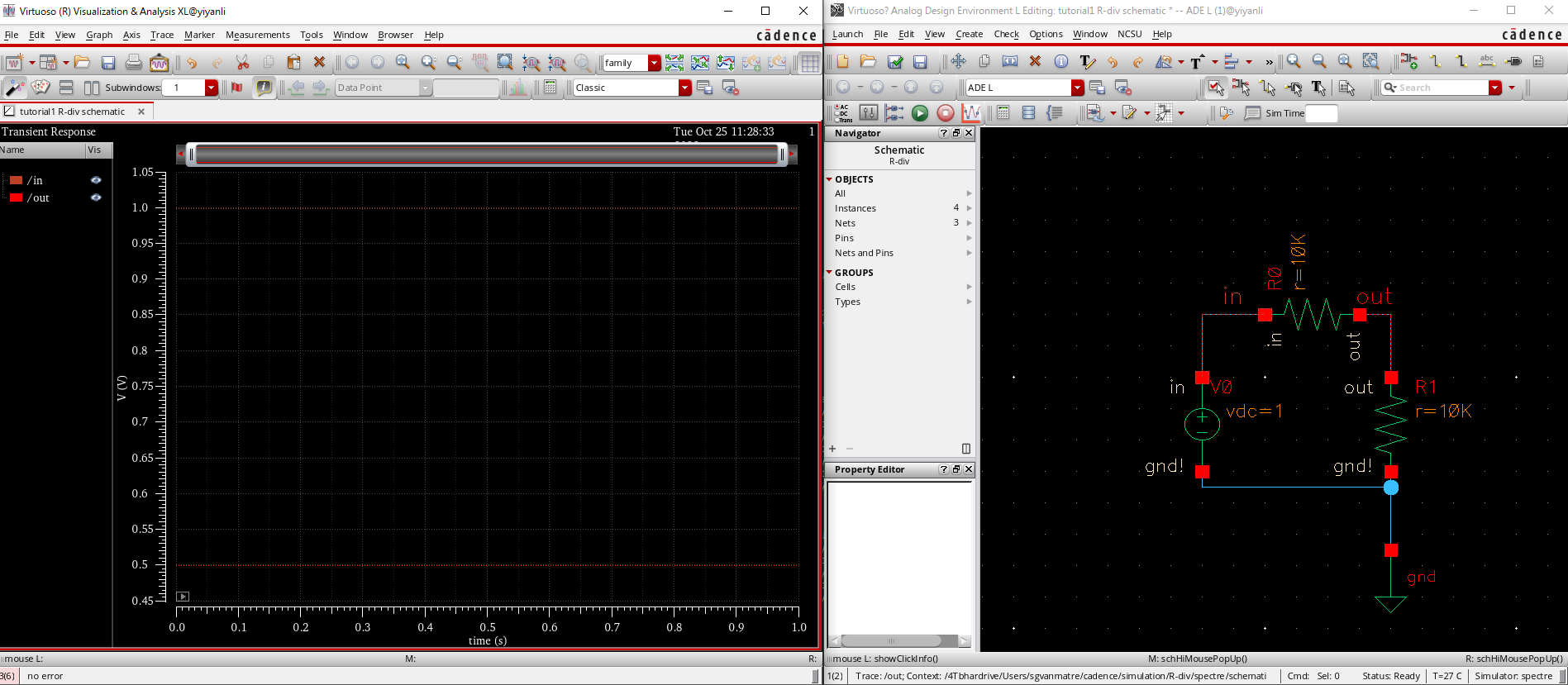

Figure 1: Simulated v-divider using 10k ohm resistor.

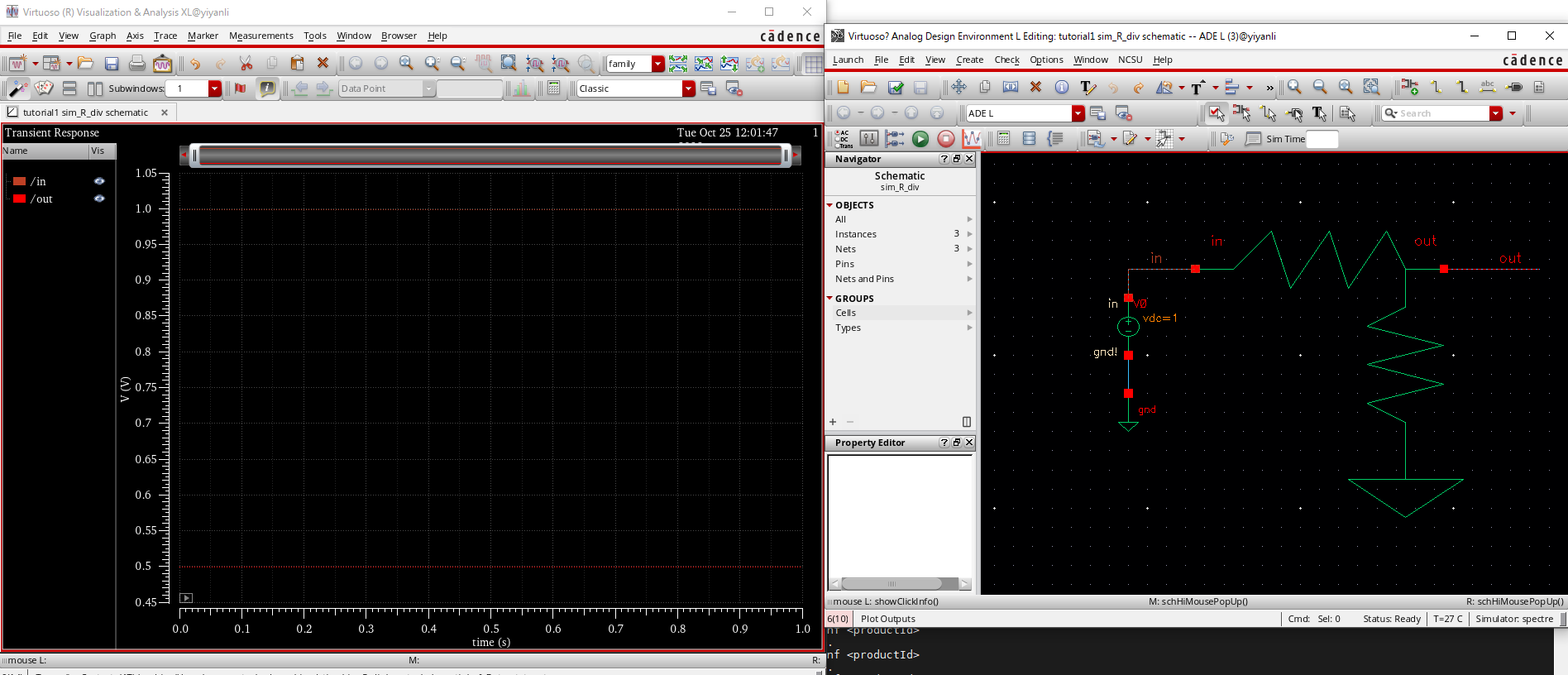

Figure 2: Simulated symbol for Figure 1.

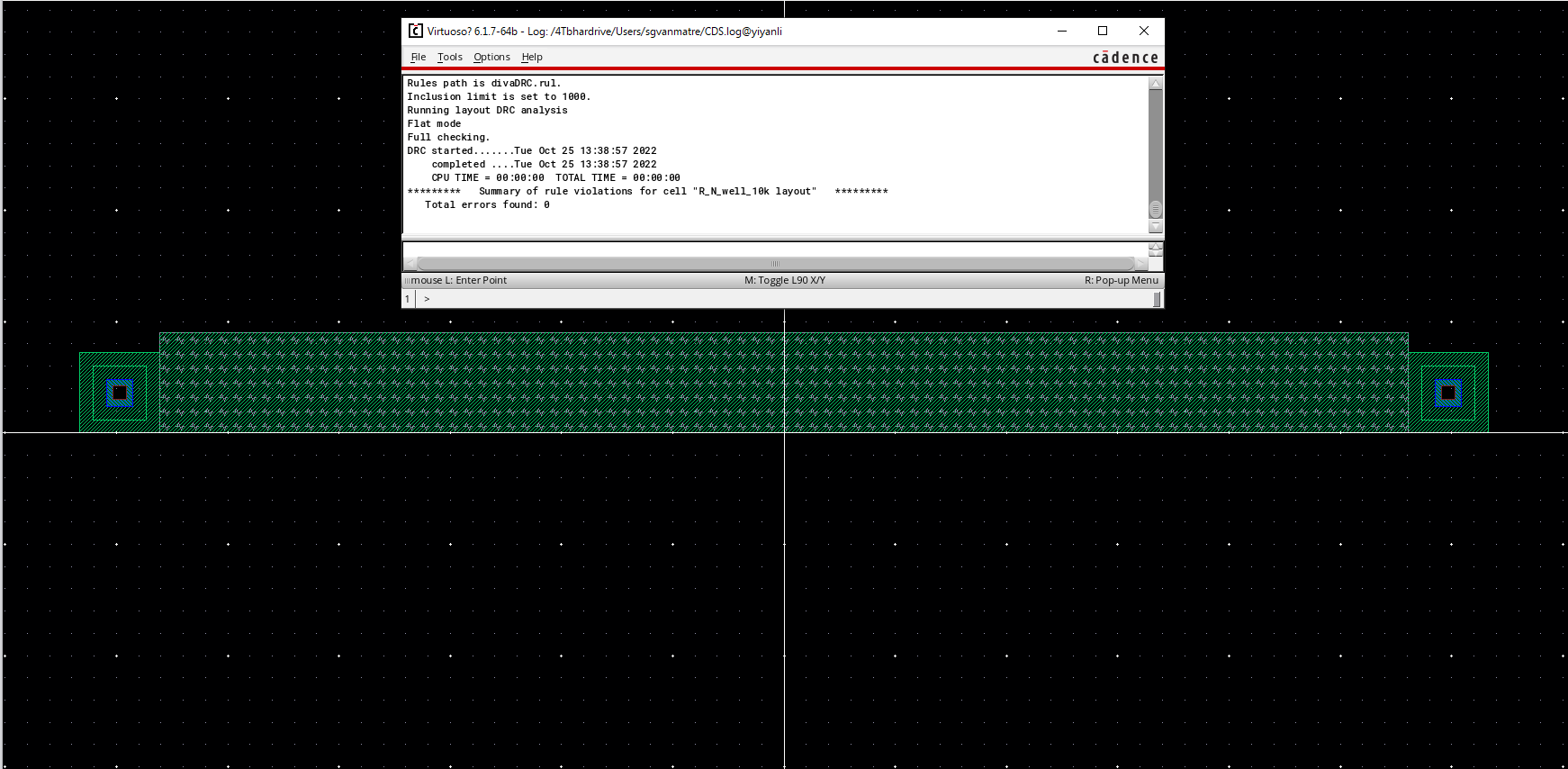

Figure 3: Nwell 10k ohm.

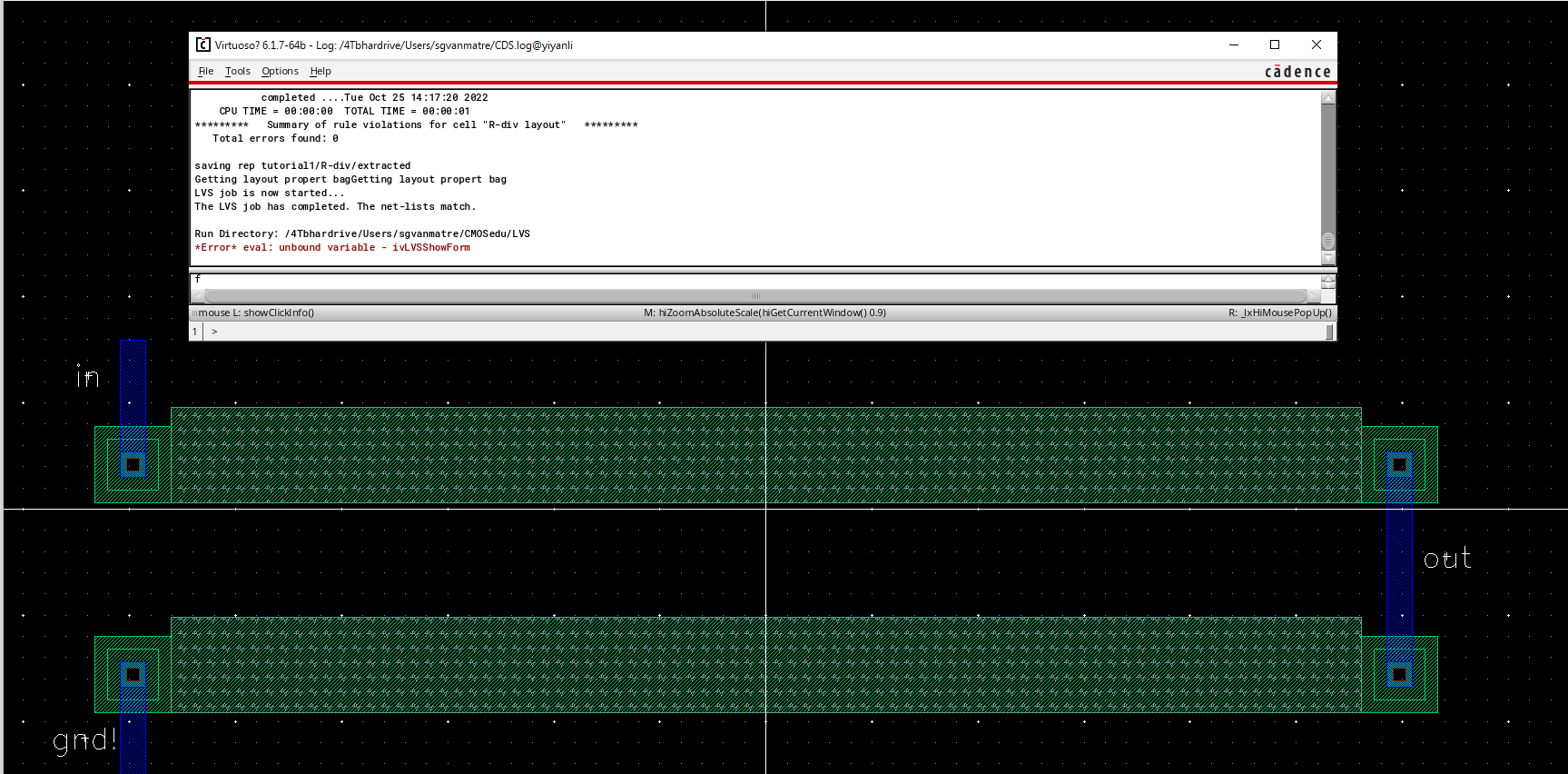

Figure 4: V-divider layout passing LRC.

Tutorial 2: NMOS and PMOS

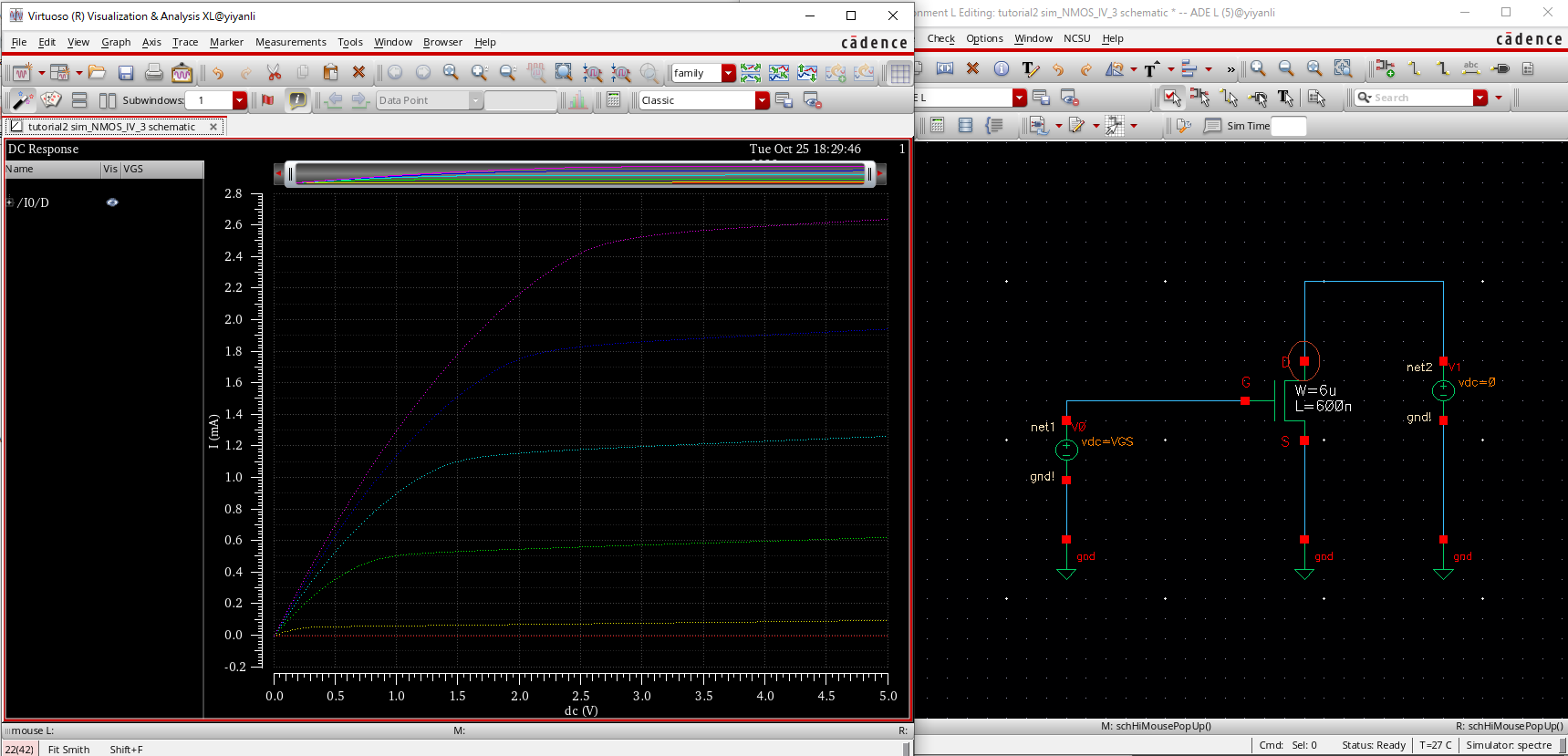

Figure 5: Simulated NMOS.

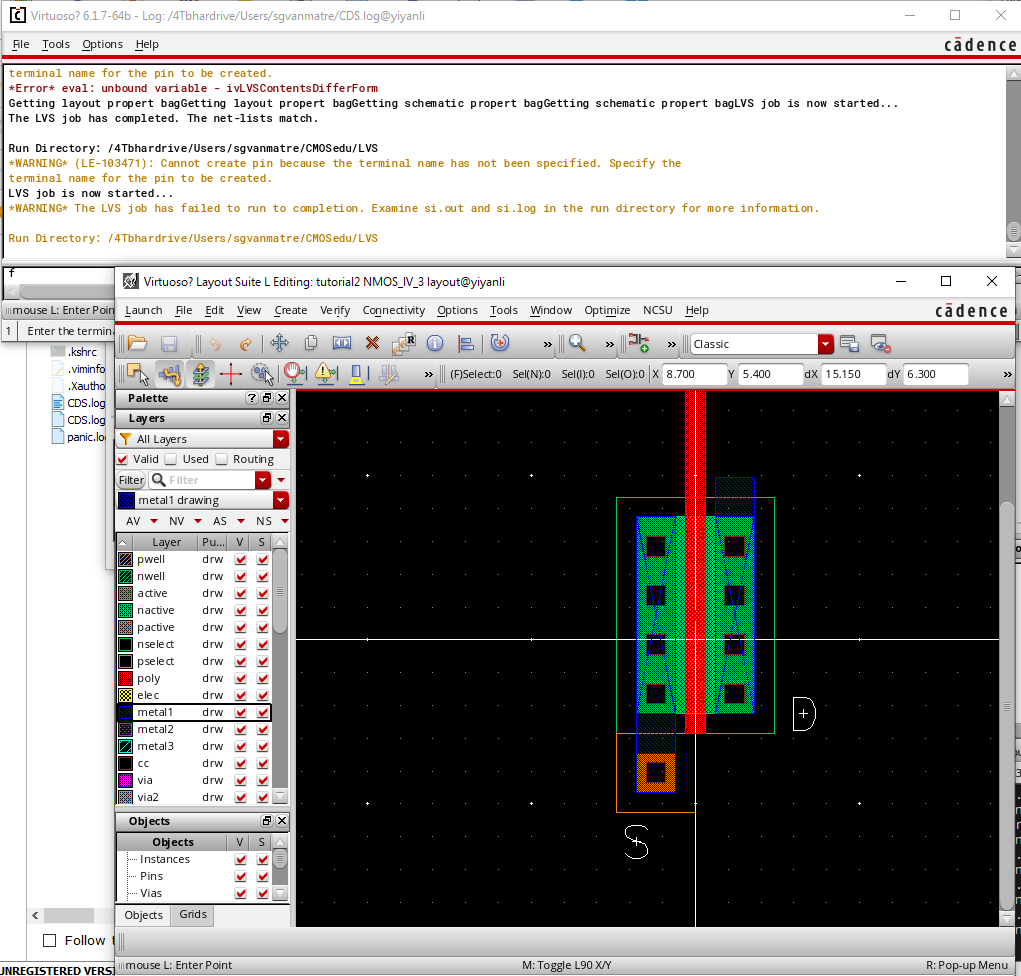

Figure 6: NMOS encountered error layout.

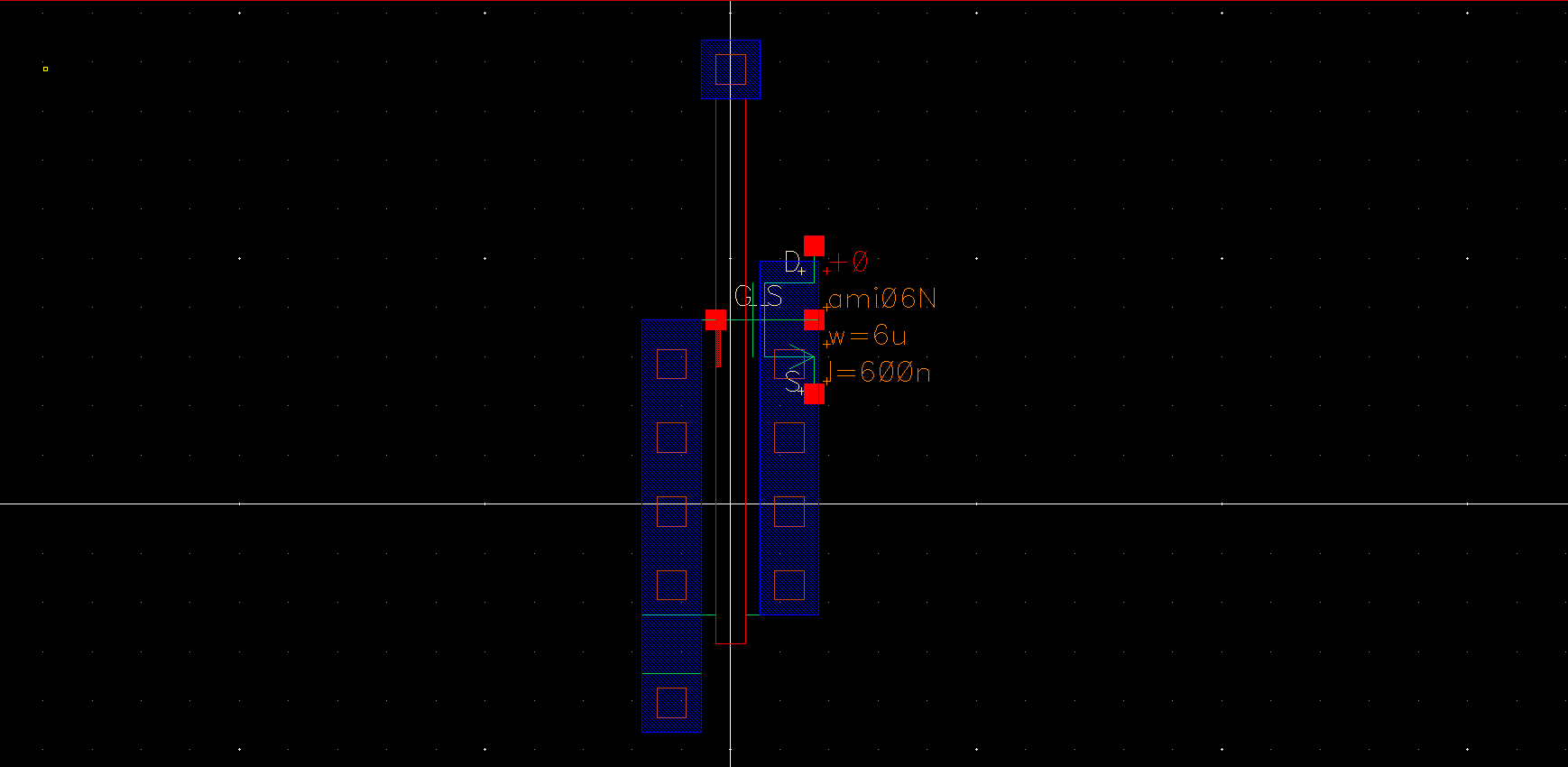

Figure 7: NMOS body pin.

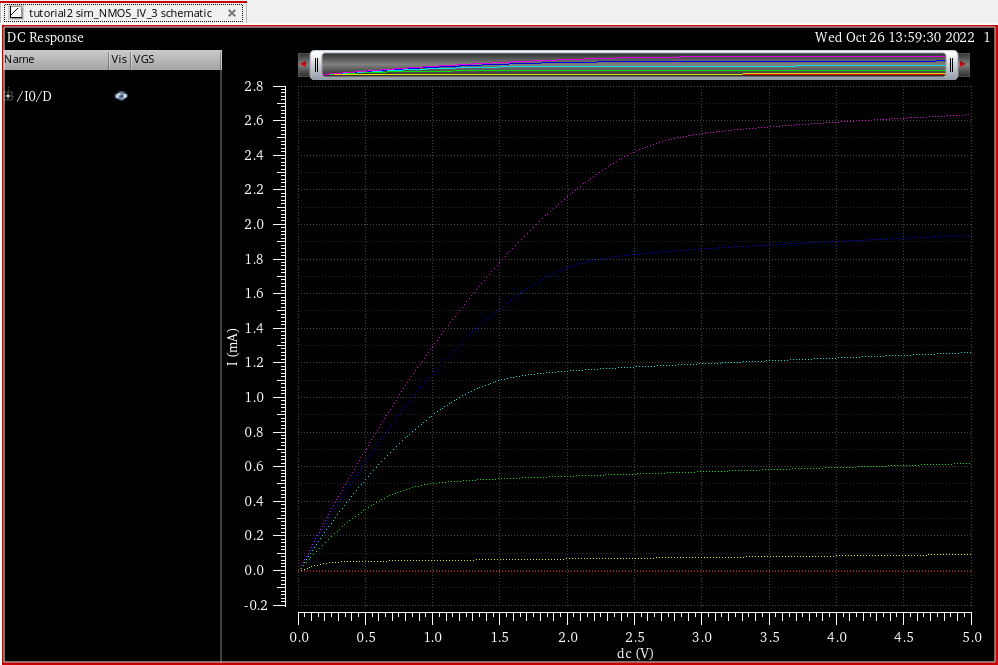

Figure 8: Extracted NMOS.

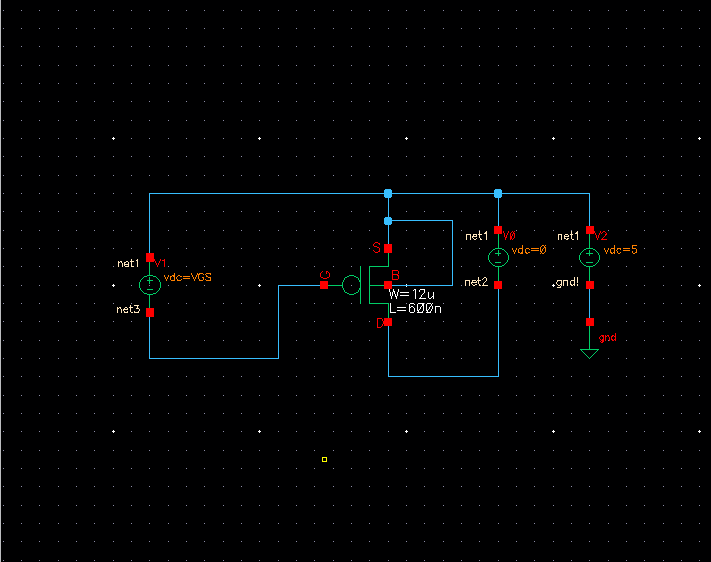

Figure 9: PMOS schematic.

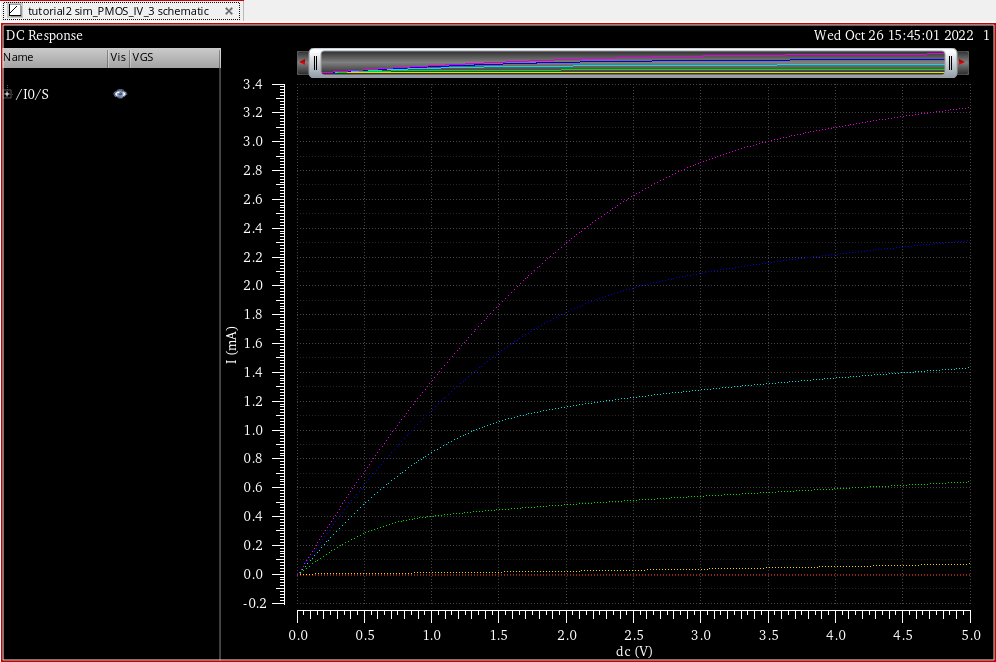

Figure 10: Simulated PMOS schematic.

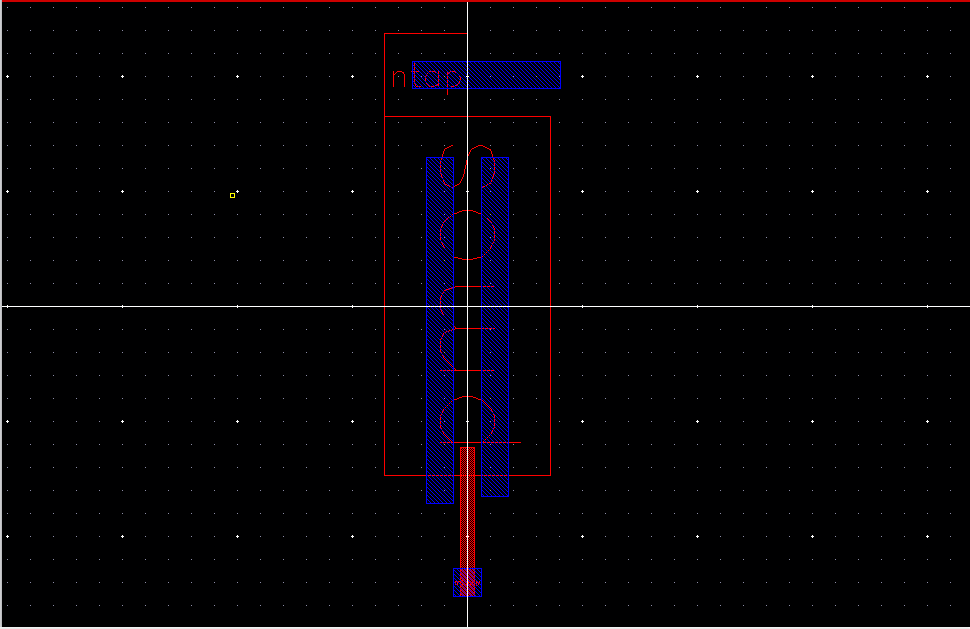

Figure 11: PMOS layout.

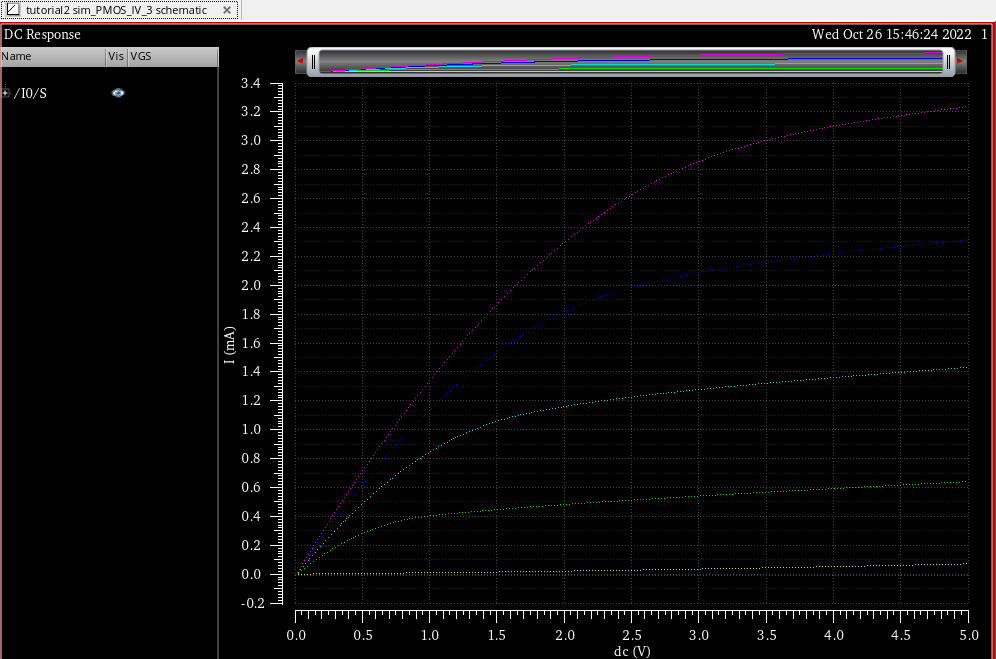

Figure 12: PMOS extracted layout simulated.