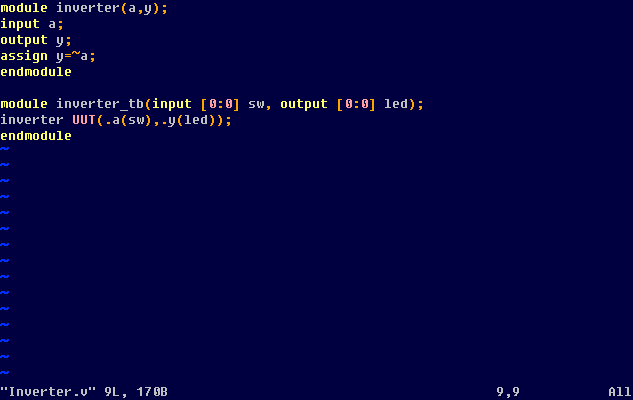

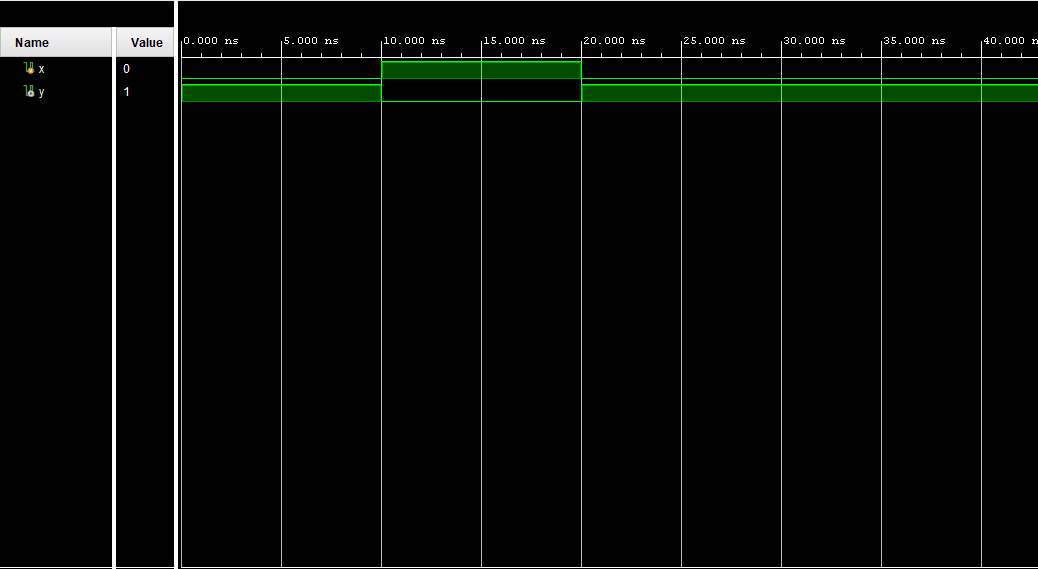

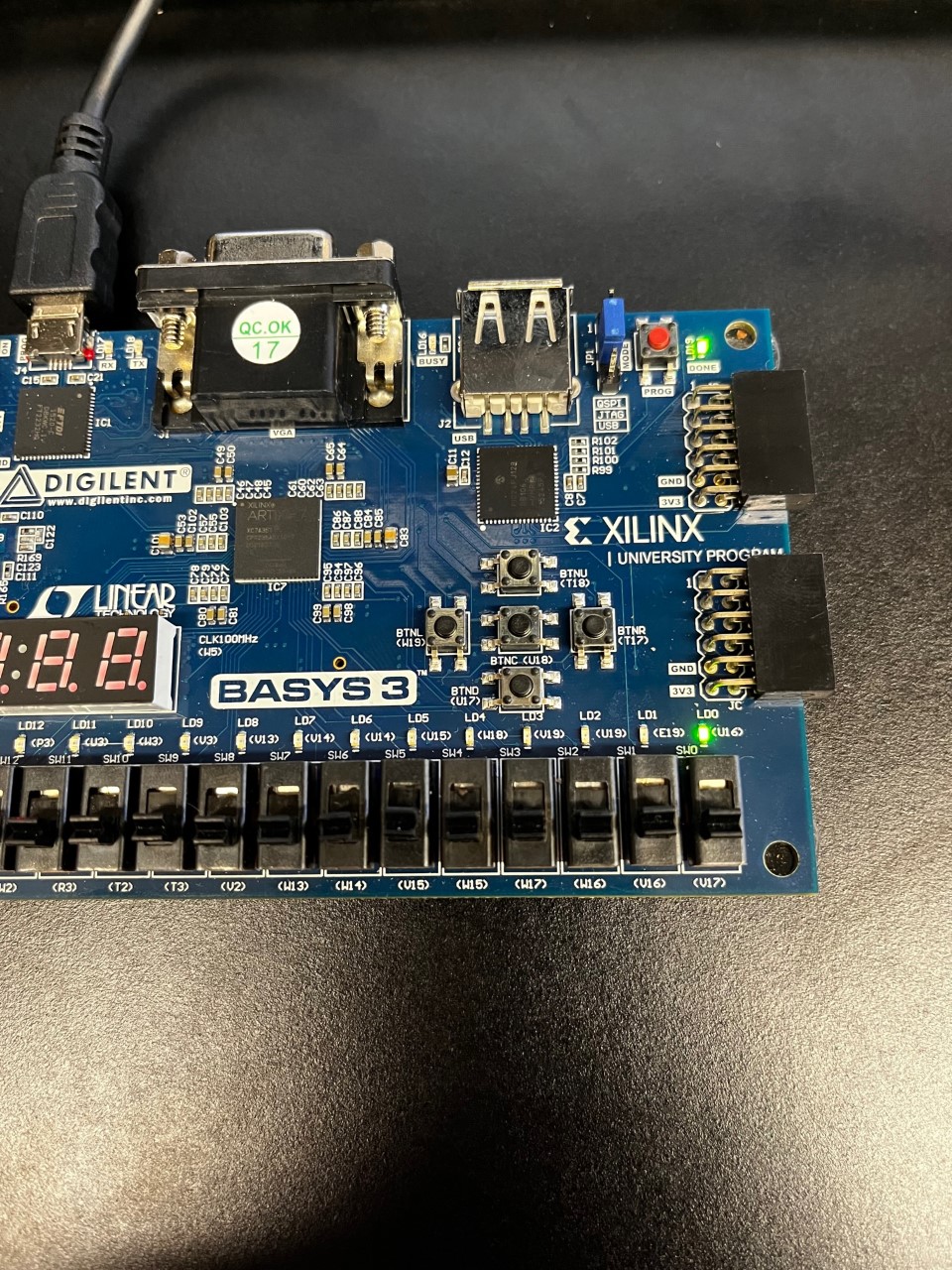

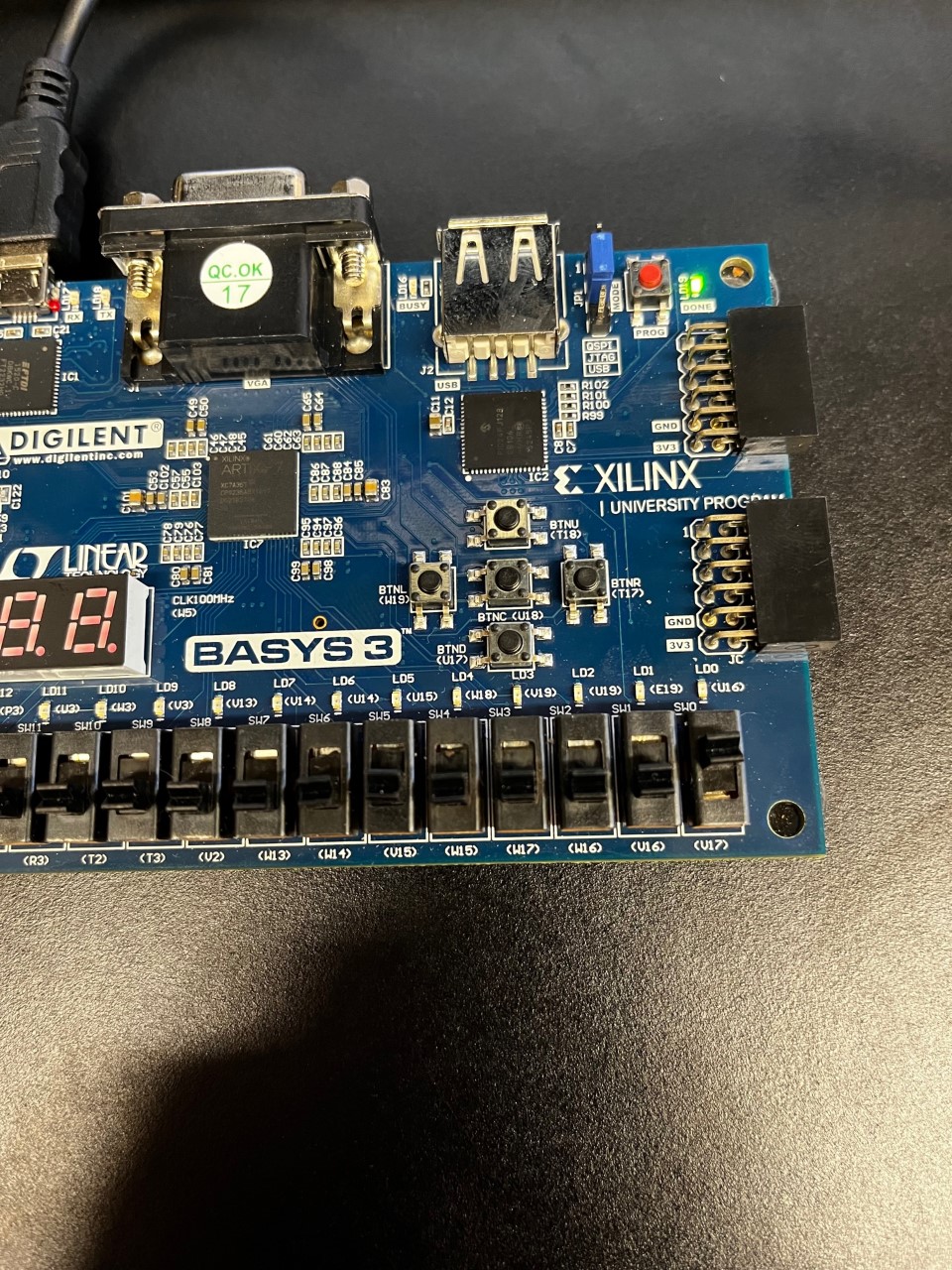

- Inverter

- 2-bit full adder

- 8-bit And

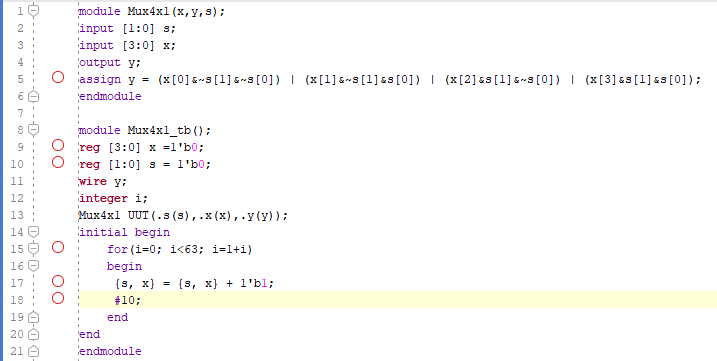

- 4-1 MUX

Figure 1: Inverter code.

Figure 1.1: Inverter simulation.

Figure 1.2: Inverter implemented ON output.

Figure 1.3: Inverter implemented OFF output

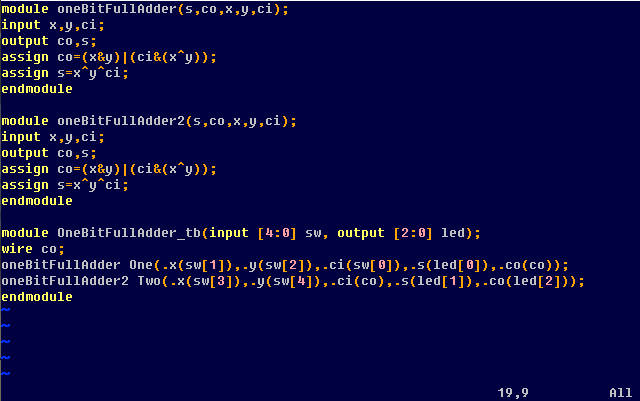

Figure 1.4: 2-bit full adder code.

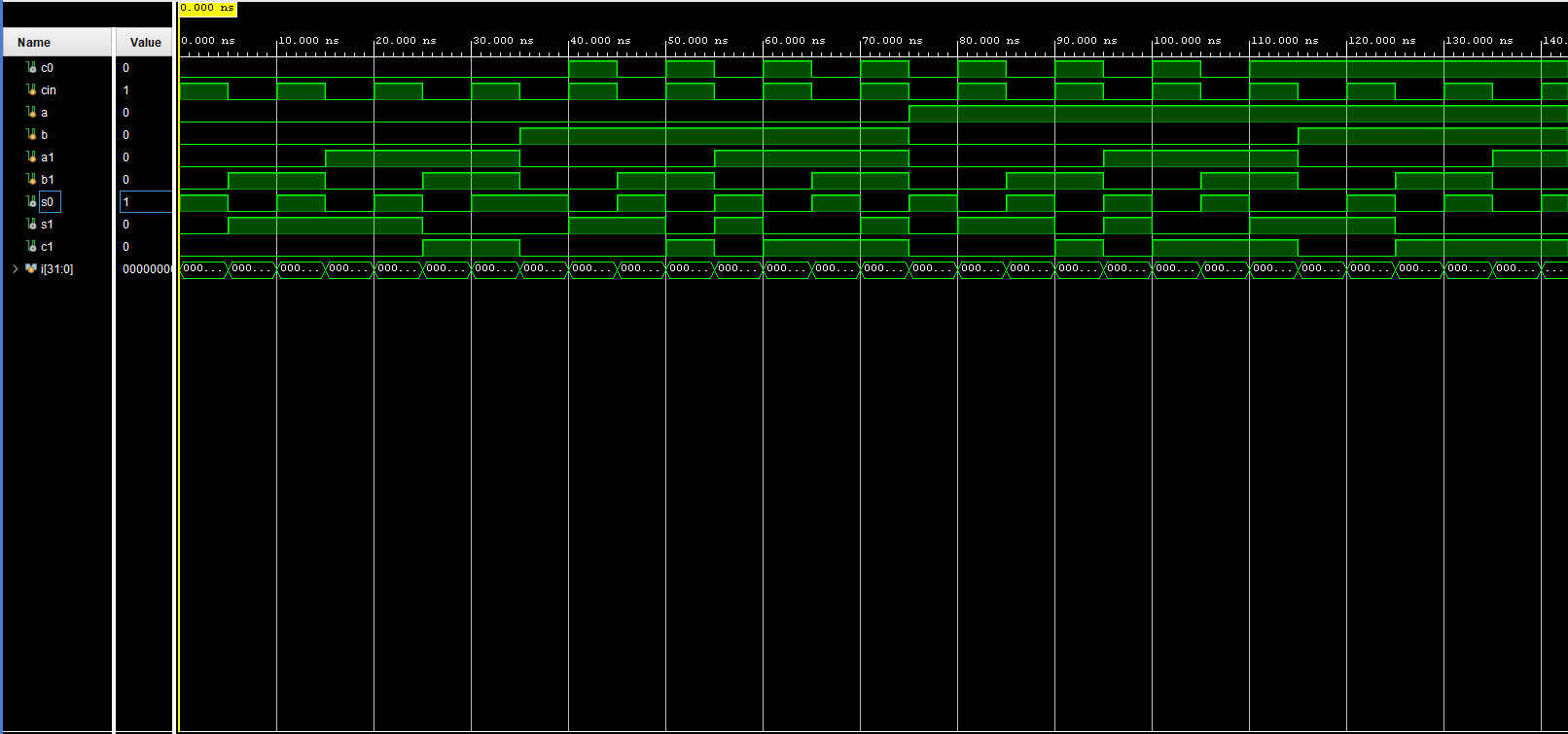

Figure 1.5: 2-bit full adder simulation.

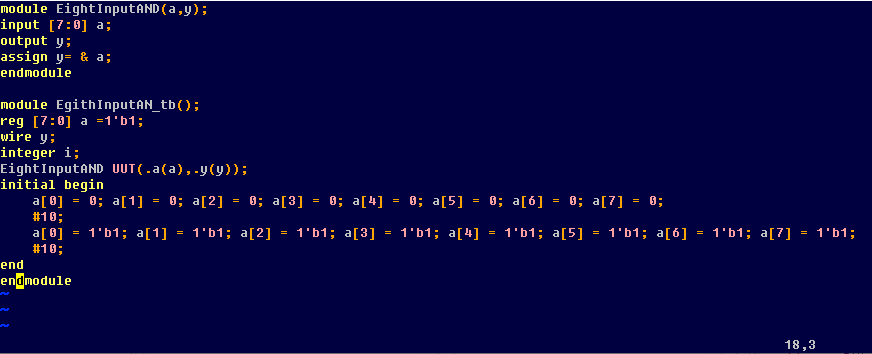

Figure 1.6: 8-bit AND code.

Figure 1.7: 8-bit AND simulation.

Figure 1.8: 4-1 MUX code.

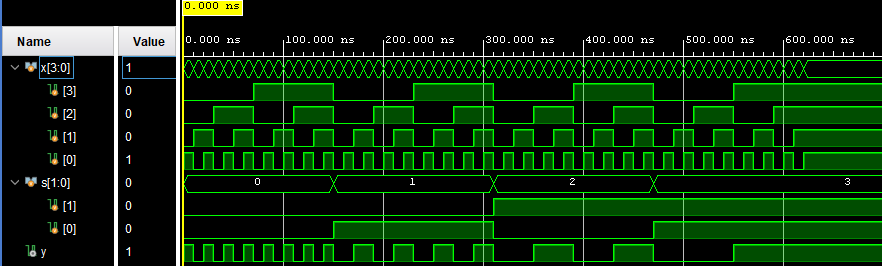

Figure 1.9: 4-1 MUX simulation.

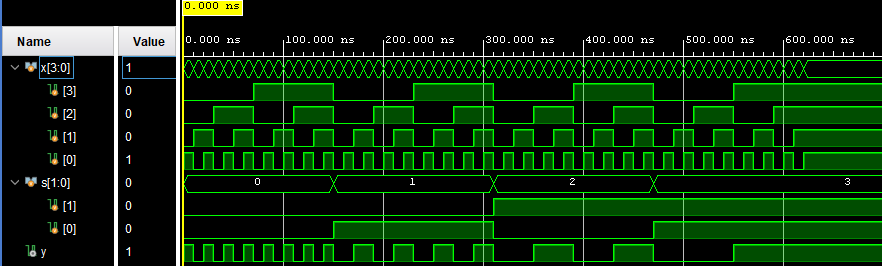

Task 2:

Using Verilog and Viado to

design a 'Running LED' program on the FPGA board.

SSDisplayCode.png

Figure 2: Running LED code.

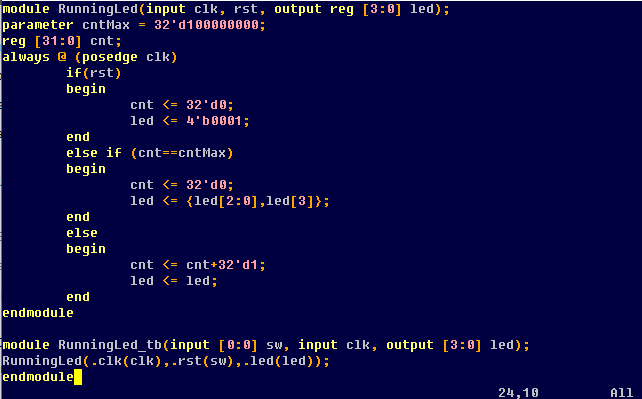

Task 3:

Interface the switches with the 7-segment display on the board.

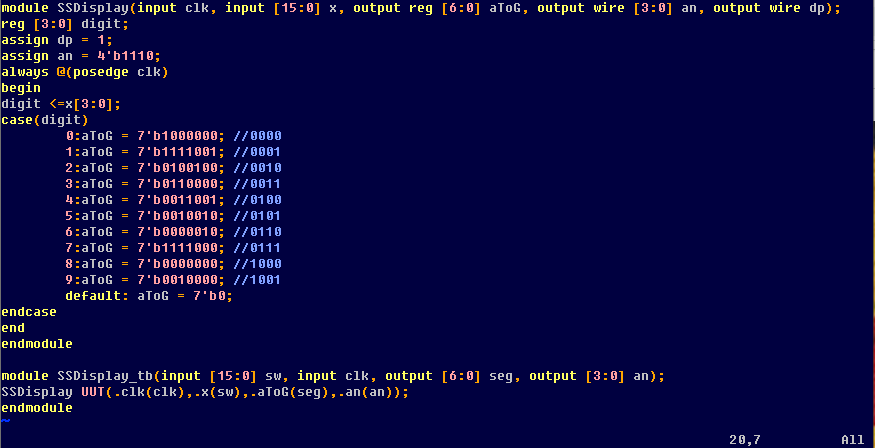

Figure 3: SSDisplay code for all sections.

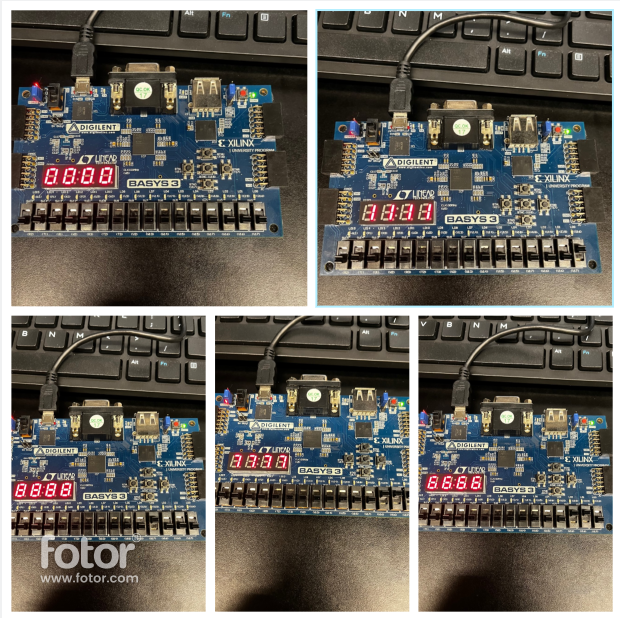

Figure 3.1: Implementation of SSDisplay to board.

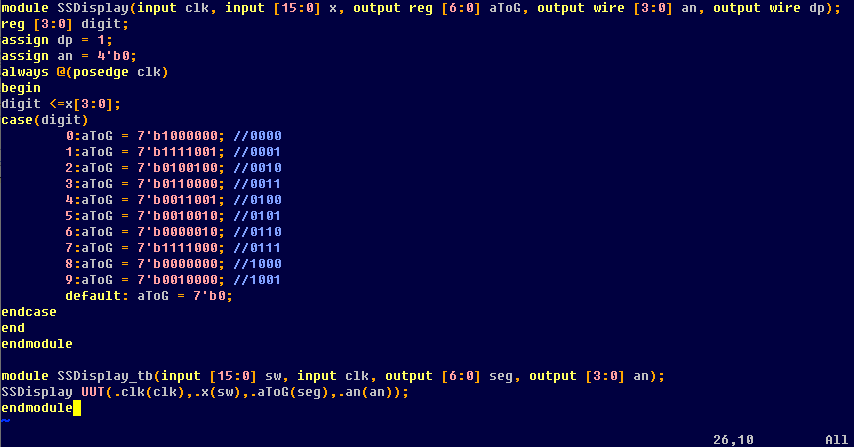

Task 4:

Modify the code in task 3 to only show the number on one of the

displays.

Figure 4: SSDisplay for only having one of the displays on.