Task 1: Half Adder and Full Adder

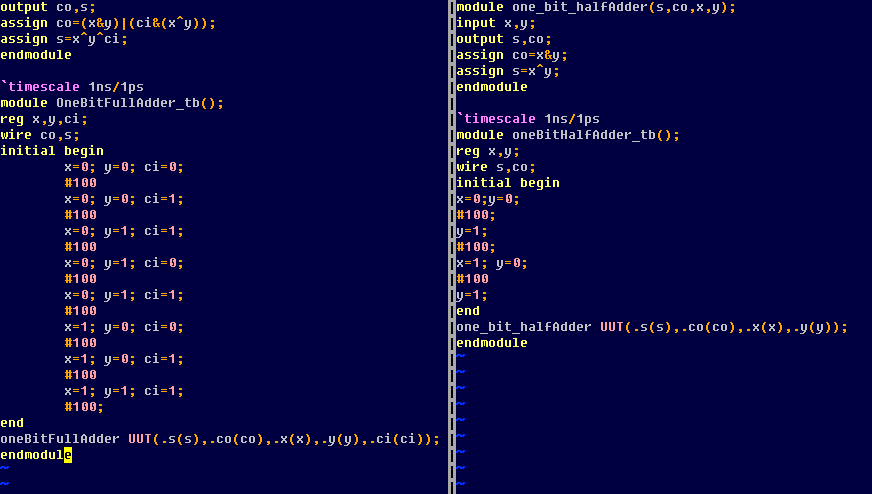

Figure 1: Full Adder on the Left, Half Adder on the right.

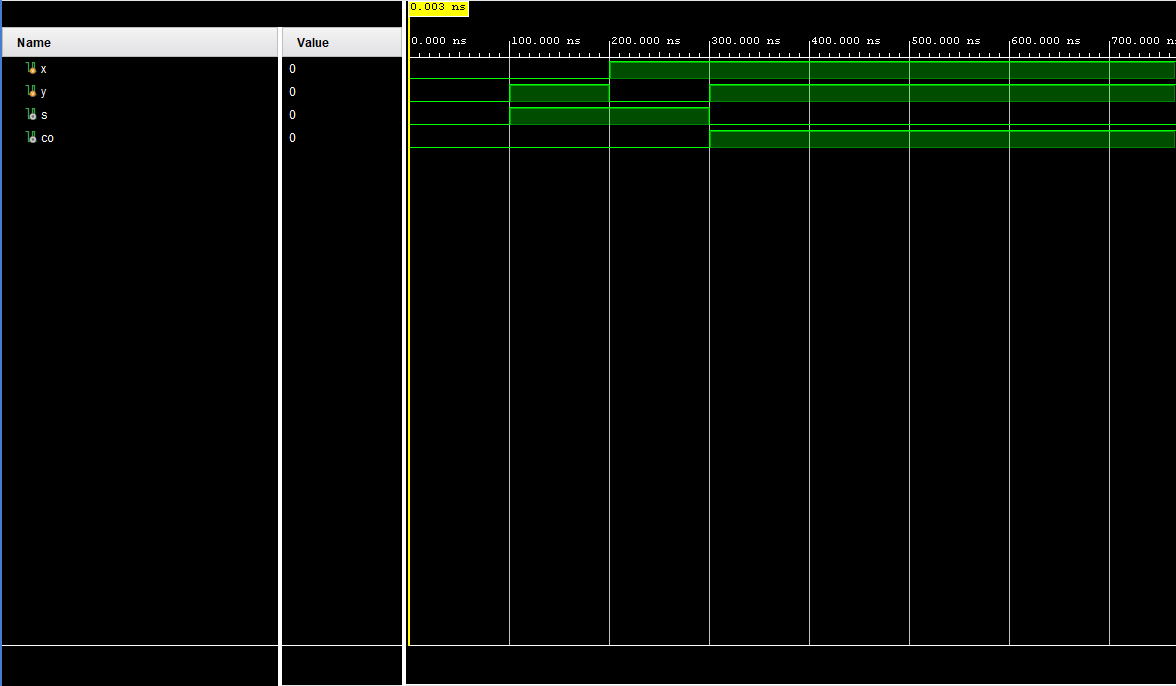

Figure 1.1: Half Adder Simulation.

Figure 1.2: Full Adder Simulation.

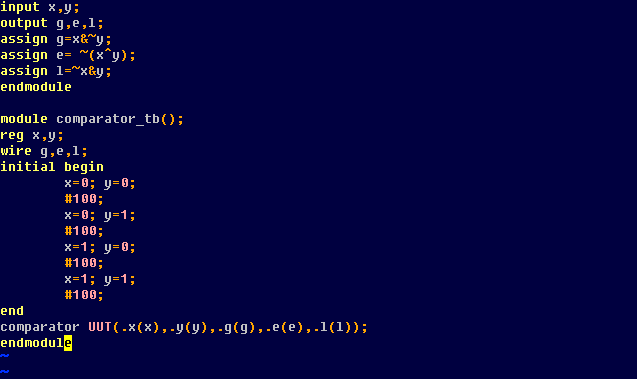

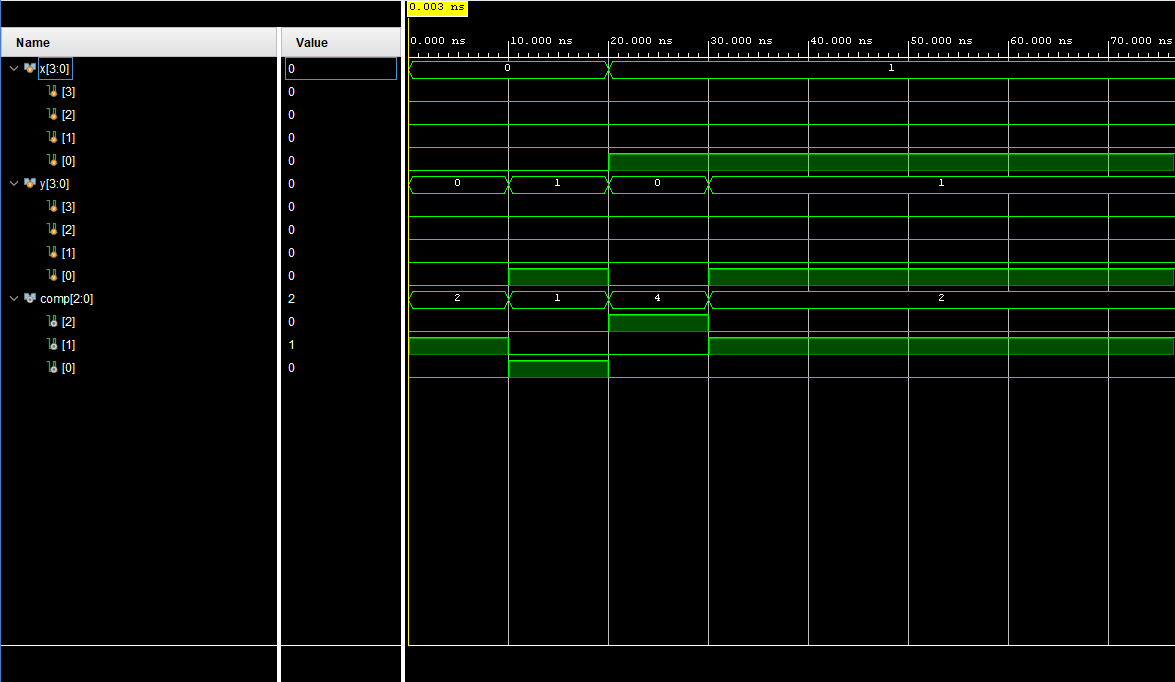

Task

2: Design teh testbench for the comparator and the simulation

results.

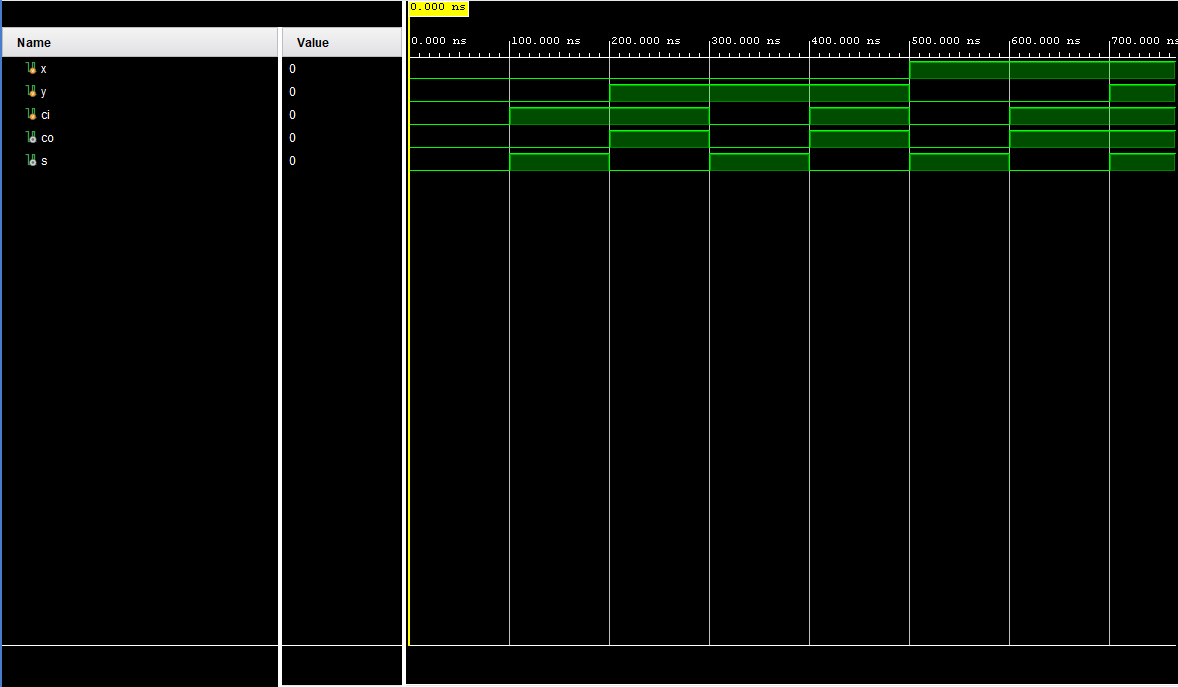

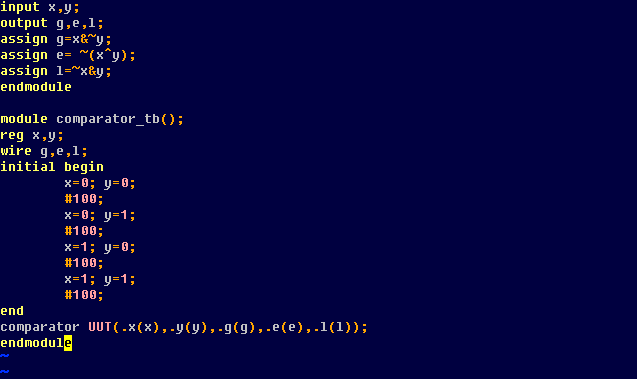

Figure 2: One bit comparator module and test bench.

Figure 2.1: One bit comparator Simulation.

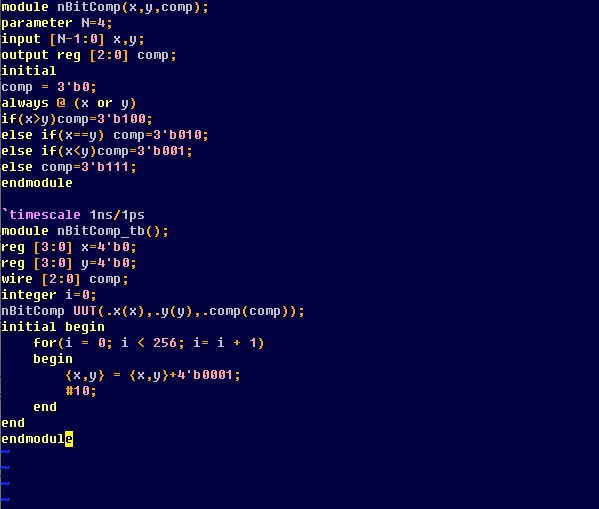

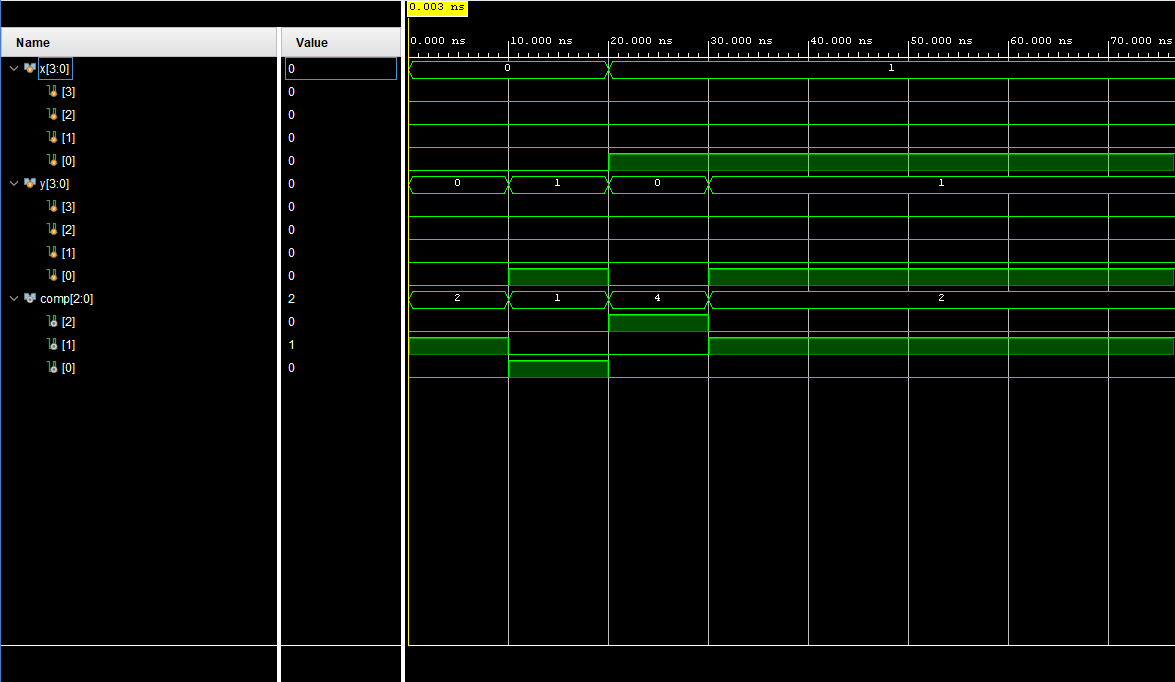

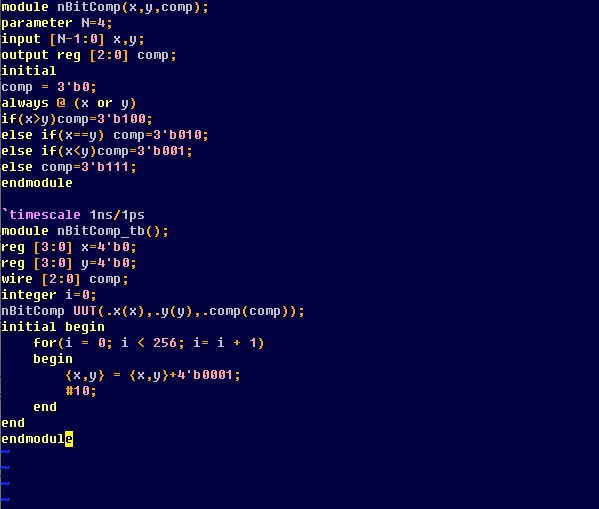

Task 3: Design the testbench for the 4-bit comparator and show the simulation results.

nBitCompSim.png

nBitCompSim.png

Figure 3: Four bit comparator code.

Figure 3.1: 4-Bit comparator code.

Task 4: 2-bit comparator on the

Basys-3 board.

Figure 4: Two bit comparator code.

Figure 2: One bit comparator module and test bench.

Figure 2.1: One bit comparator Simulation.

Task 3: Design the testbench for the 4-bit comparator and show the simulation results.

nBitCompSim.png

nBitCompSim.pngFigure 3: Four bit comparator code.

Figure 3.1: 4-Bit comparator code.

Figure 4: Two bit comparator code.

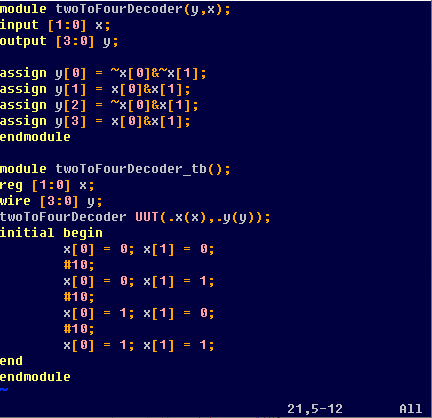

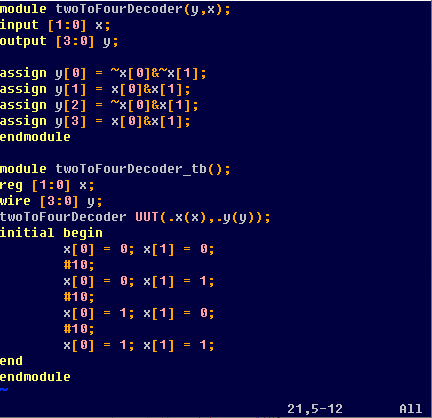

Task 5:

Design the testbench for the decoder and verify the logic using

simulation.

Figure 5: Decoder code with test bench.

Figure 5.1: Decoder Simulation.

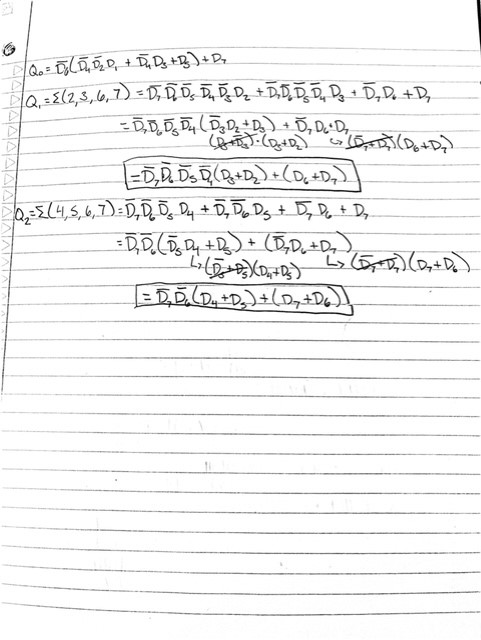

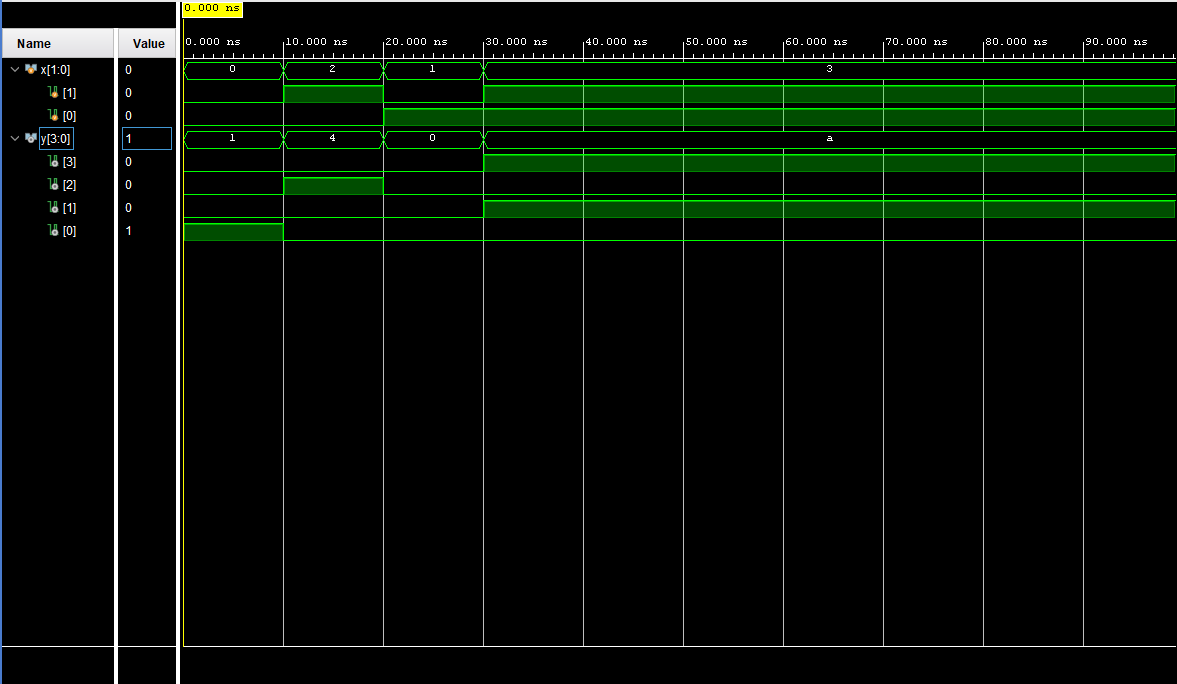

Figure 6: Finding Q1 and Q2.

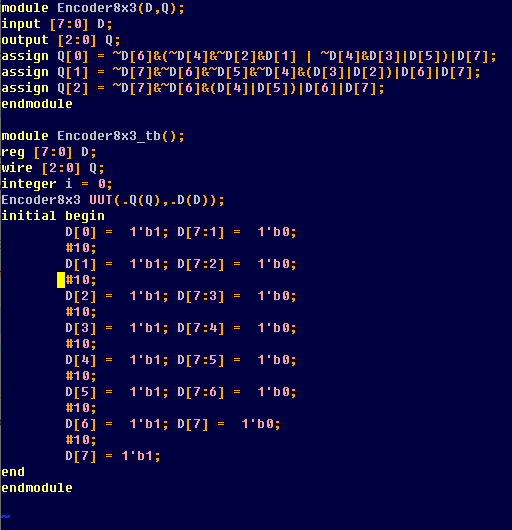

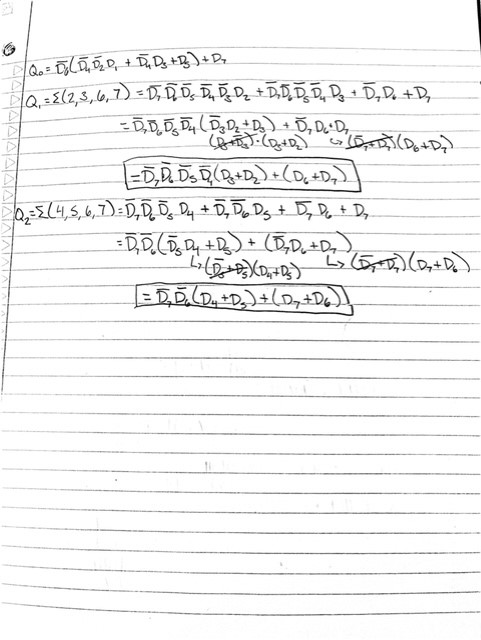

Figure 6.1: Priority 8x3 Encoder.

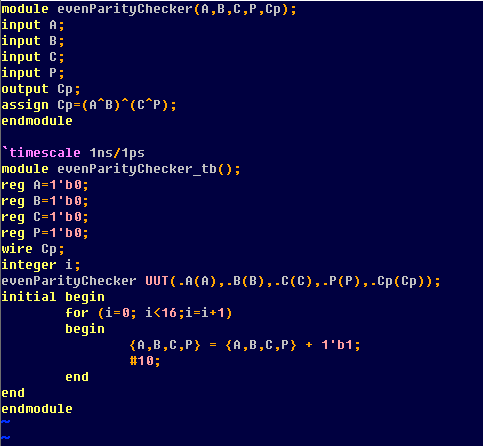

Figure 6.2: Priority 8x3 Encoder Simulation.

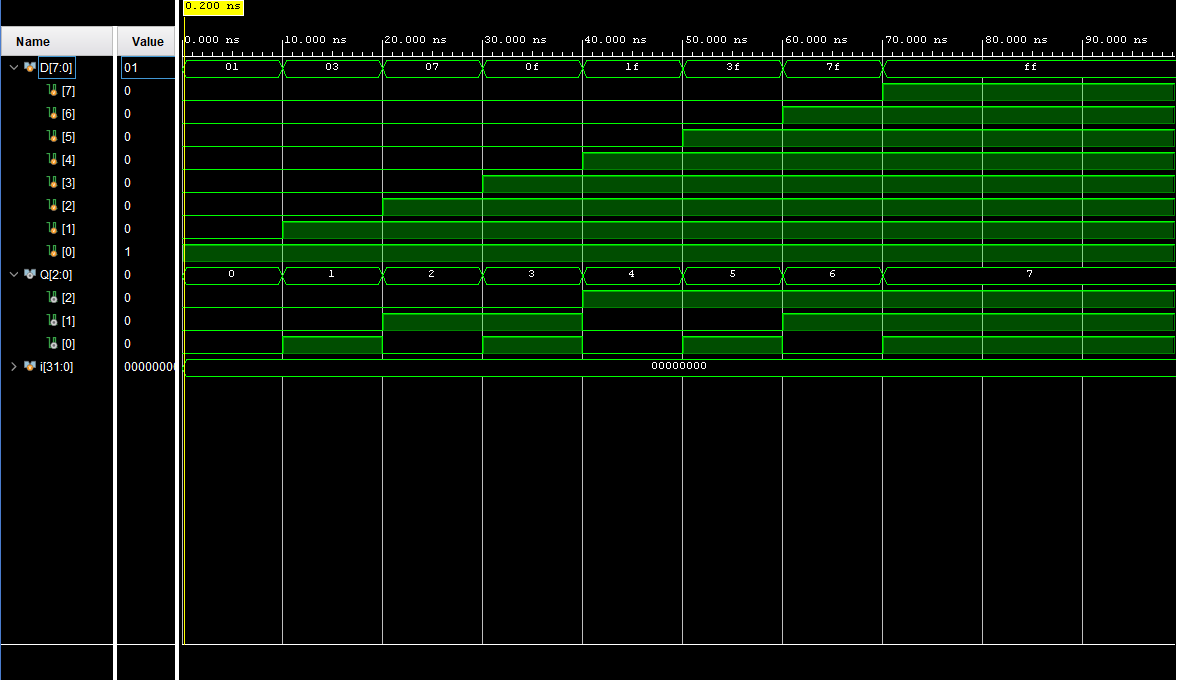

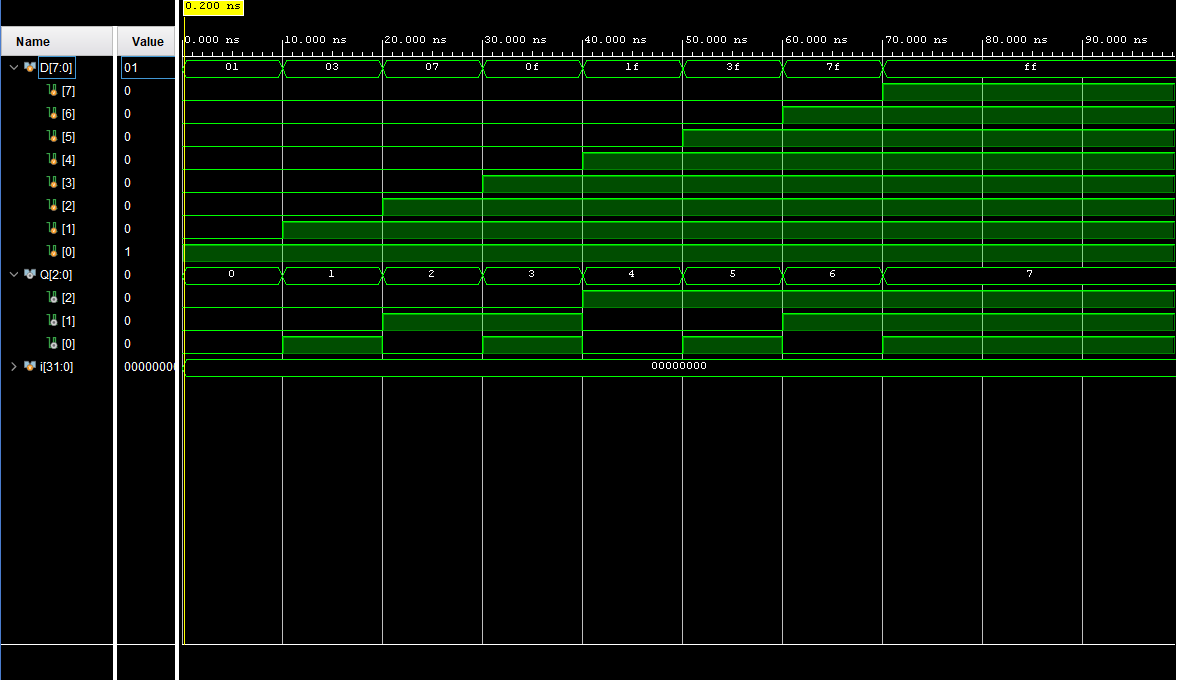

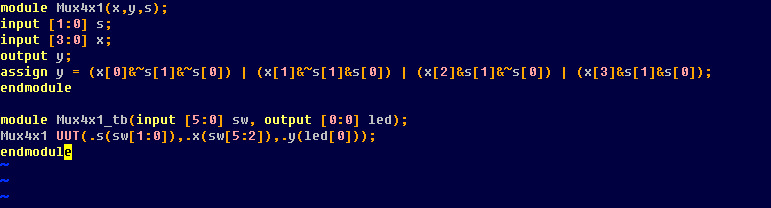

Figure 7: 4-1 MUX code.

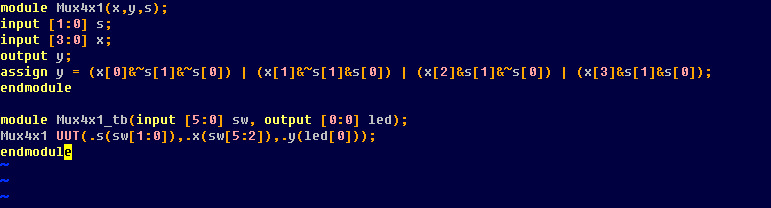

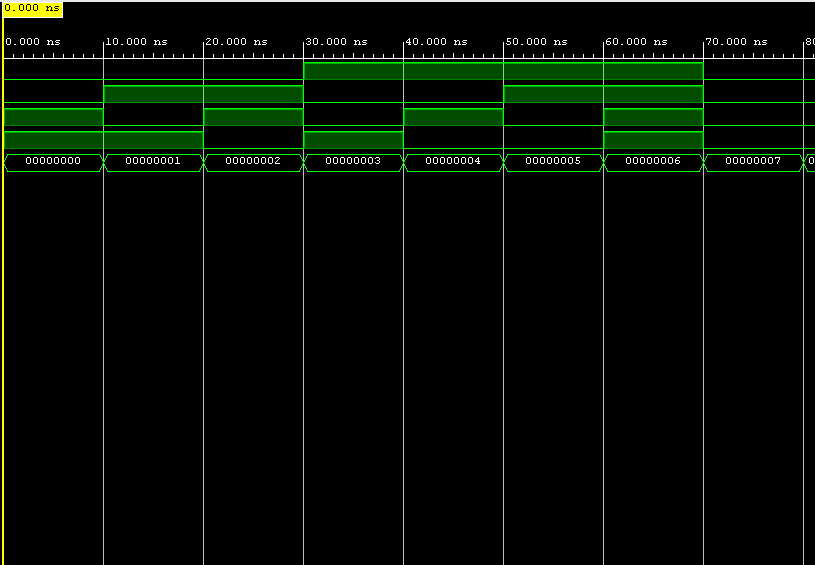

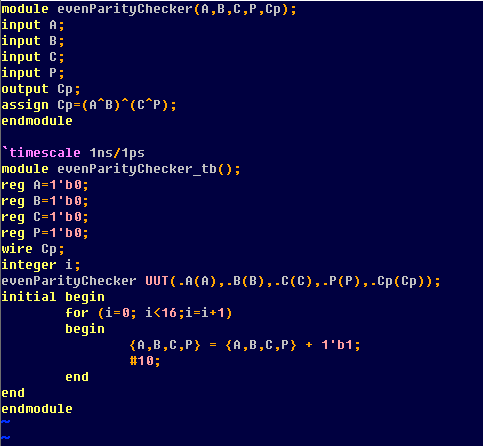

Figure 8: Even parity checker code.

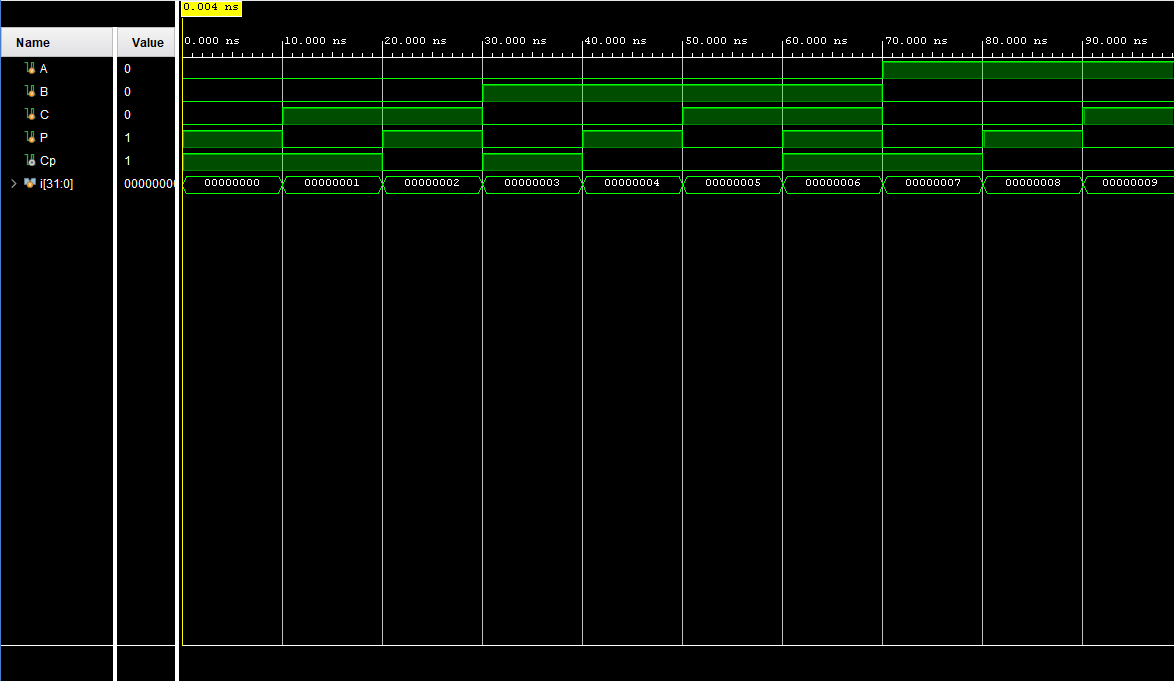

Figure 8.1: Even parity checker simulation.

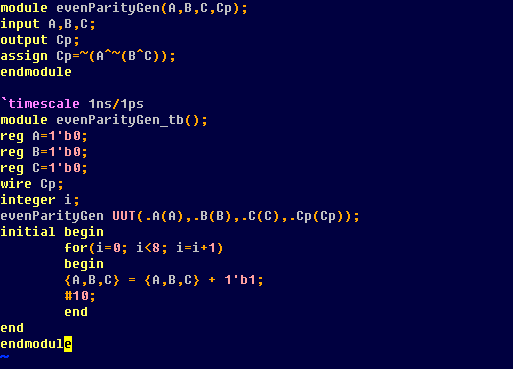

Figure 8.2: Even parity generator code.

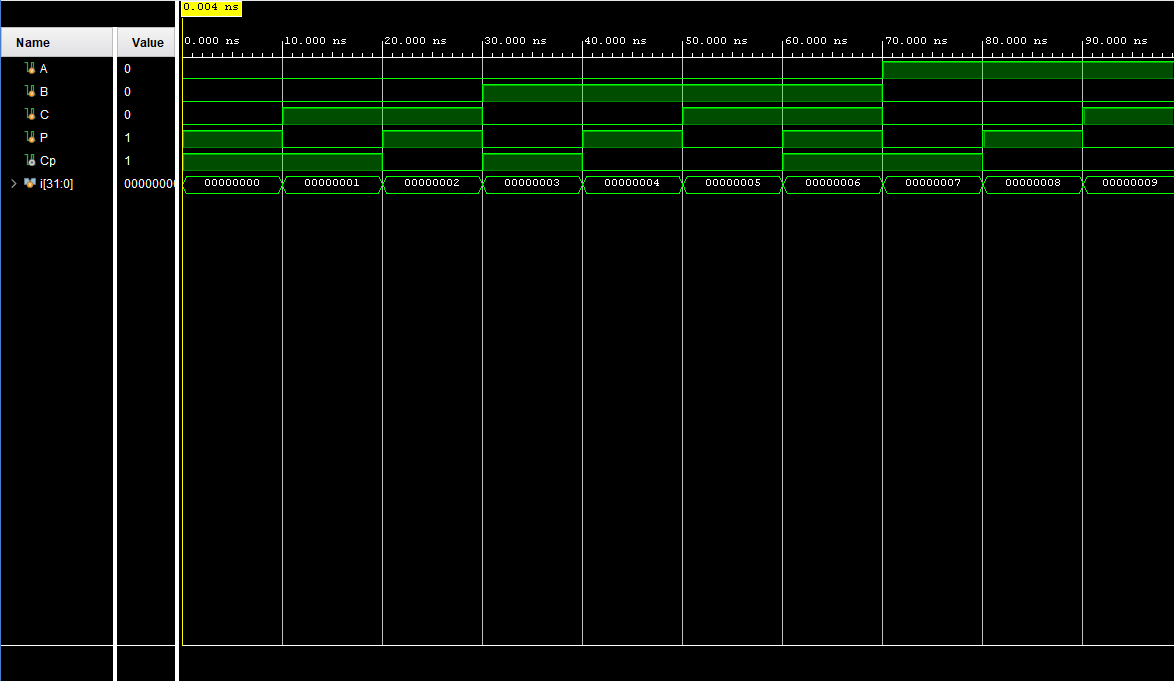

Figure 8.3: Even parity generator simulation.

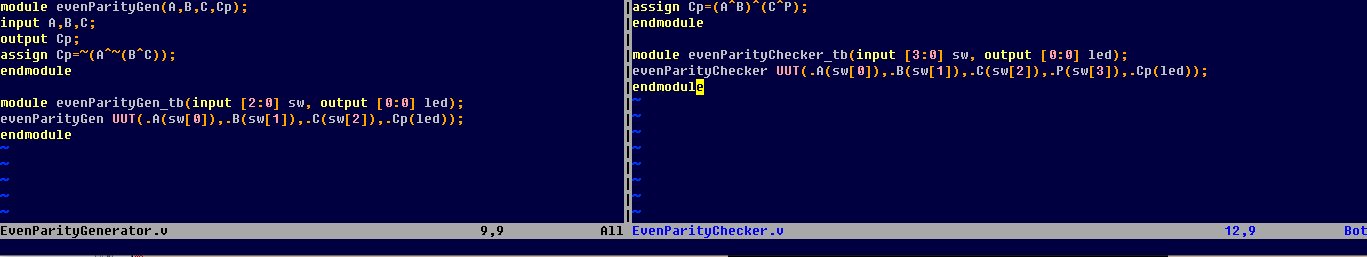

Figure 8.4: Right even parity checker and left is the even parity generator.

Figure 5: Decoder code with test bench.

Figure 5.1: Decoder Simulation.

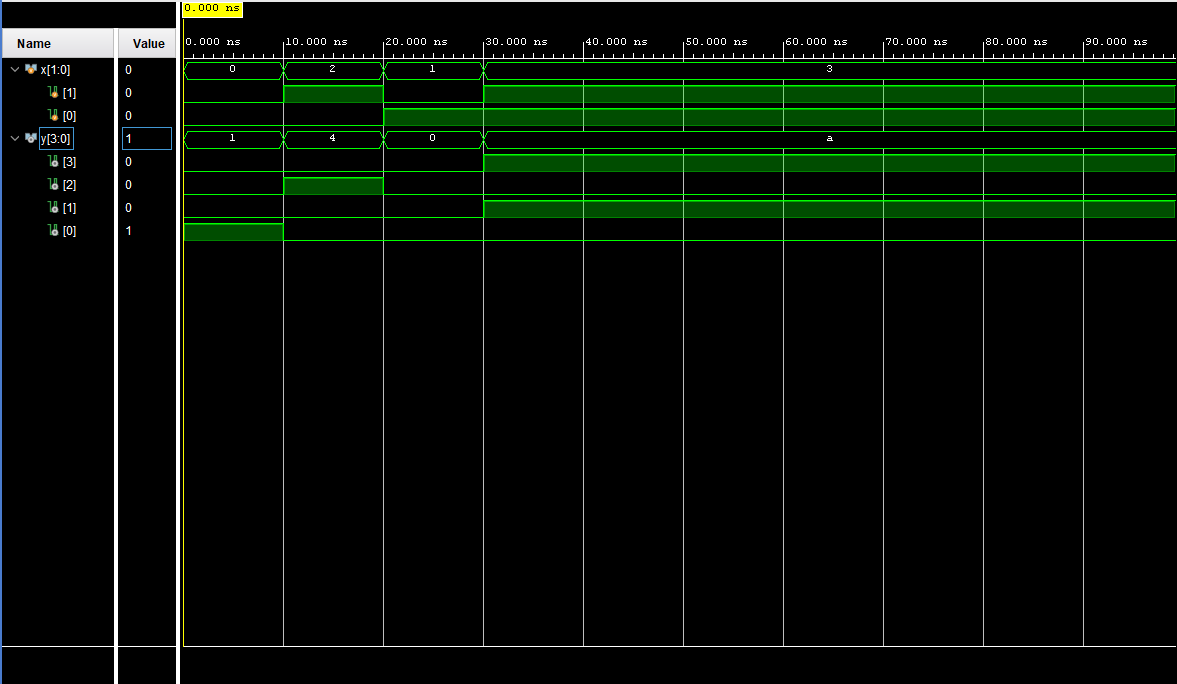

Task 6:

Encoder 8x3 Priority.

Figure 6: Finding Q1 and Q2.

Figure 6.1: Priority 8x3 Encoder.

Figure 6.2: Priority 8x3 Encoder Simulation.

Task 7:

Implemnting a 4-1 MUX to the Basys-3 board.

Figure 7: 4-1 MUX code.

Task 8:

Parity generator and checker.

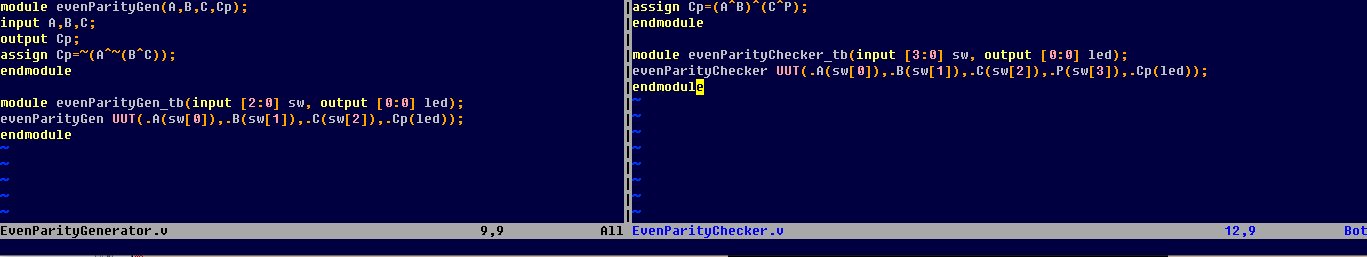

Figure 8: Even parity checker code.

Figure 8.1: Even parity checker simulation.

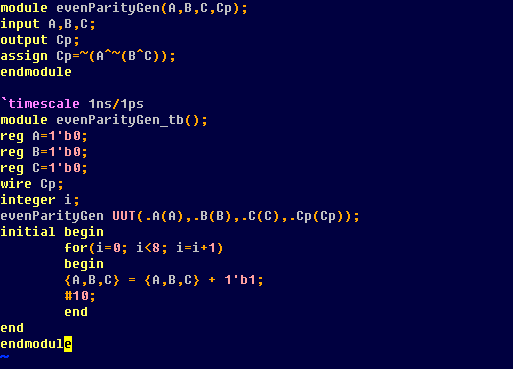

Figure 8.2: Even parity generator code.

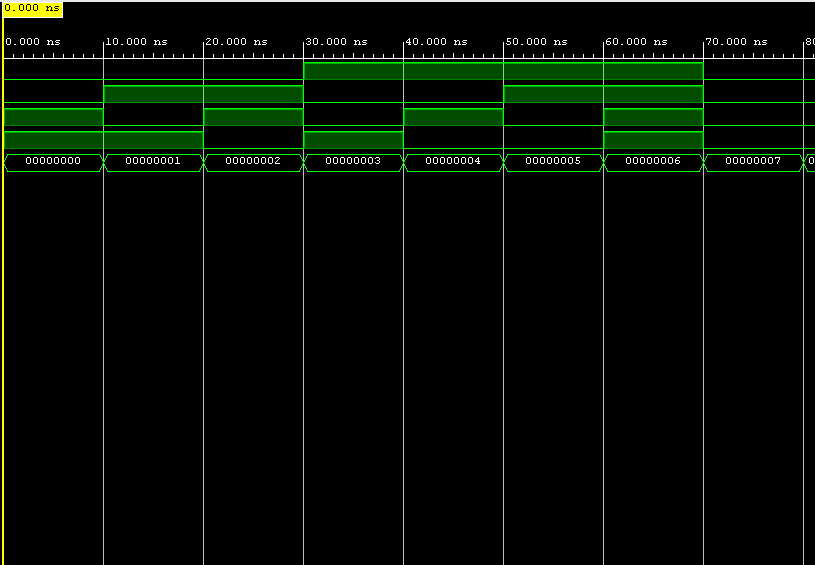

Figure 8.3: Even parity generator simulation.

Figure 8.4: Right even parity checker and left is the even parity generator.

Task 9:

Implementation of the advanced home alarm and advanced car parking.