Task 1: Use gvim and Vivado to simulate the examples in sections 2.1, 2.2, and 2.3. Post snapshots of gvim windows and vivado simulation results in your report. You must create testbenches for your simulations. (20 points)

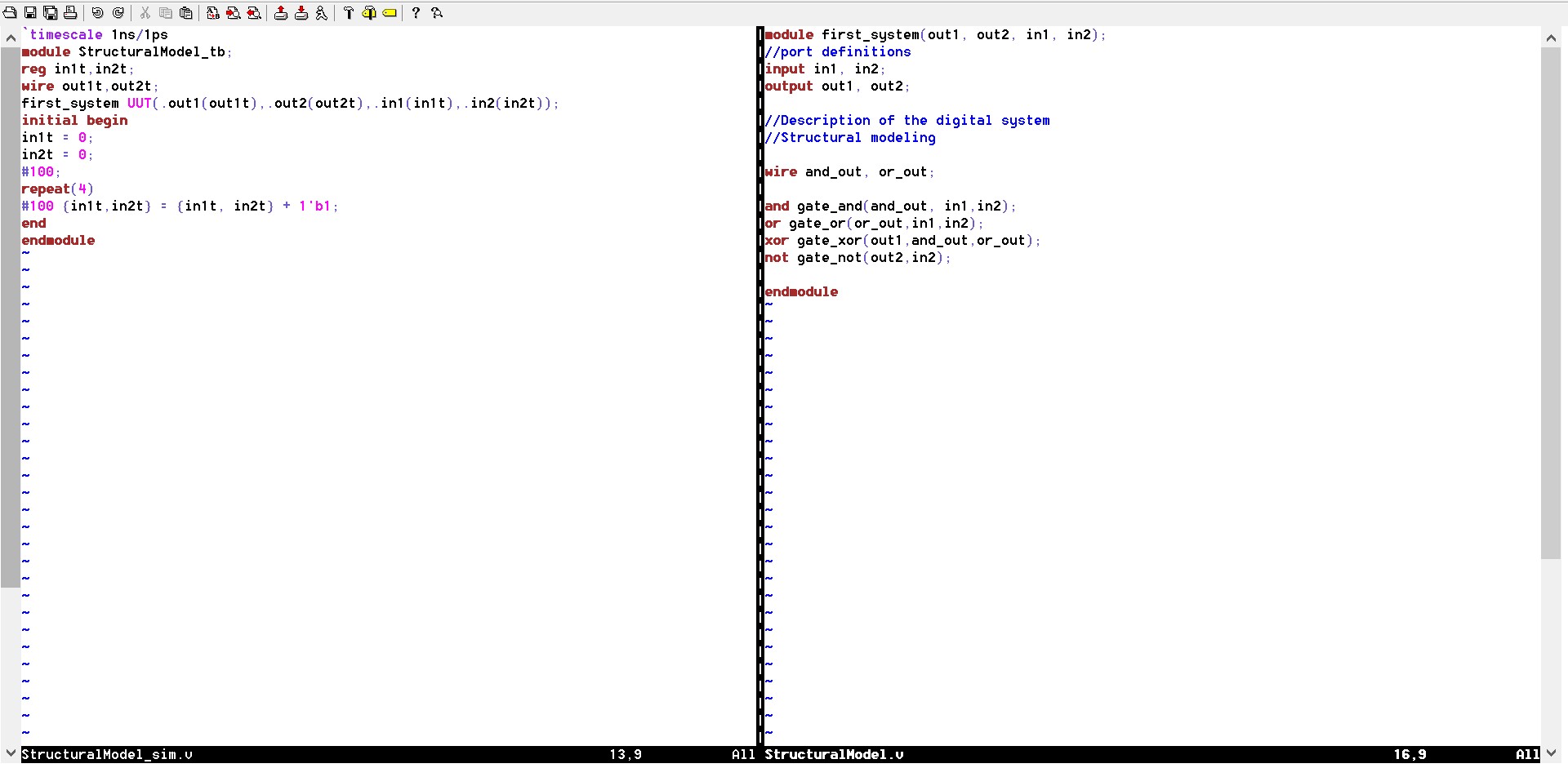

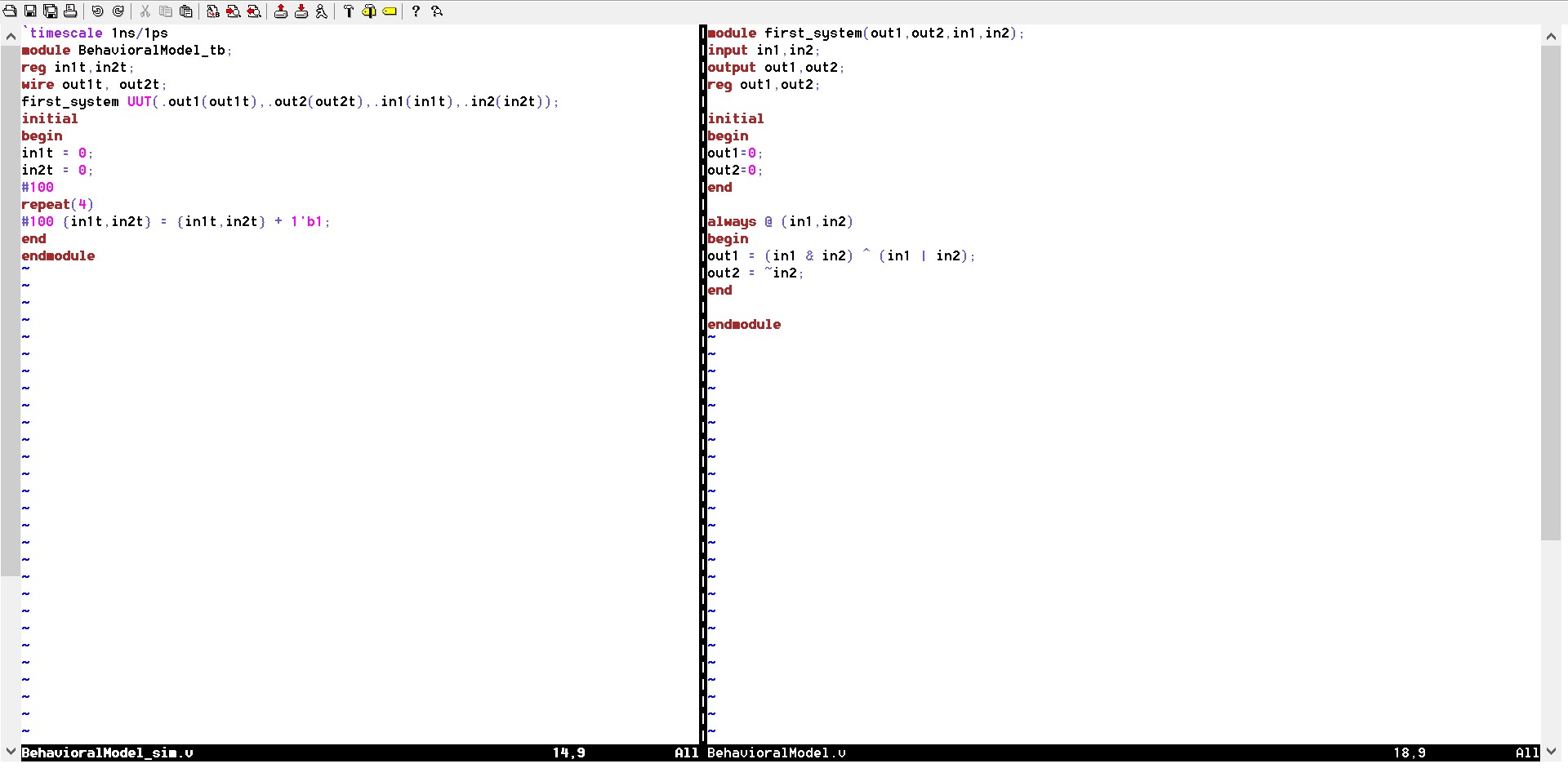

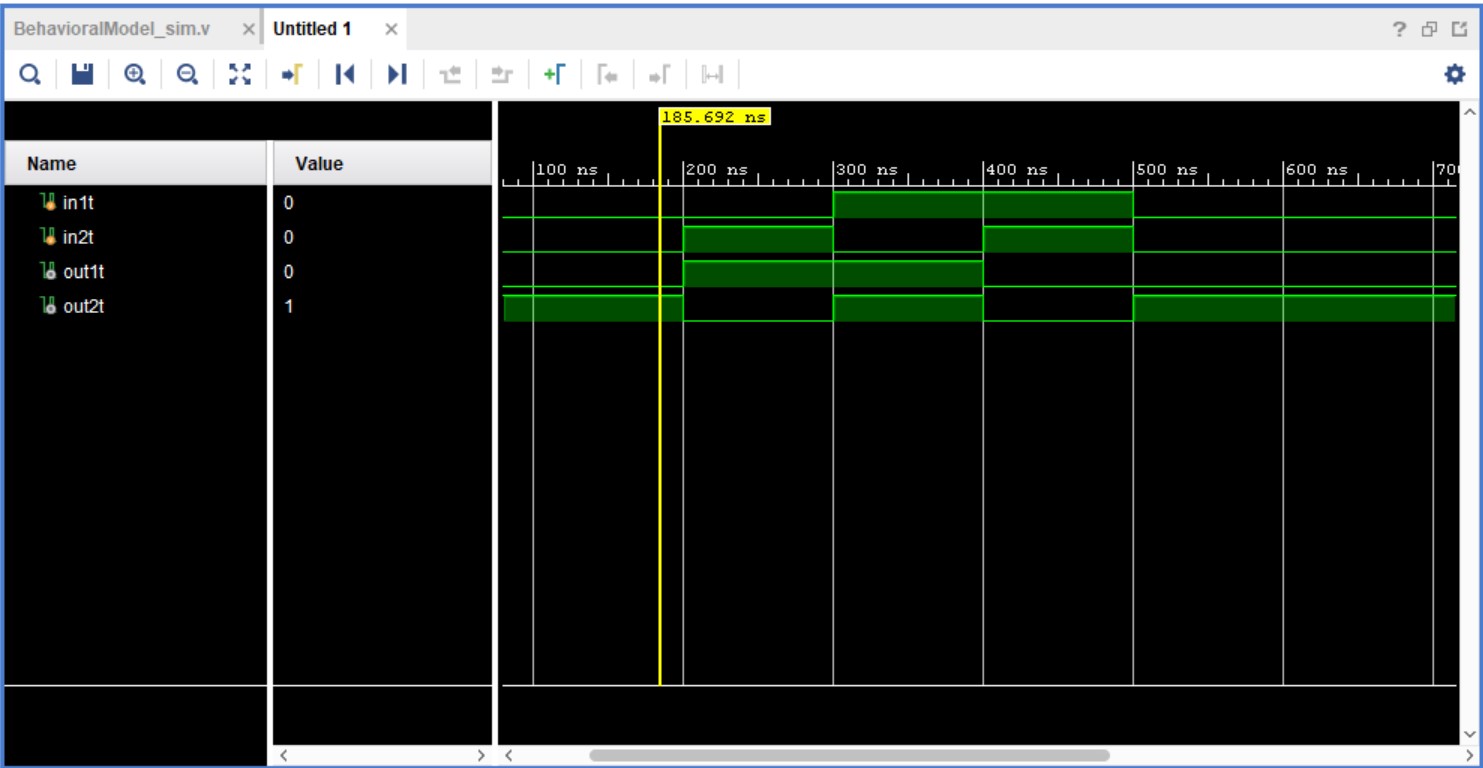

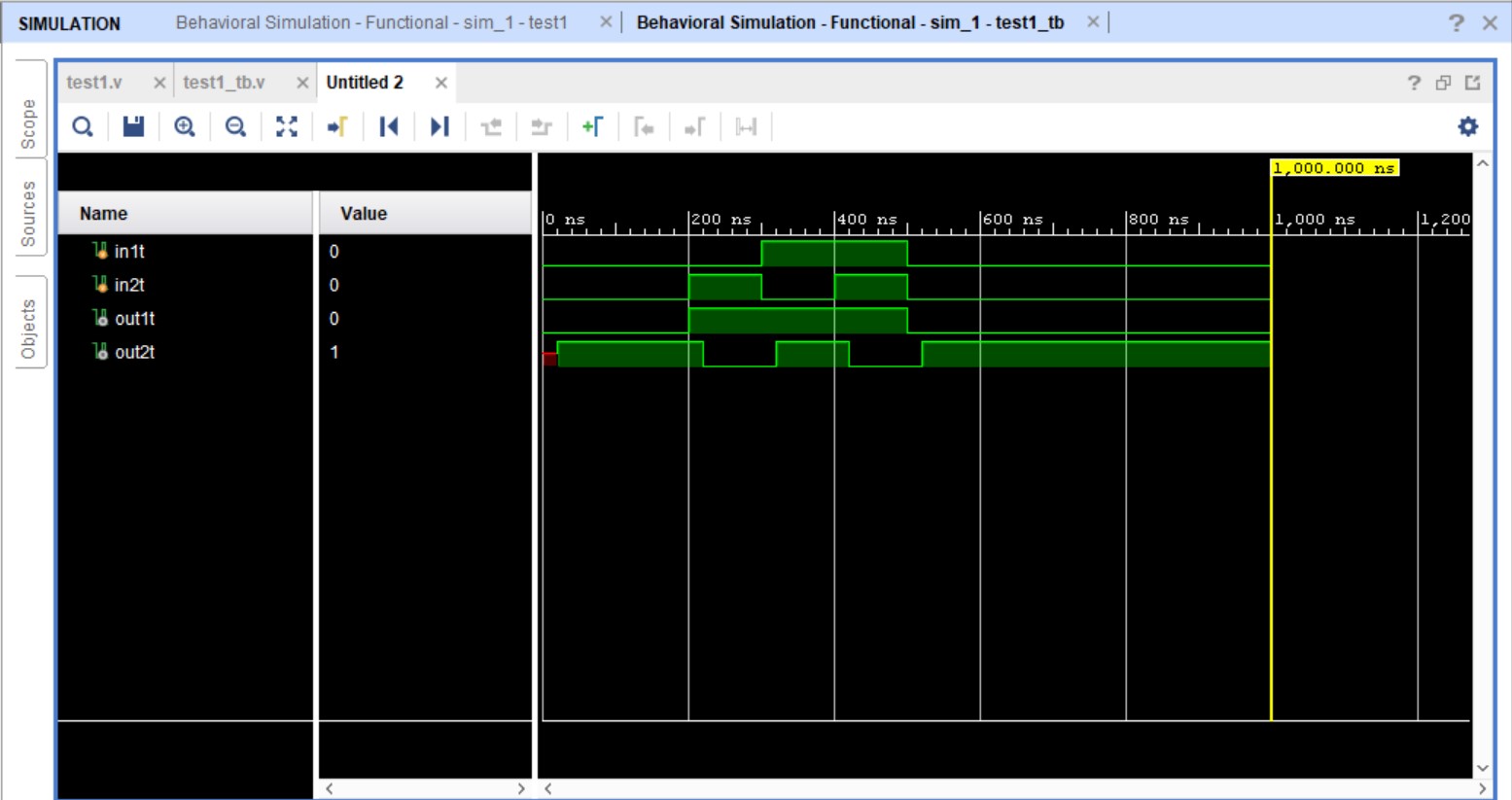

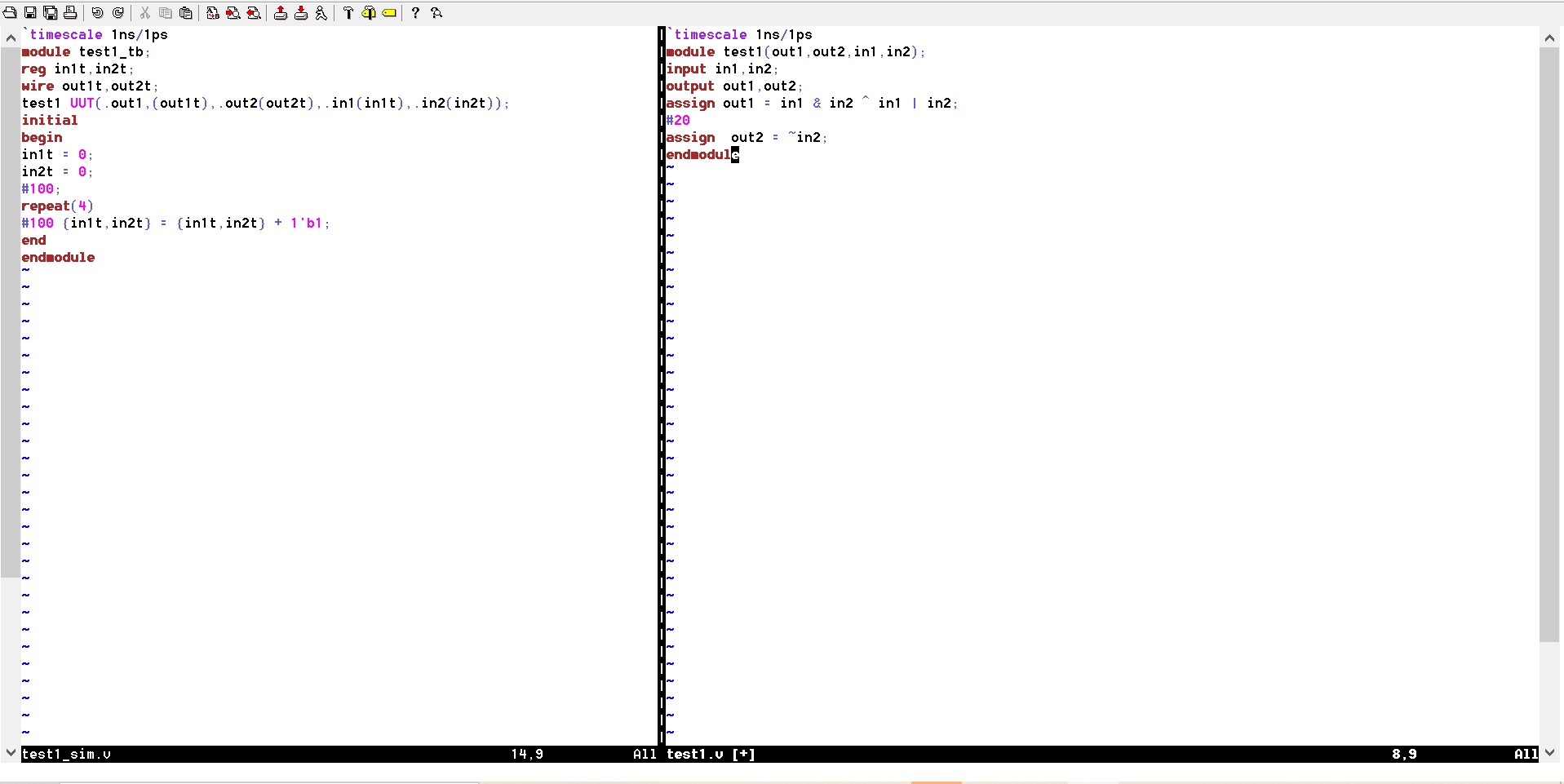

Figure 1: Unit under test and test bench code for 2.2

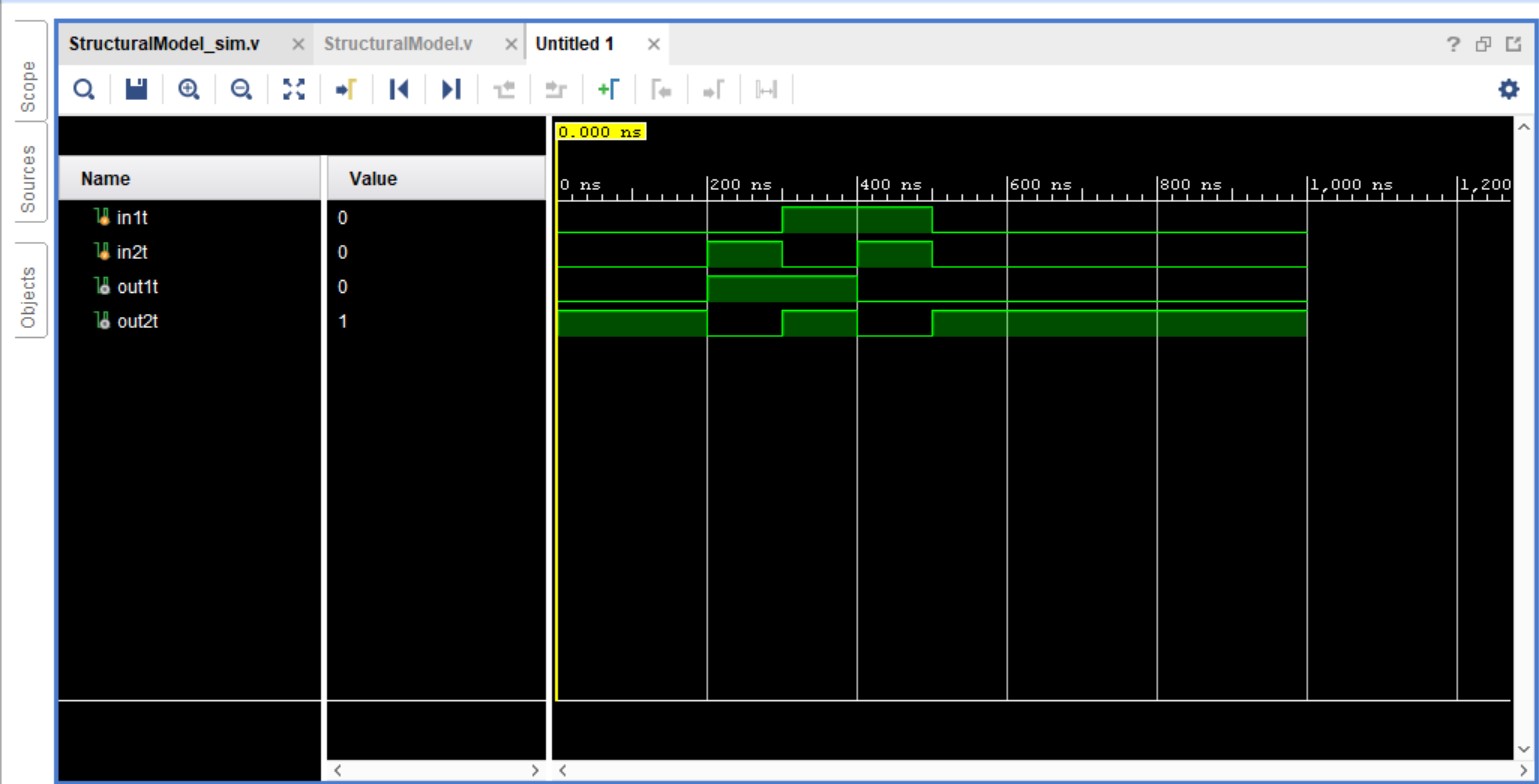

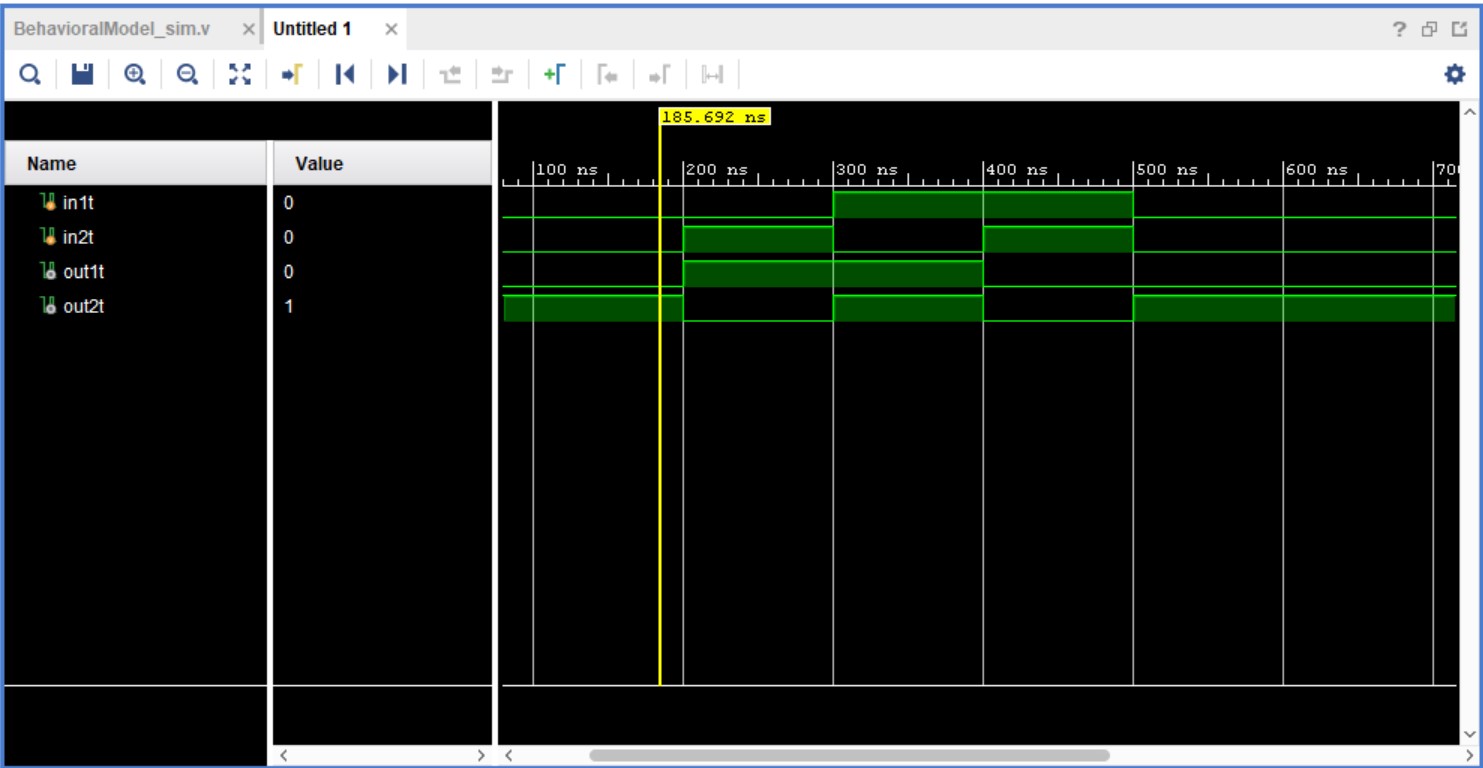

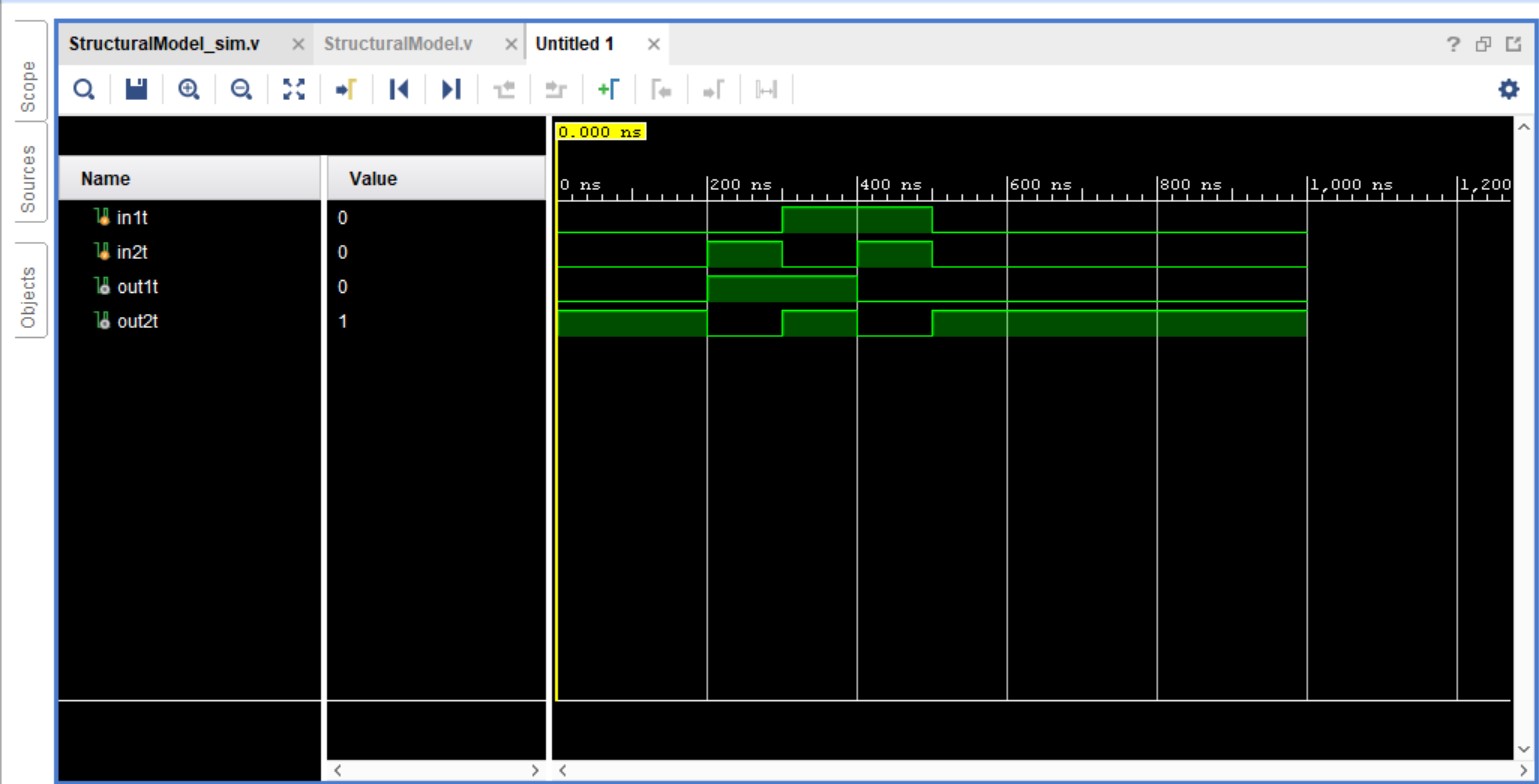

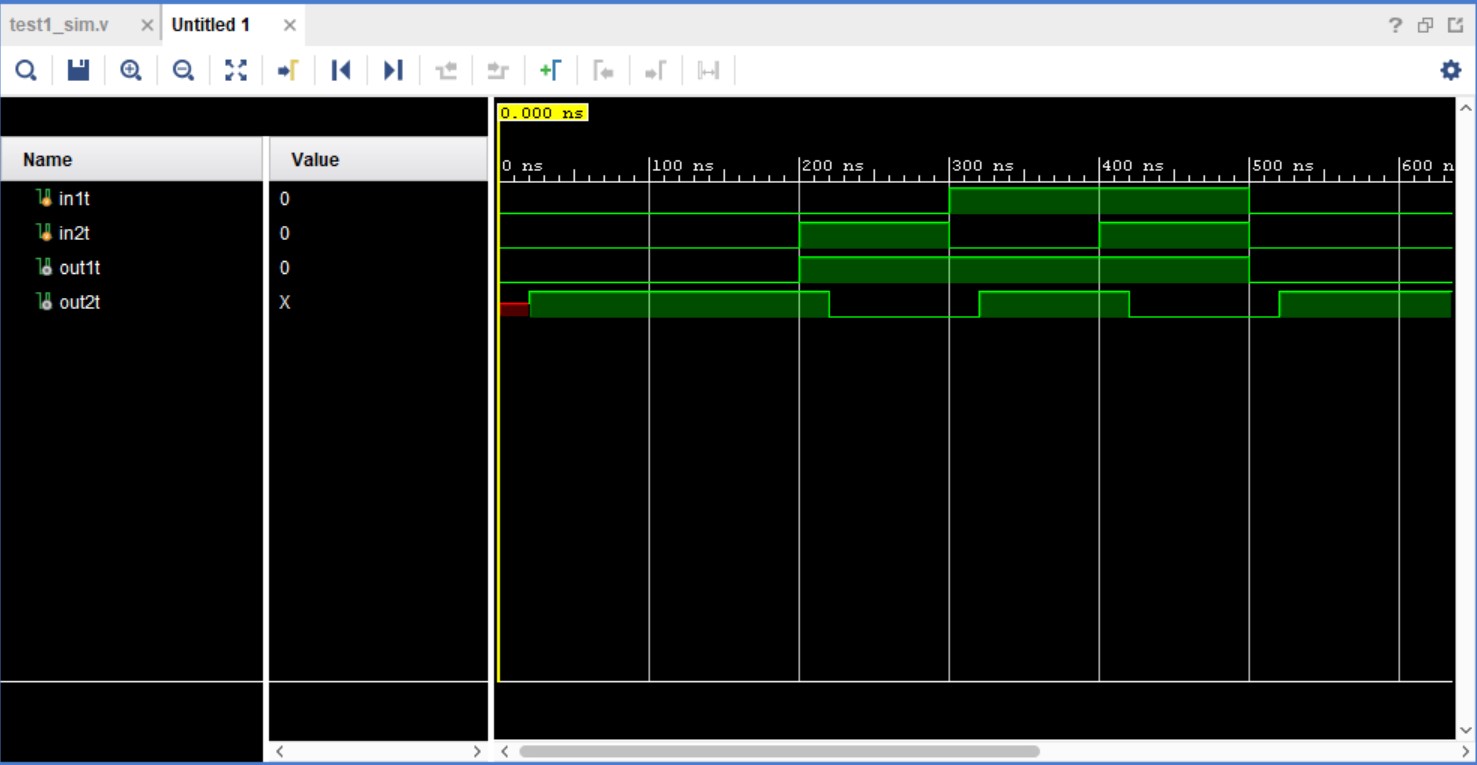

Figure 1.1: Simulation of code from Fig 1.

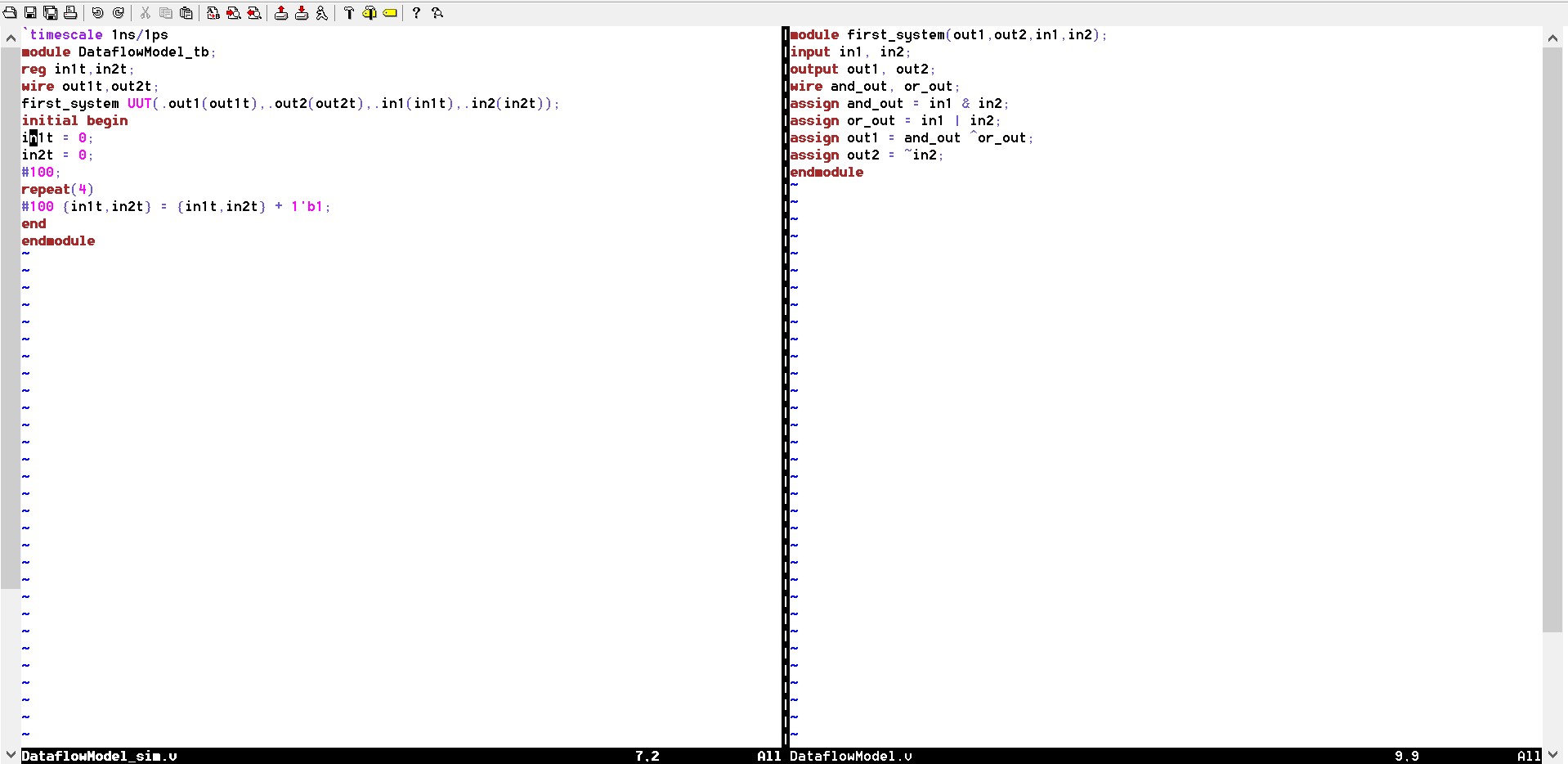

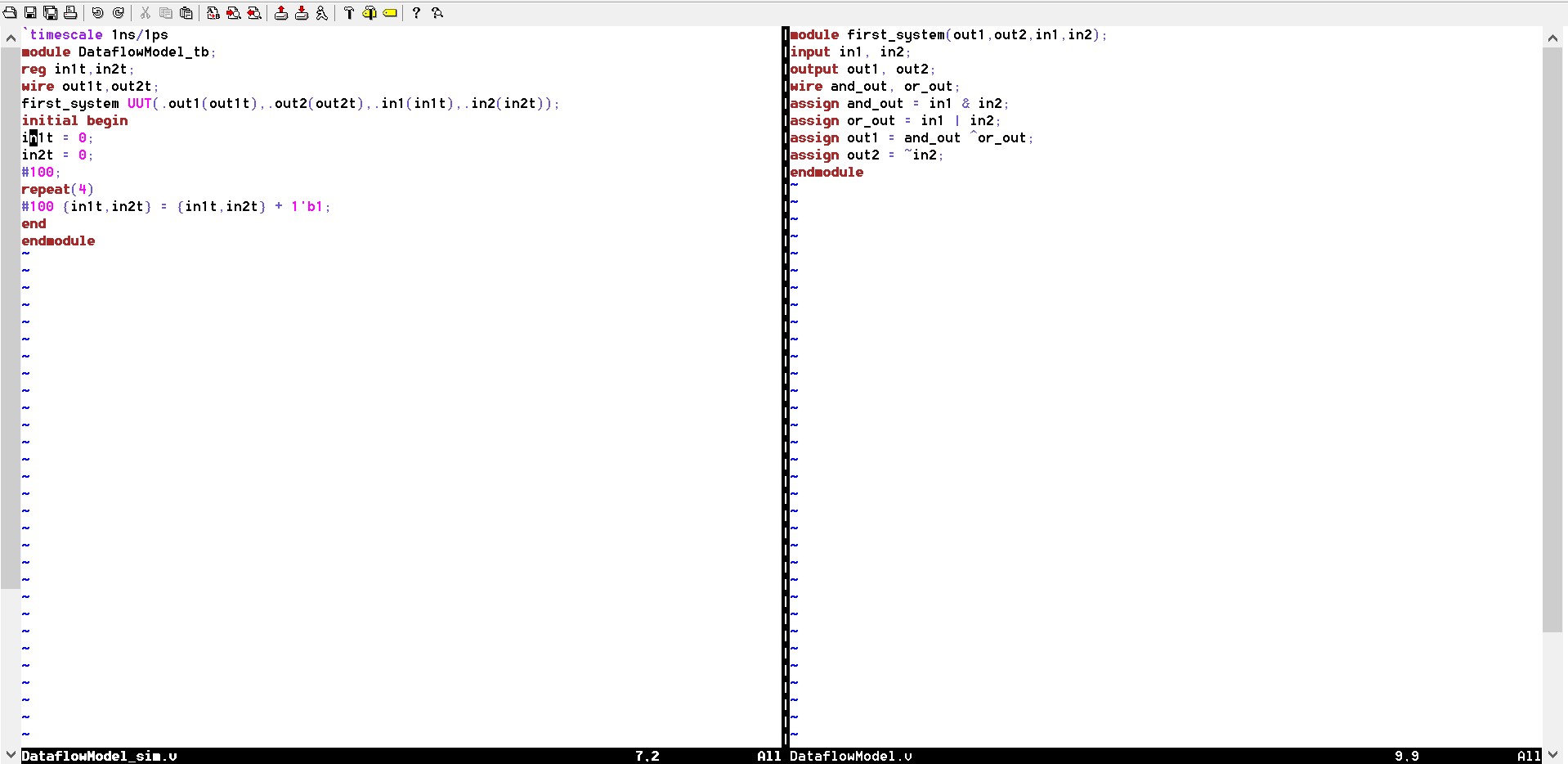

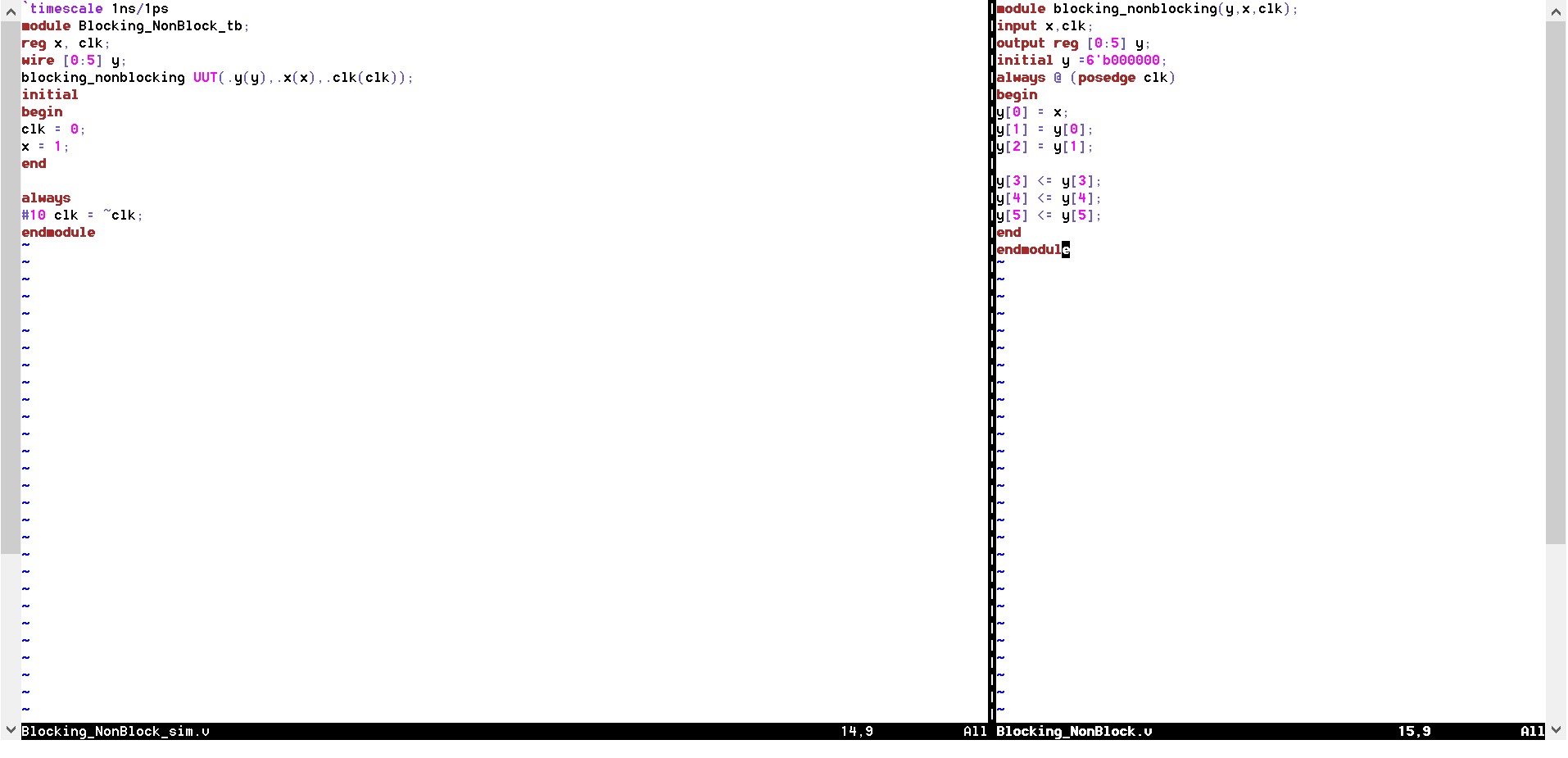

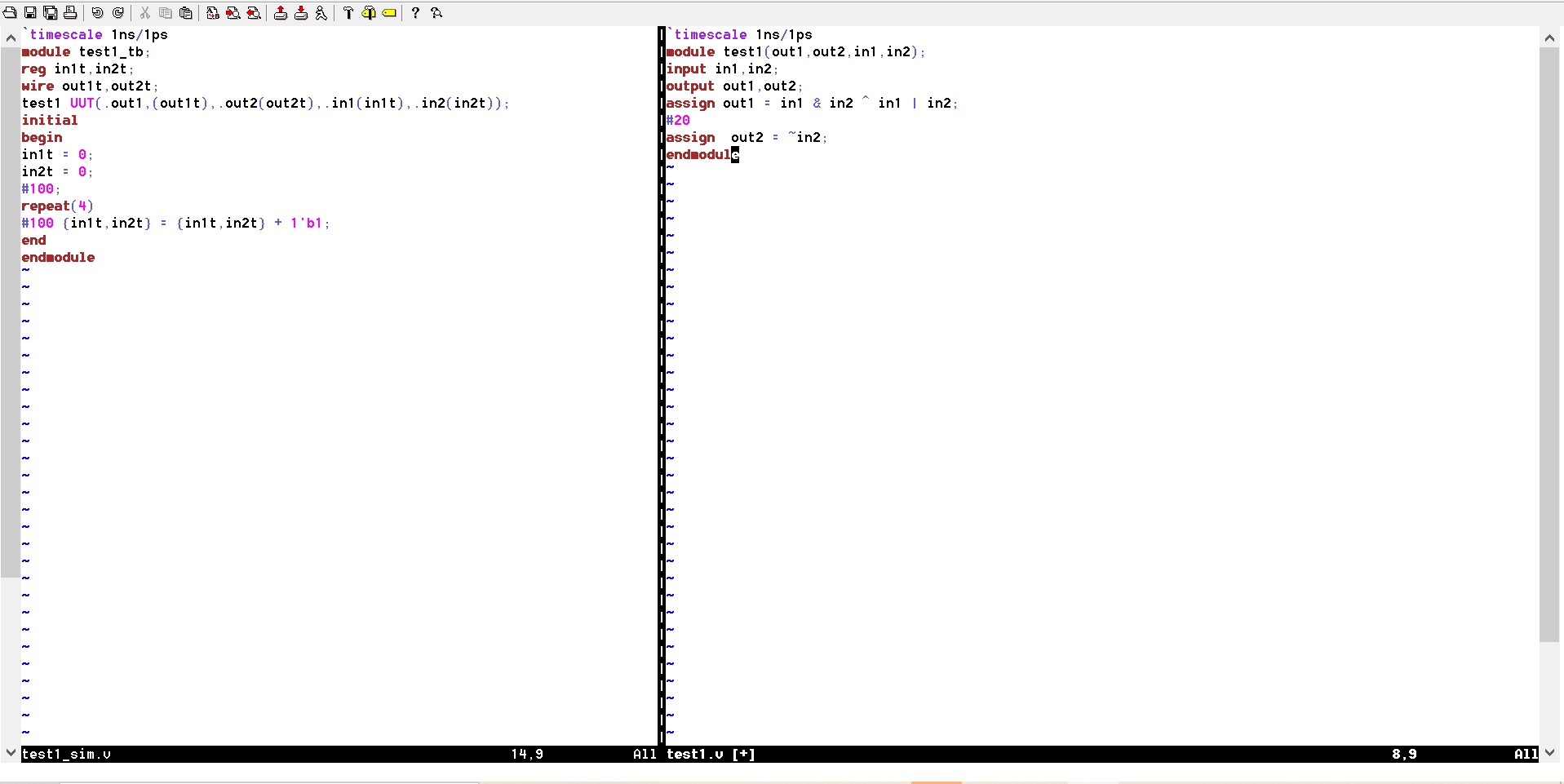

Figure 1.2: Unit under test and test bench code for 2.2

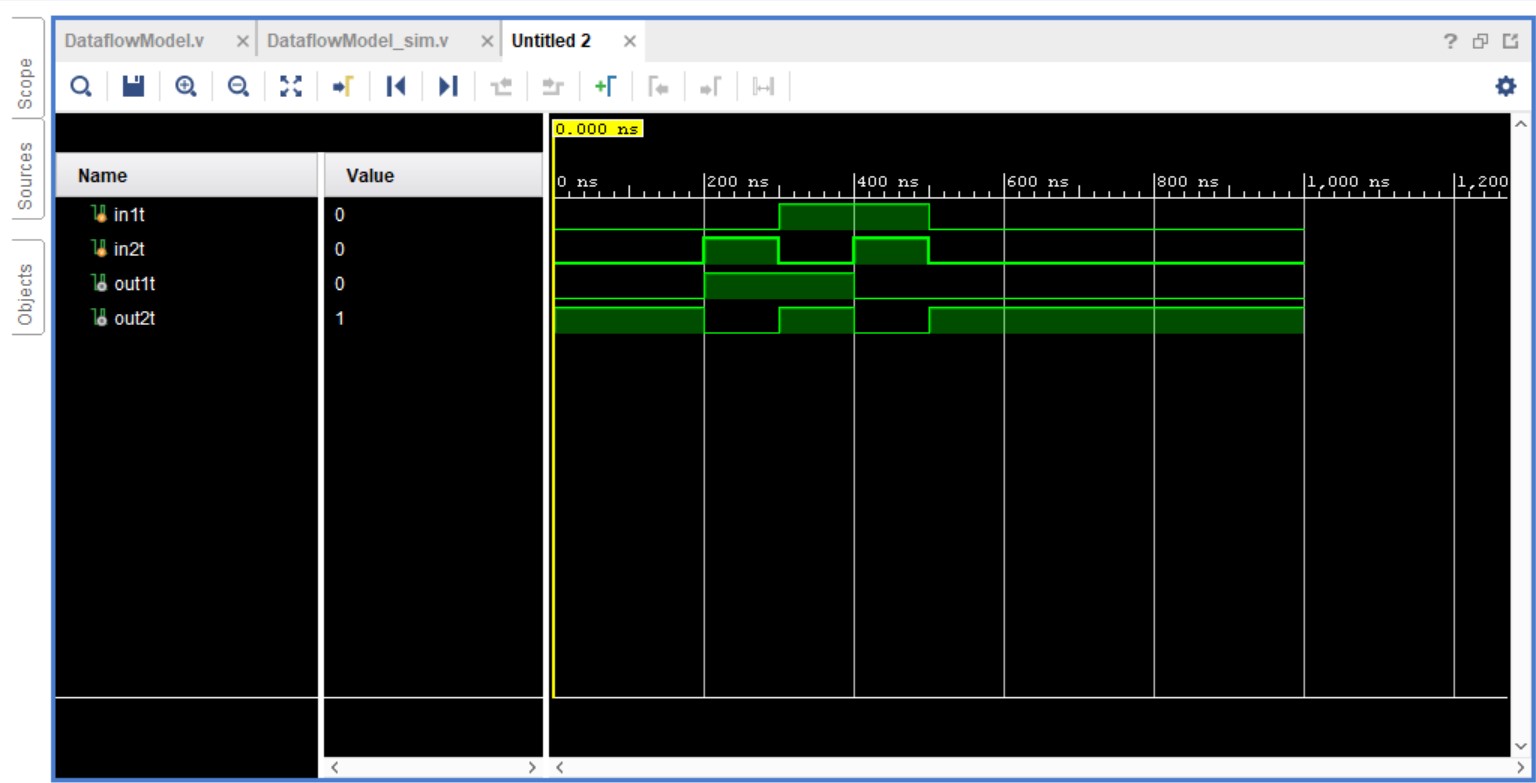

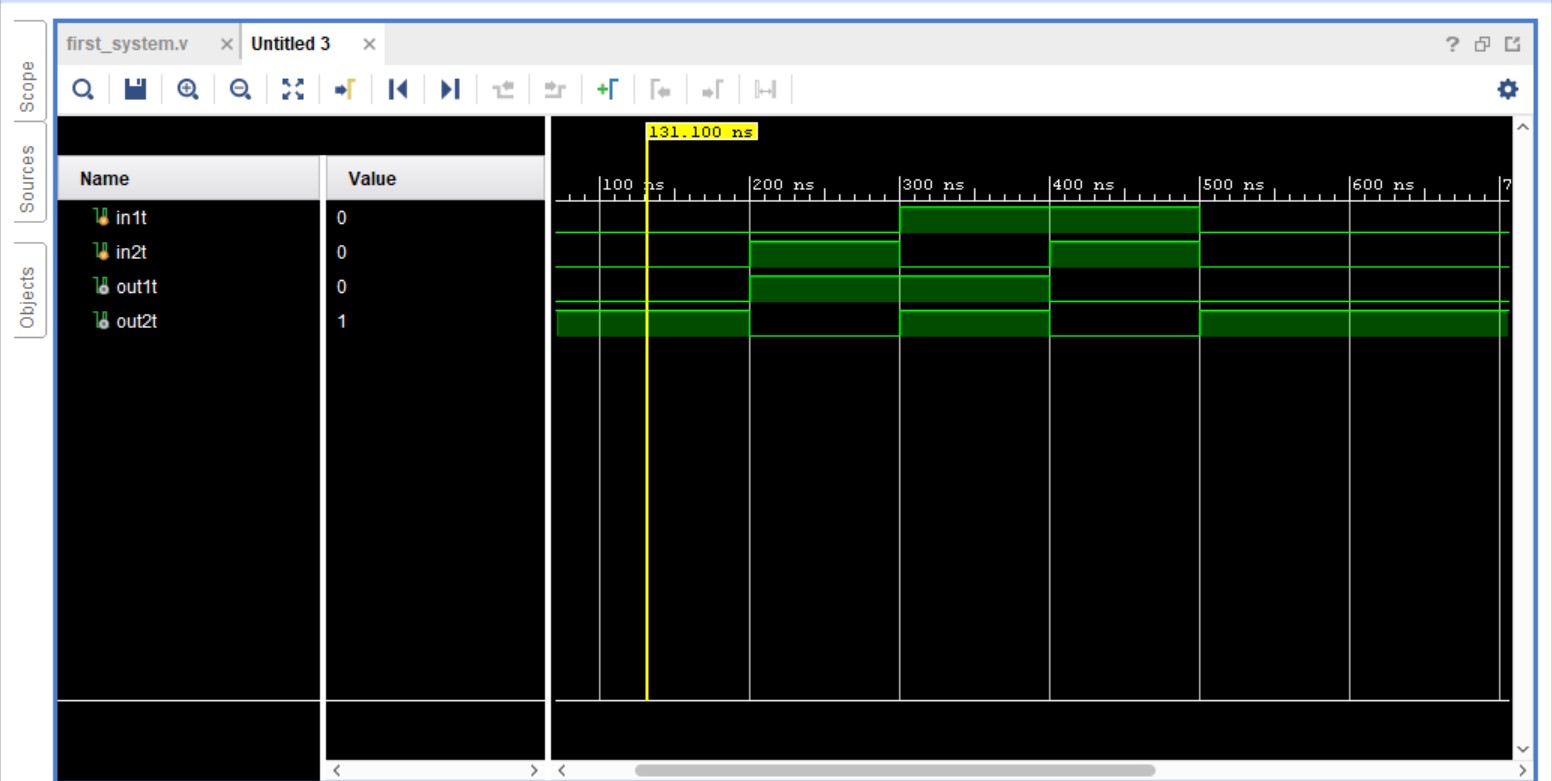

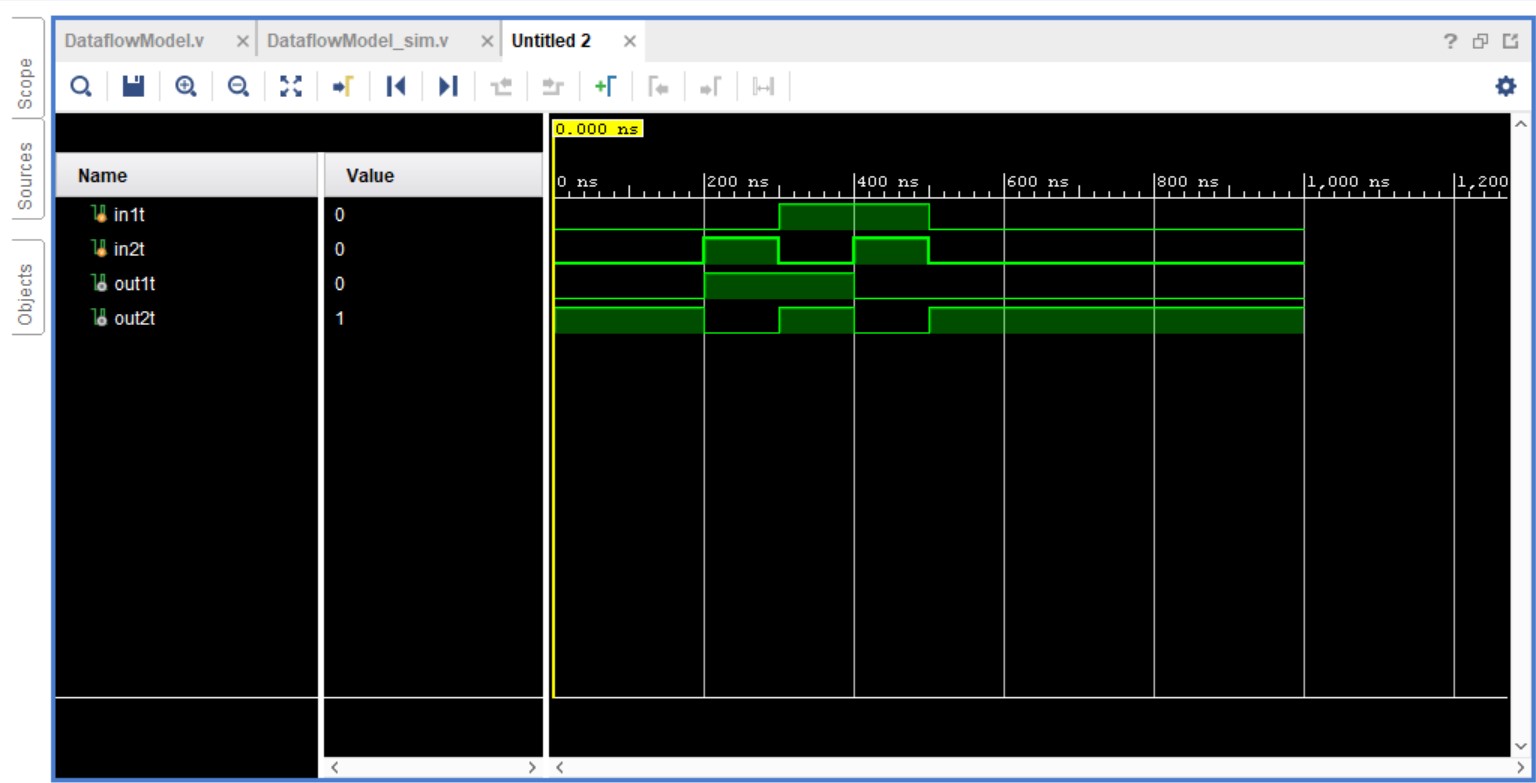

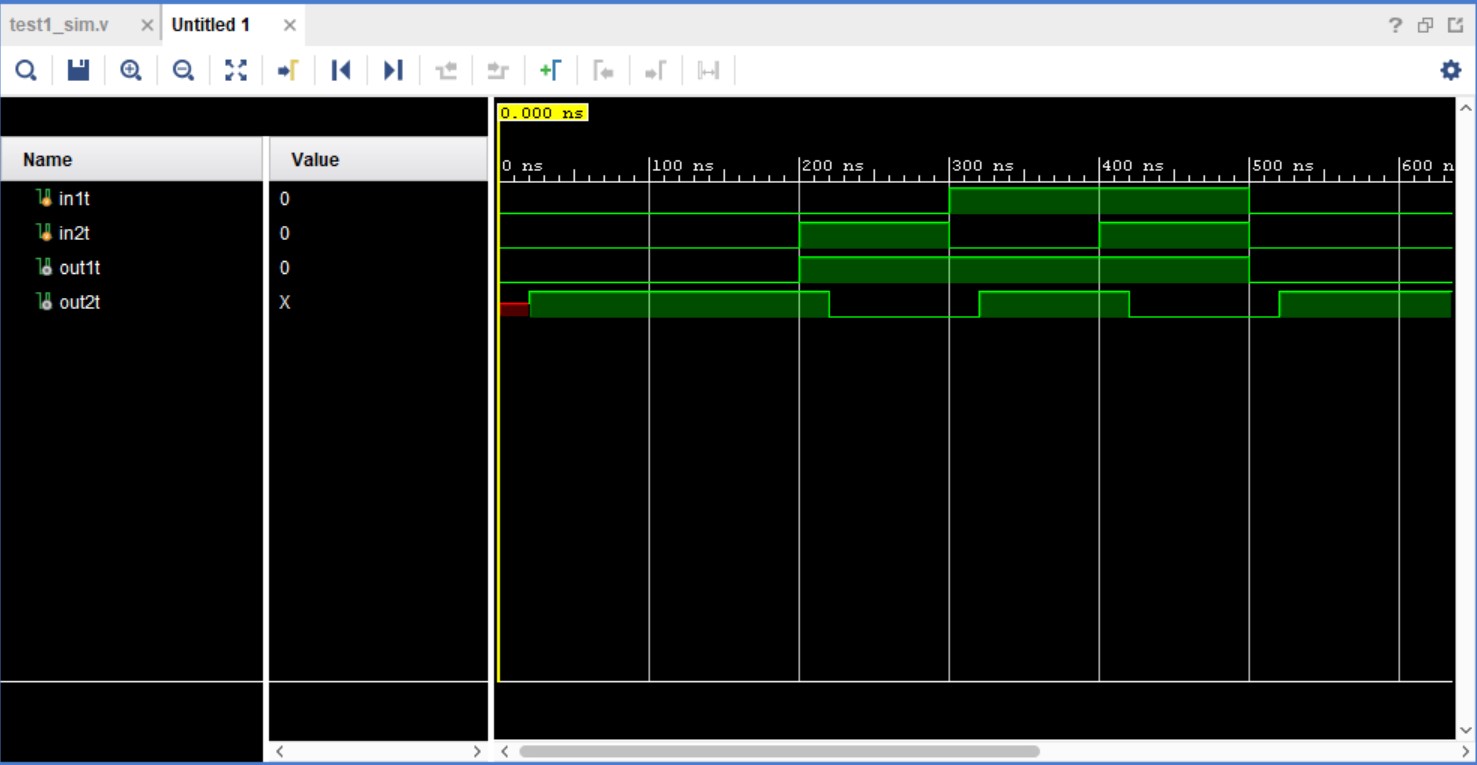

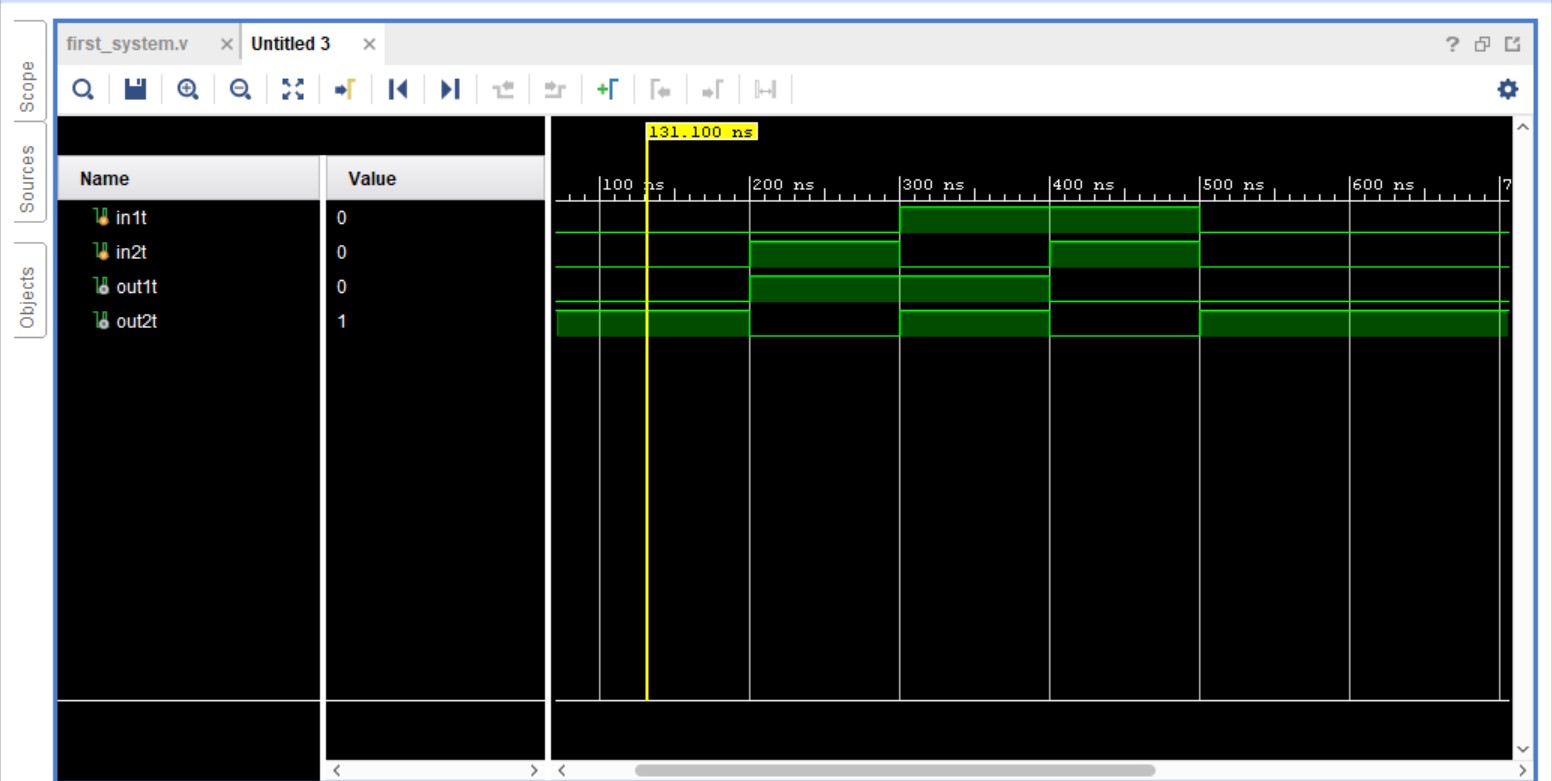

Figure 1.3: Simulation of code from Fig 1.2.

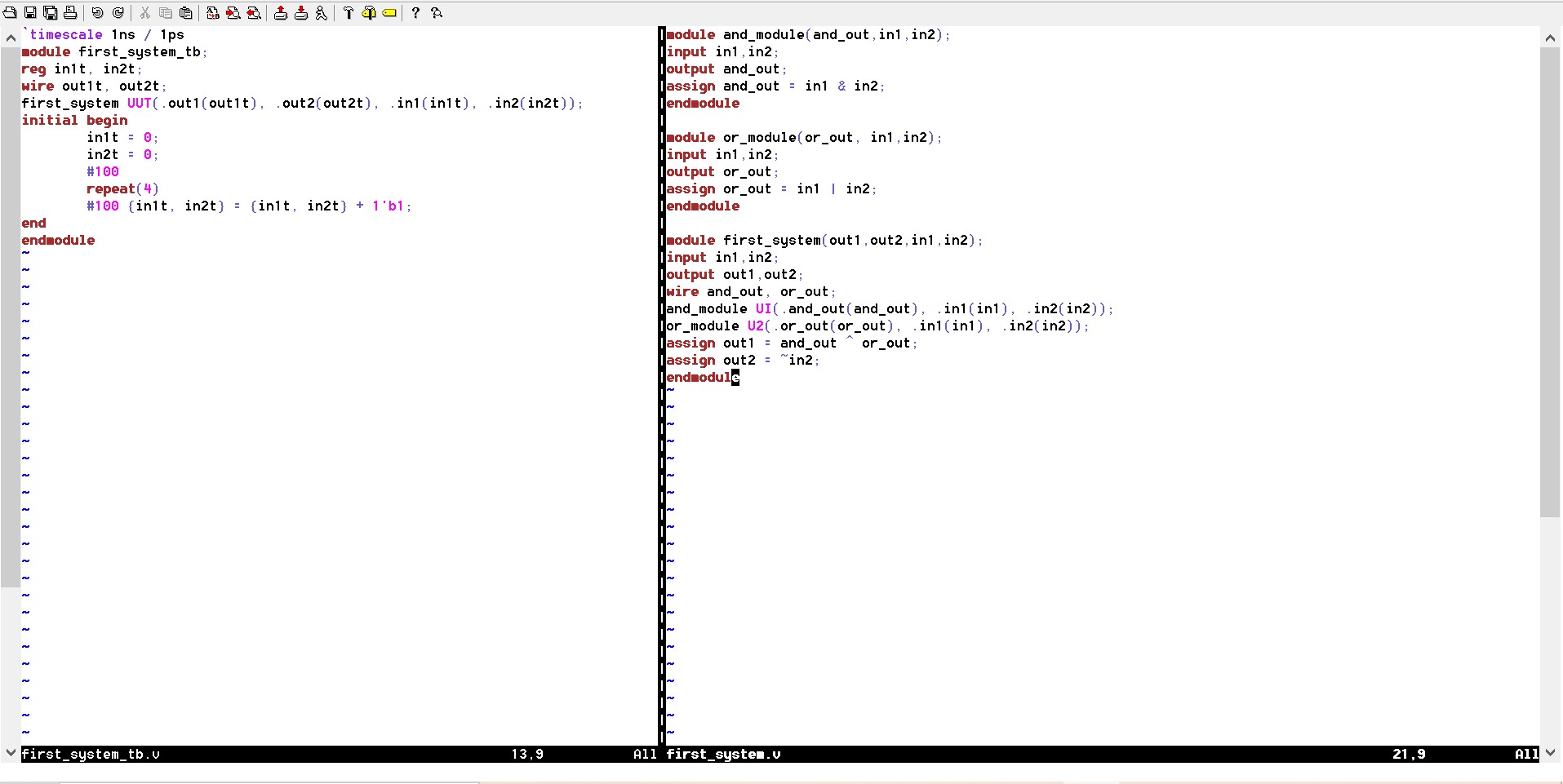

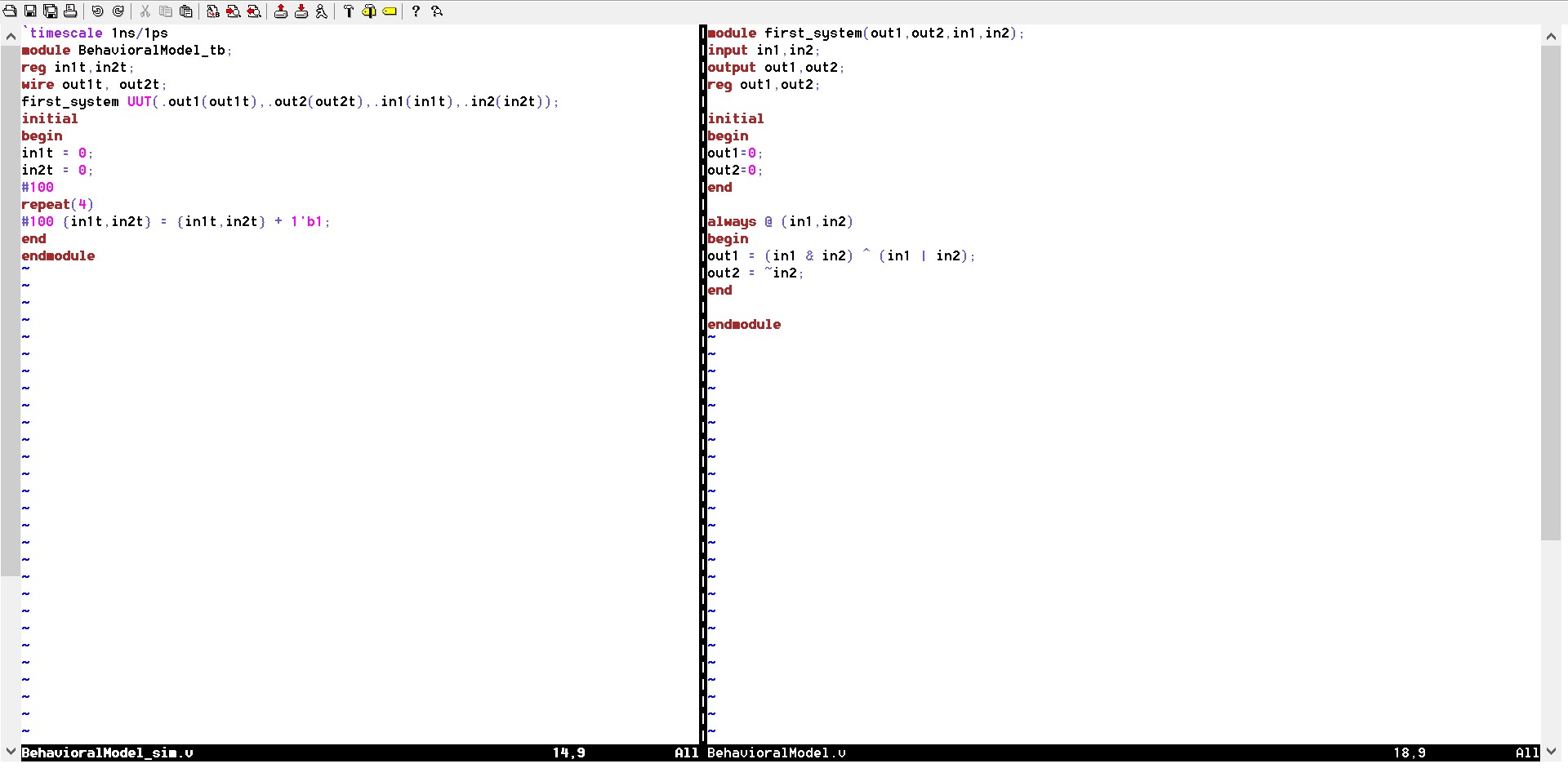

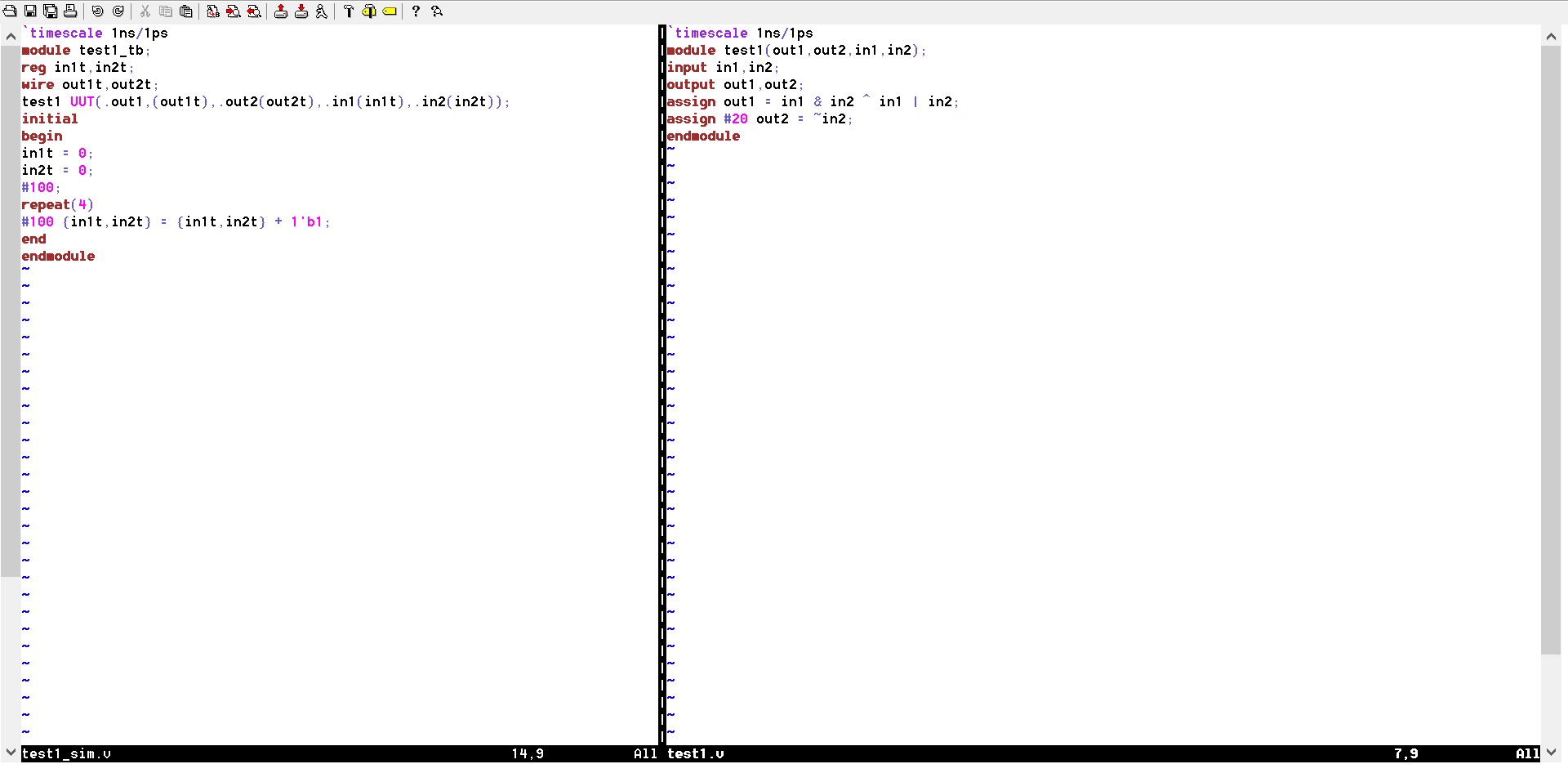

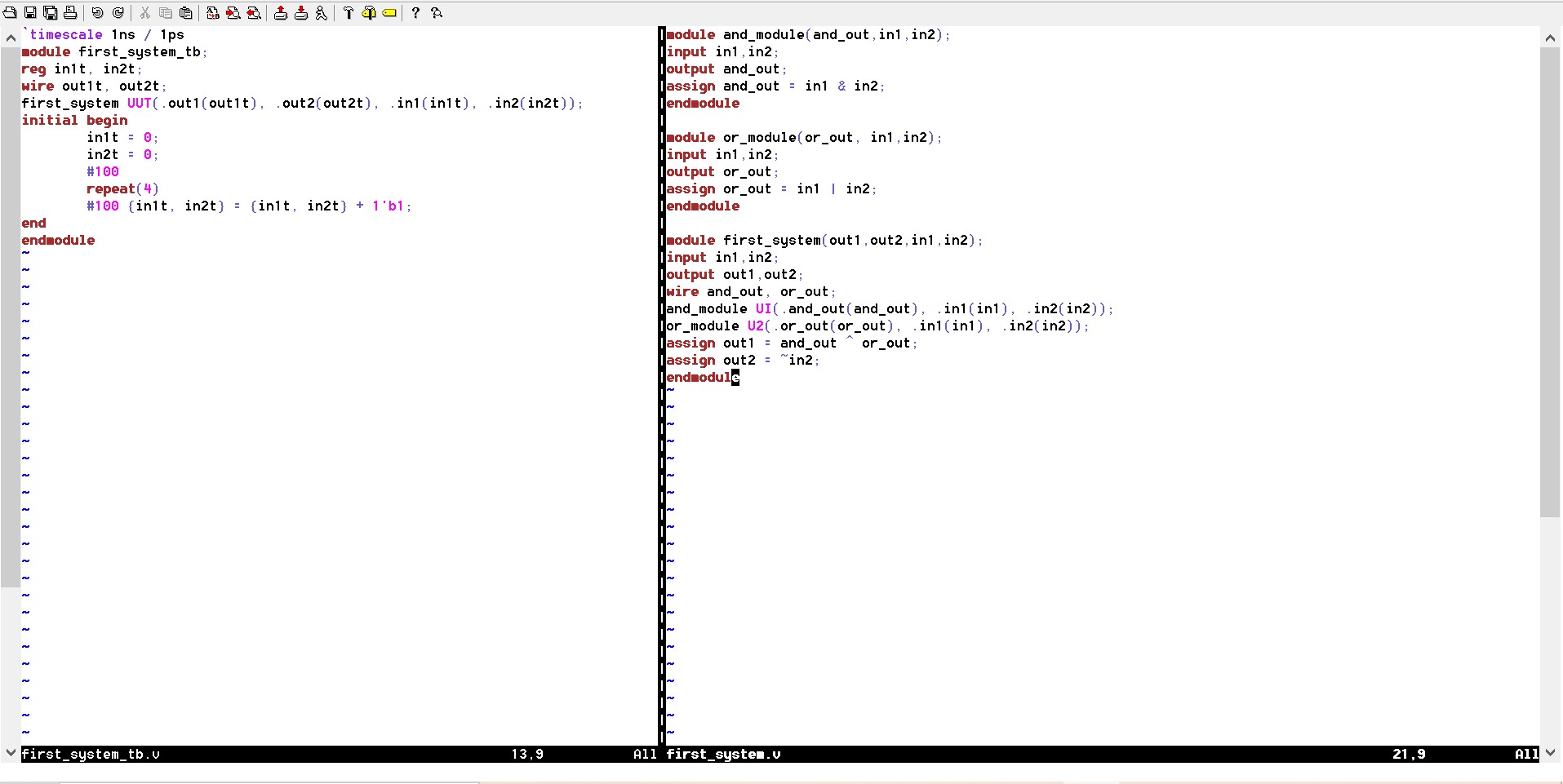

Figure 1.4: Unit under test and test bench code for 2.3.

Figure 1.5: Simulation of code from Fig 1.4.

Figure 5: Unit under test and test bench code for 2.6.

Figure 5.1: Simulation results from running Fig 5.

Figure 1.1: Simulation of code from Fig 1.

Figure 1.2: Unit under test and test bench code for 2.2

Figure 1.3: Simulation of code from Fig 1.2.

Figure 1.4: Unit under test and test bench code for 2.3.

Figure 1.5: Simulation of code from Fig 1.4.

Task

2: Run a simulation to show the difference between blocking and

non-blocking assignment in the example in section 2.4. (20 points)

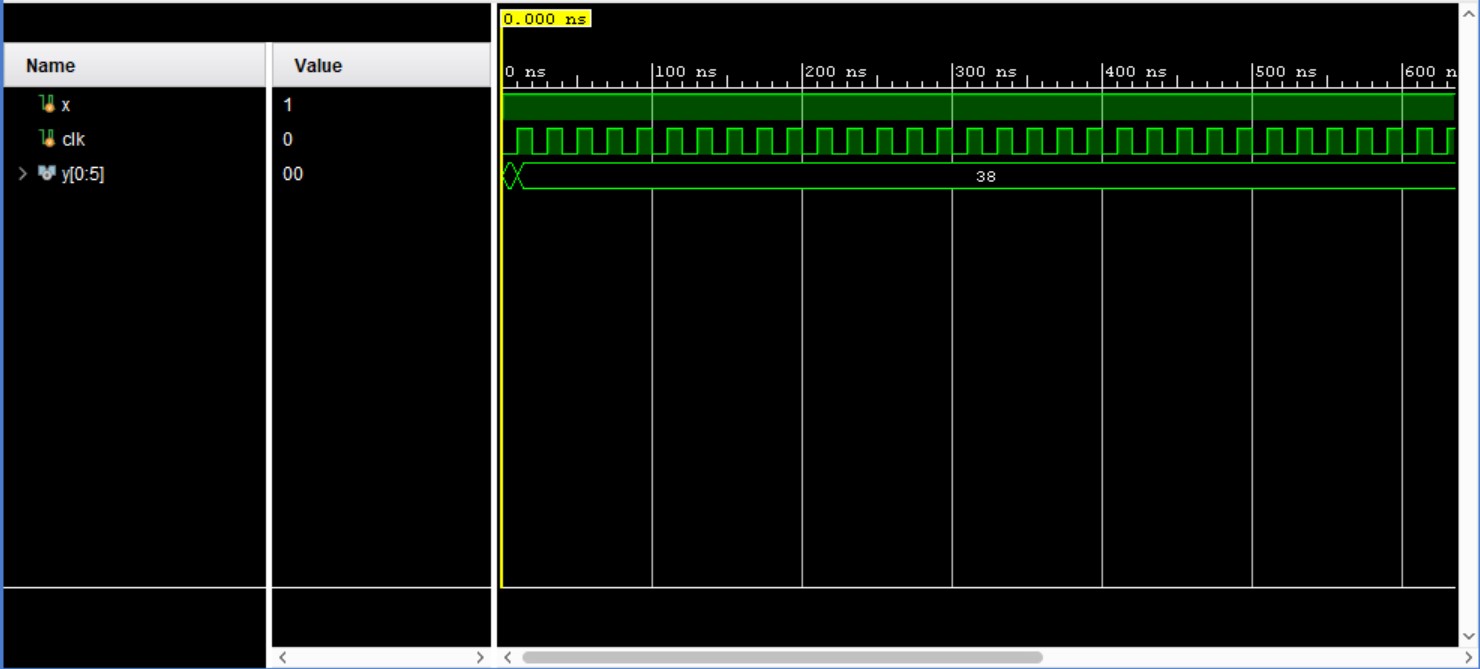

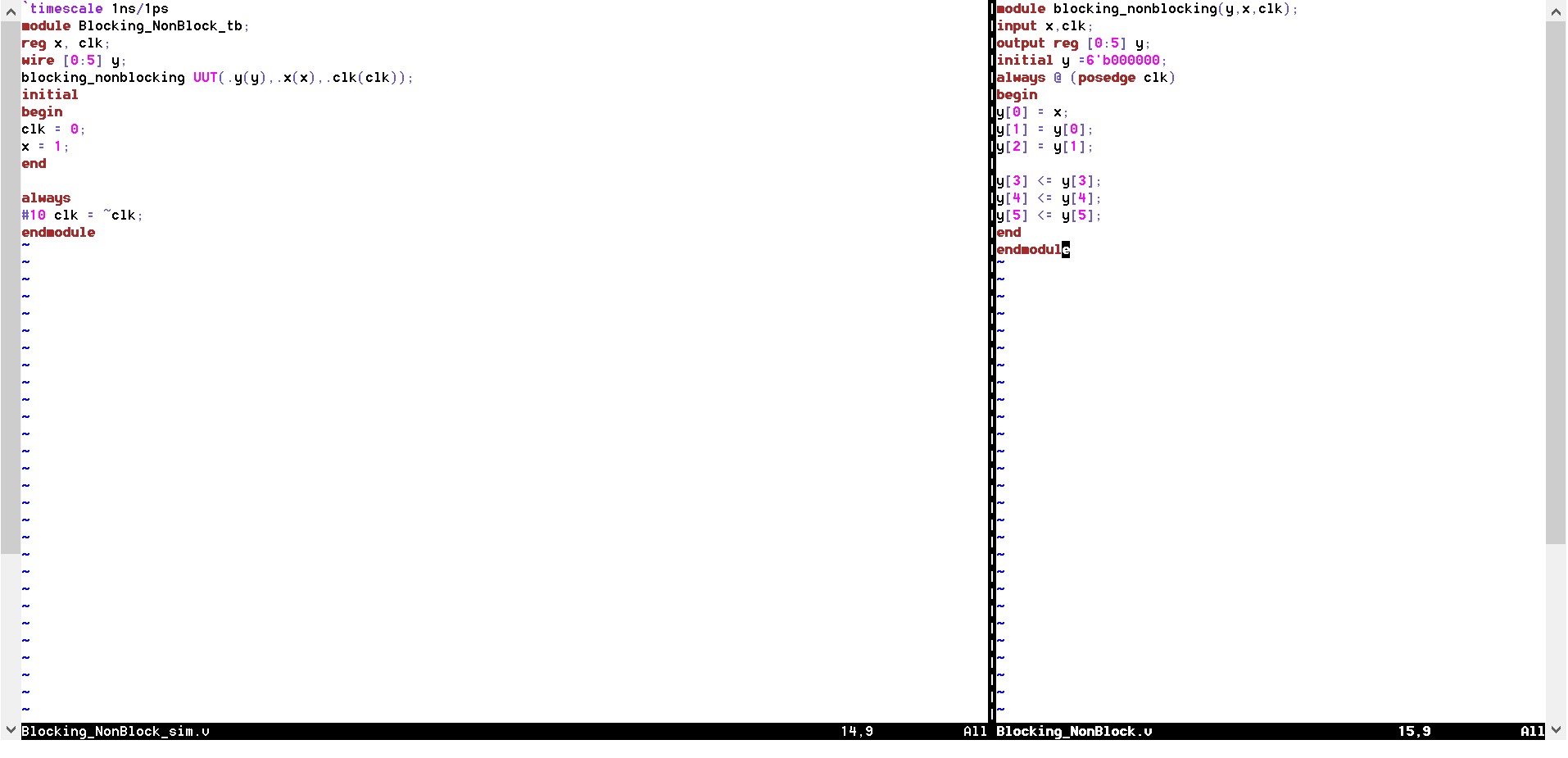

Figure 2: Unit under test and test bench code for blocking and unblocking.

Figure 2: Unit under test and test bench code for blocking and unblocking.

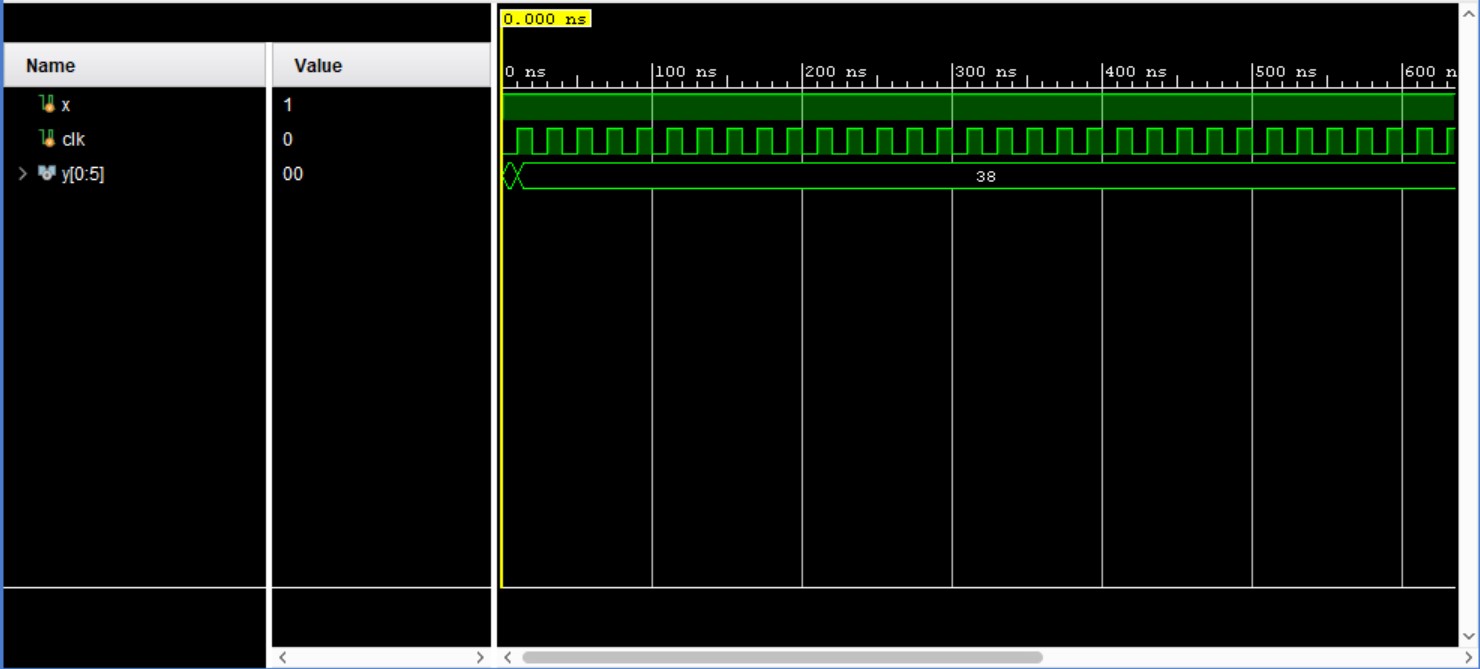

Figure 2.1: Simulation code for the blocking and non-blocking from Fig 2.

Task 3: Repeat teh simulation example in section 2.5. (20 points)

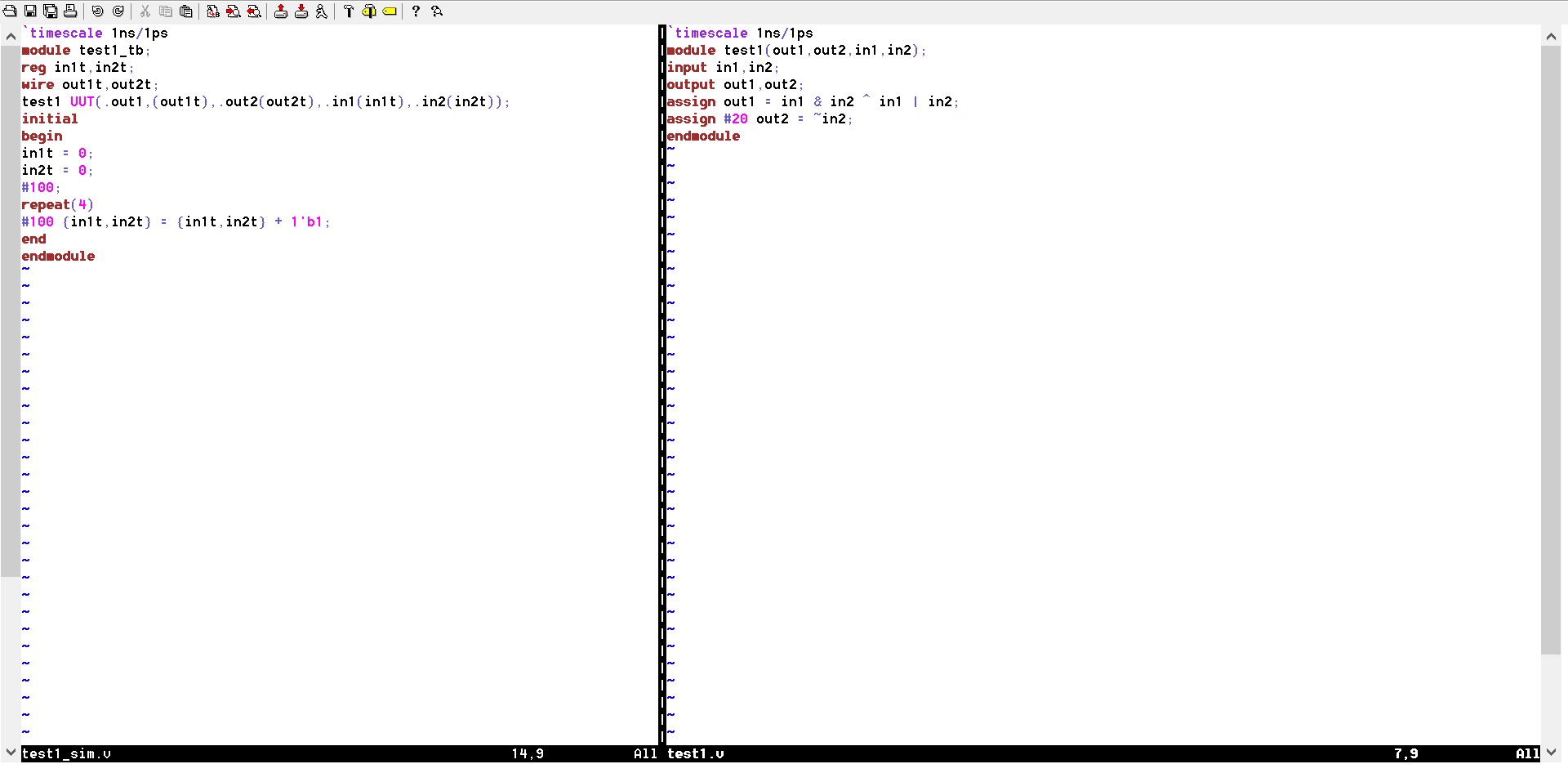

Figure 3: Unit under test and test bench code for 2.5.

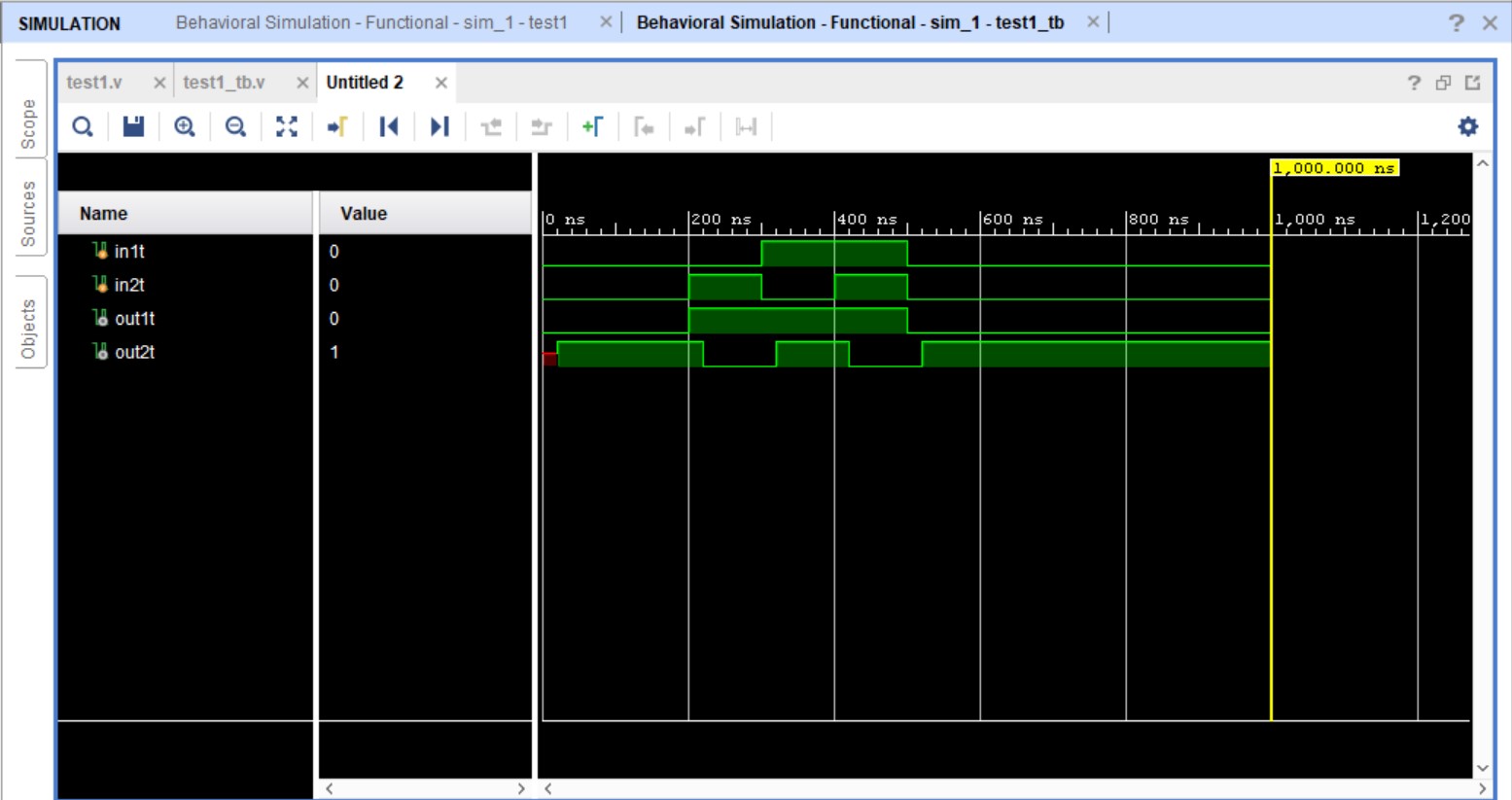

Figure 3.1: Simulation from Fig 3.

Task 4: For the example in section 2.5, move the 20ns delay from line 25 to line 24 and run the simulation . (20 points)

Figure 4: Unit under test and test bench code for 2.5 with 20ns moved.

Figure 4.1: Simulation from Fig 4.

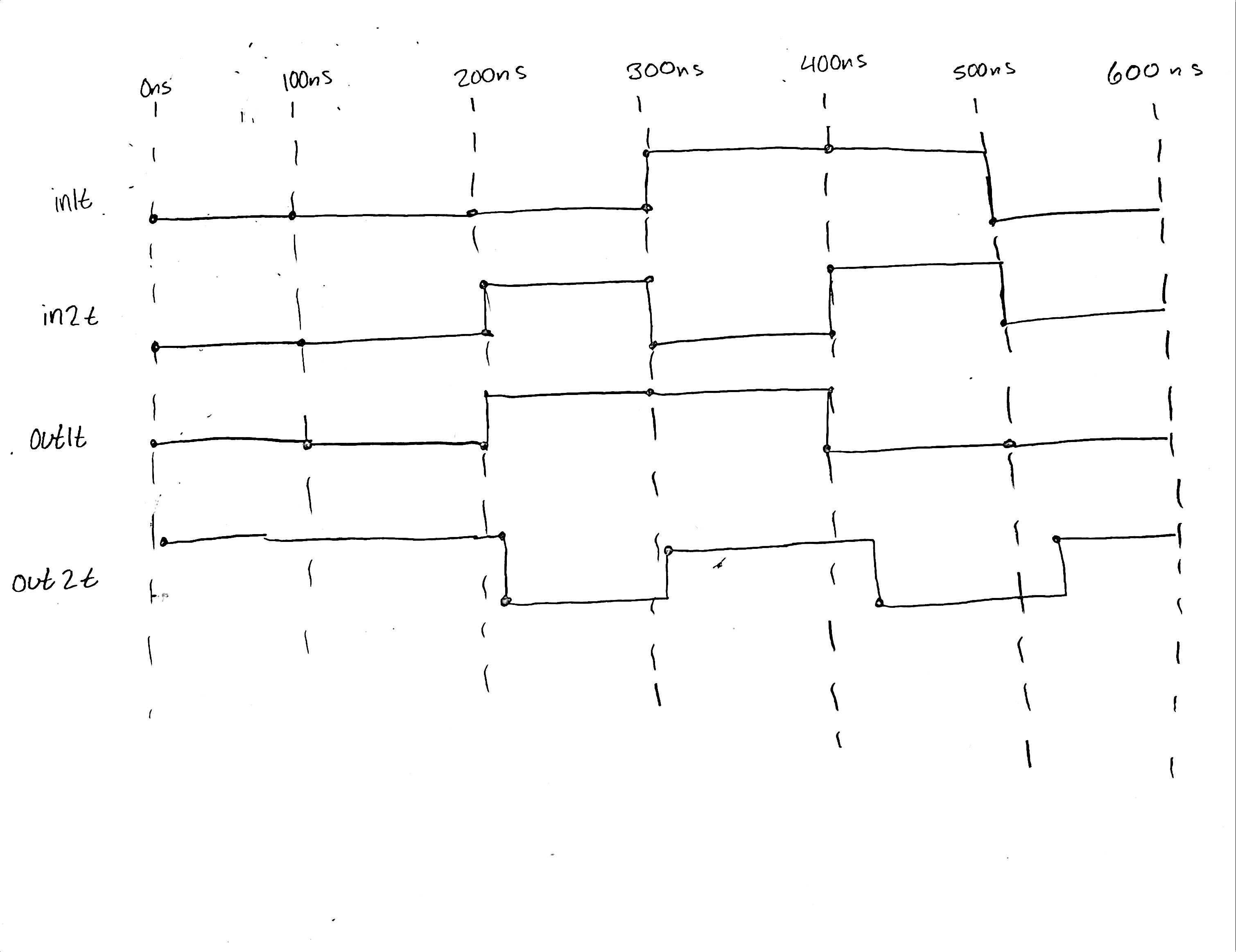

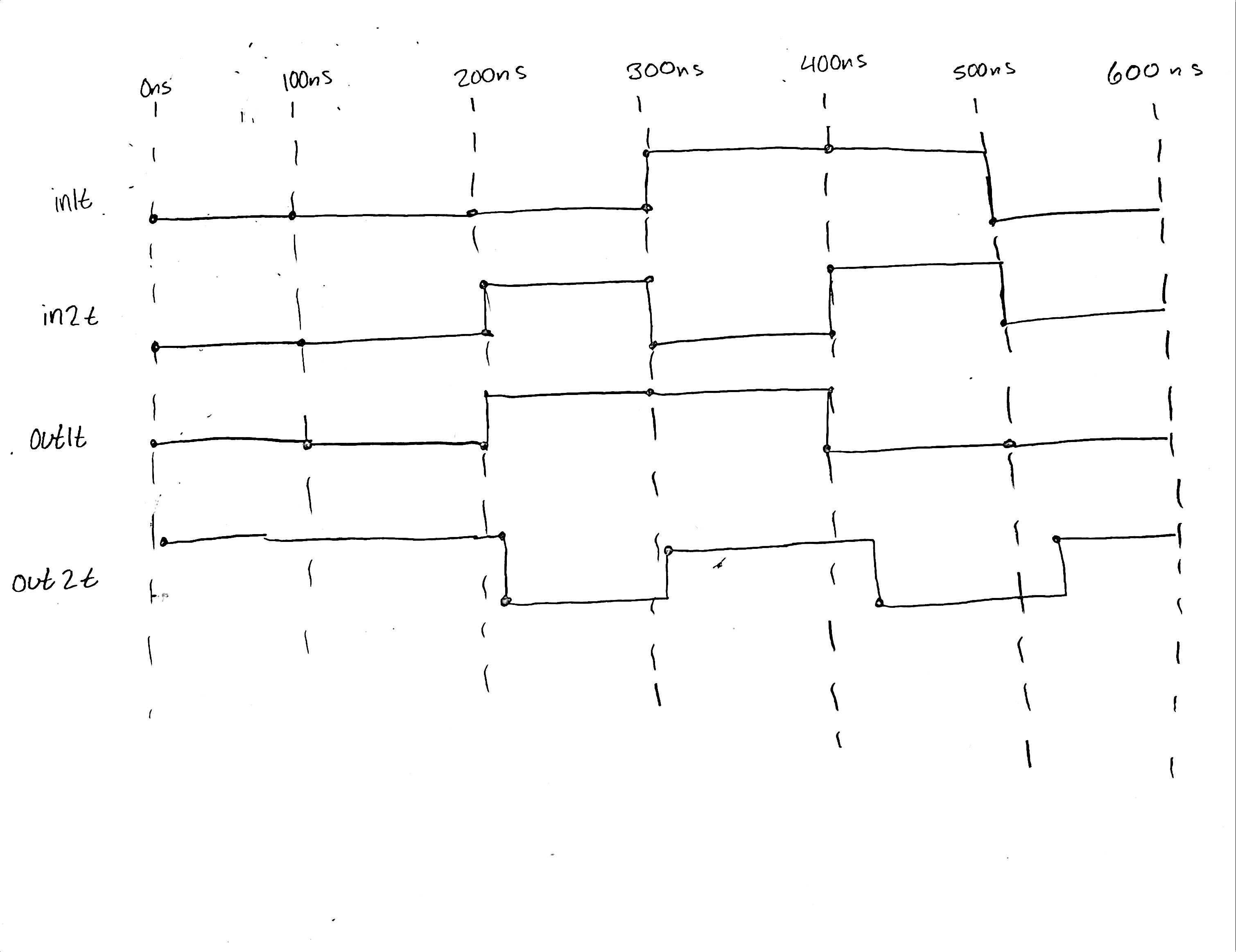

Figure 4.2: Hand drawling of the timing diagram.

Task 5: Use gvim and vivado, repeat the example in 2.6. Post the gvim window and vivado simulation window for credit. (20 points)

Figure 2: Unit under test and test bench code for blocking and unblocking.

Figure 2: Unit under test and test bench code for blocking and unblocking.

Figure 2.1: Simulation code for the blocking and non-blocking from Fig 2.

Task 3: Repeat teh simulation example in section 2.5. (20 points)

Figure 3: Unit under test and test bench code for 2.5.

Figure 3.1: Simulation from Fig 3.

Task 4: For the example in section 2.5, move the 20ns delay from line 25 to line 24 and run the simulation . (20 points)

Figure 4: Unit under test and test bench code for 2.5 with 20ns moved.

Figure 4.1: Simulation from Fig 4.

Figure 4.2: Hand drawling of the timing diagram.

Task 5: Use gvim and vivado, repeat the example in 2.6. Post the gvim window and vivado simulation window for credit. (20 points)

Figure 5: Unit under test and test bench code for 2.6.

Figure 5.1: Simulation results from running Fig 5.