Homework 1 - Basics

CE 433 Embedded Devices

2024 SpringName: Joel Nash

Email:

jxnash@gmail.com

Task 1. Use gvim and Vivado to simulate the examples in sections 2.1, 2.2, and 2.3. Post snapshots of gvim windows and vivado simulation results in your report. You must create test benches for your simulations. (20 points)

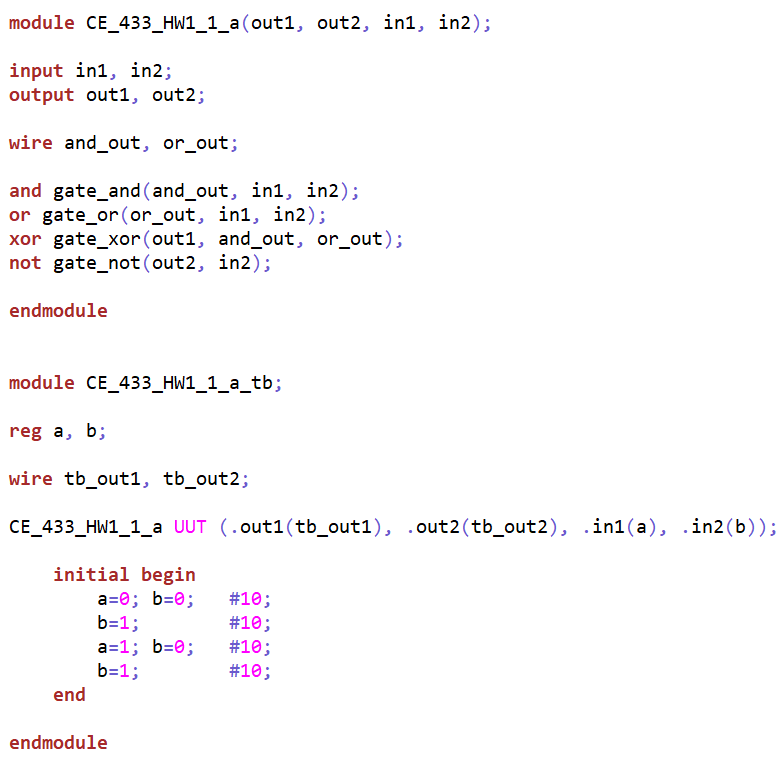

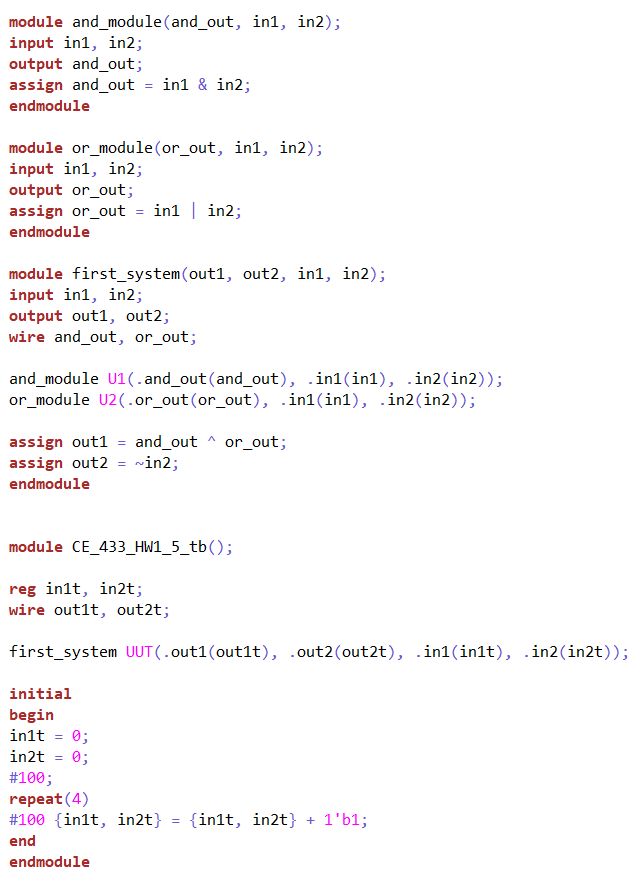

Example 2.1 Structural Modeling.

Figure 1: Gvim code for 2.1 with test bench.

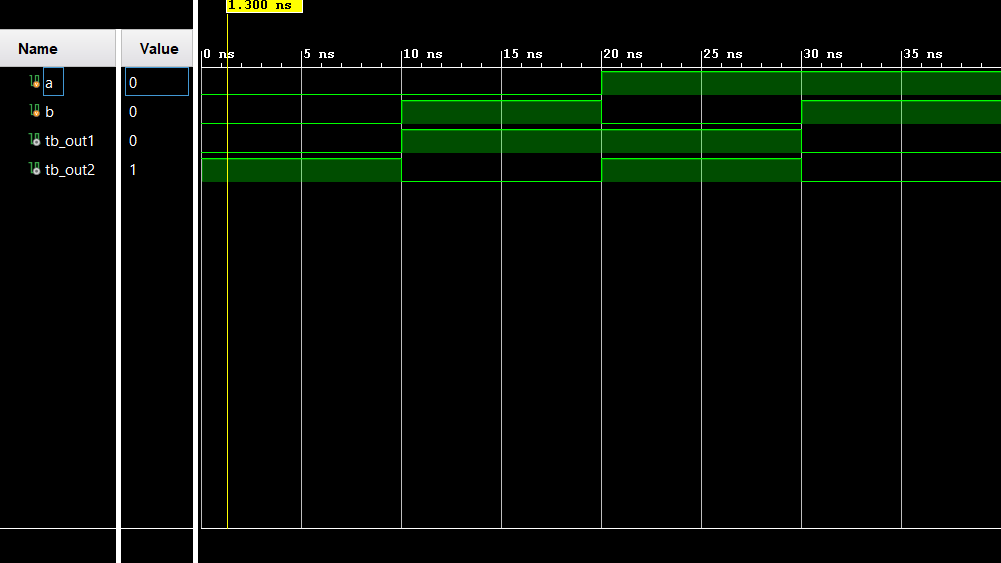

Figure 2: Vivado Simulation of 2.1.

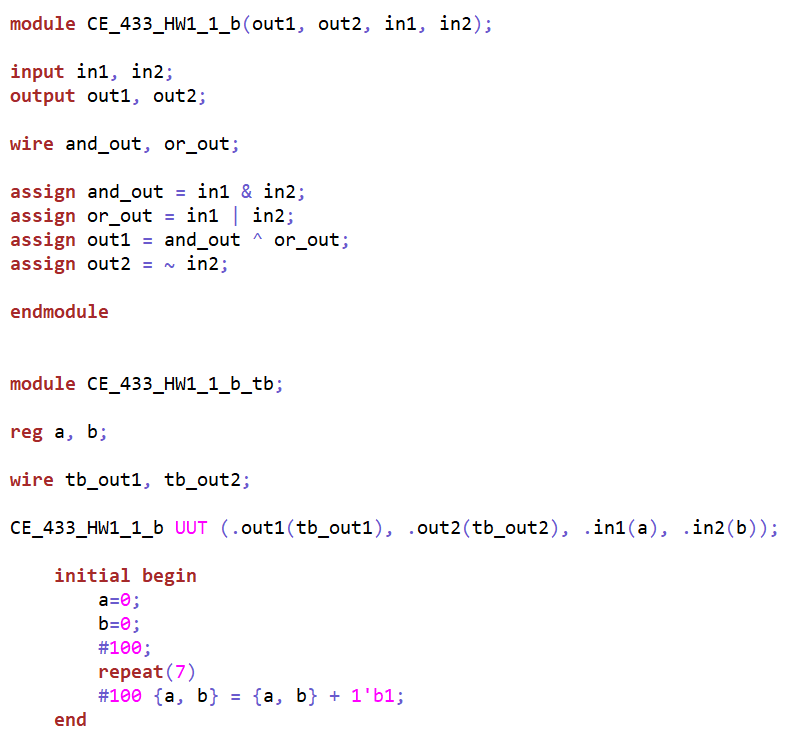

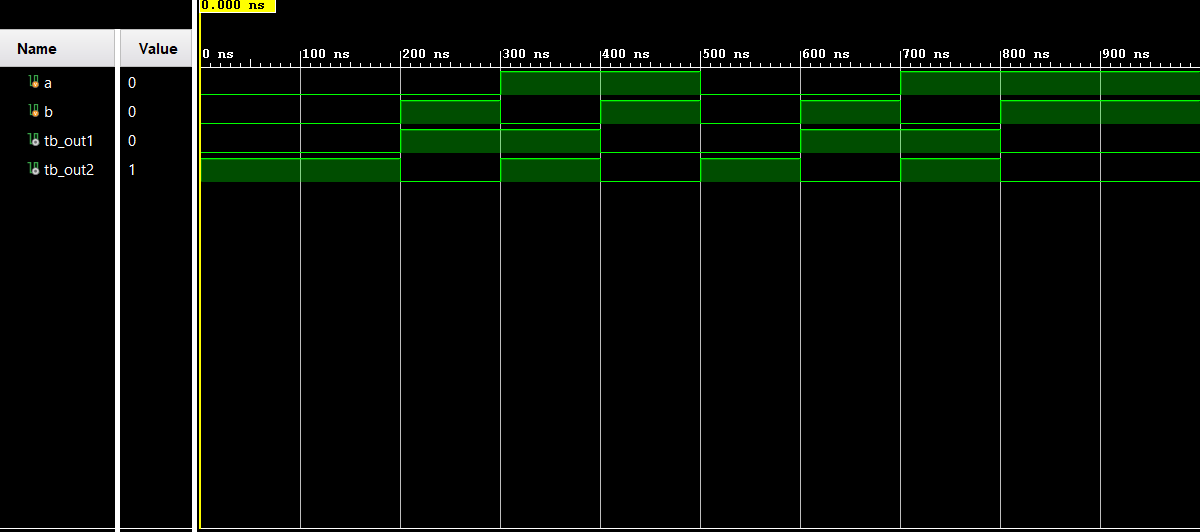

Example 2.2 Data flow Modeling.

Figure 3: Gvim code using logic operators in example 2.2.

Figure 4: Vivado simulation for example 2.2.

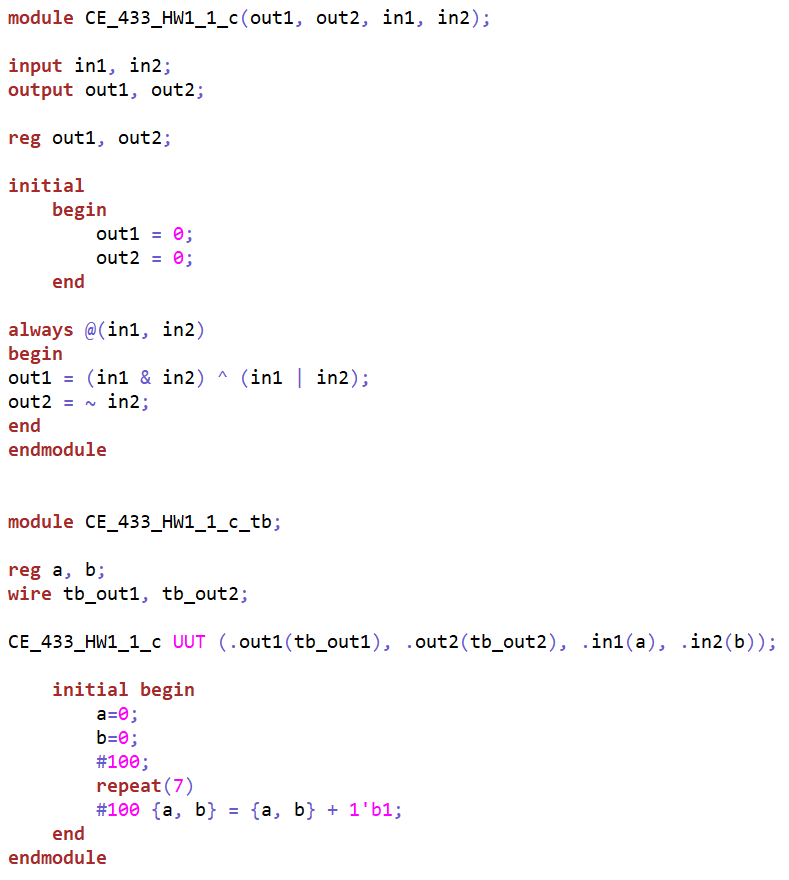

Example 2.3 Behavioral Modeling.

Figure 5: Gvim code utilizing the 'always' procedural block in Verilog.

Figure 6: Vivado simulation of example 2.3.

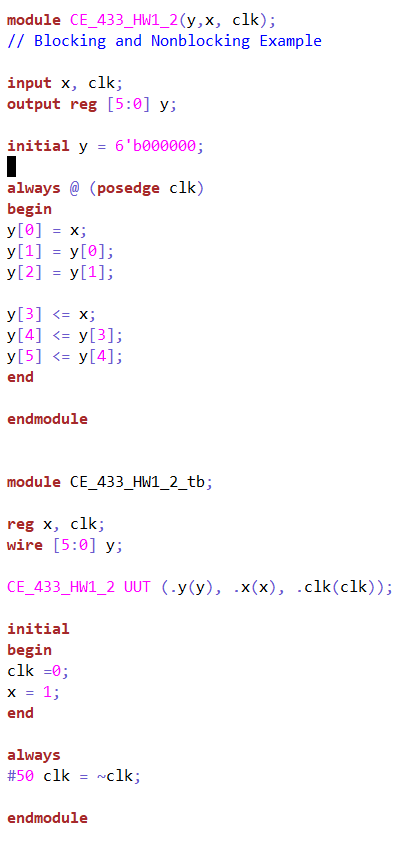

Task 2. Simulate to show the difference between blocking and non-blocking assignments in the example in section 2.4. (20 points)

Example 2.4: Blocking and Non-Blocking in Behavioral Modeling.

Figure 7: Gvim code demonstrating the blocking and non-blocking assignments in a behavior model (example 2.4).

Figure 8: Vivado simulation of example 2.4.

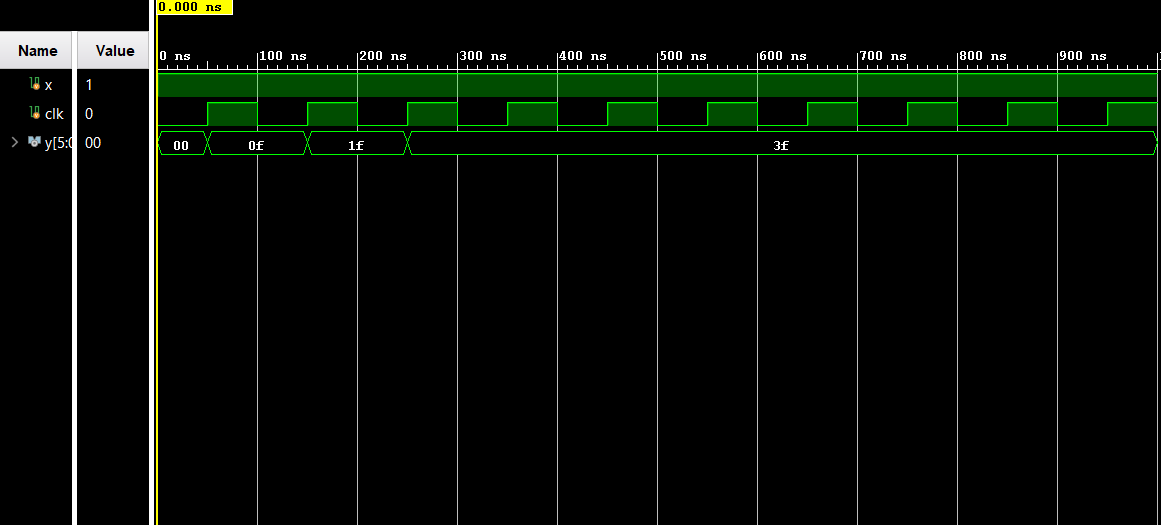

Task 3. Repeat the simulation example in section 2.5. (20 points)

Example 2.5 Timing and Delaying Modeling.

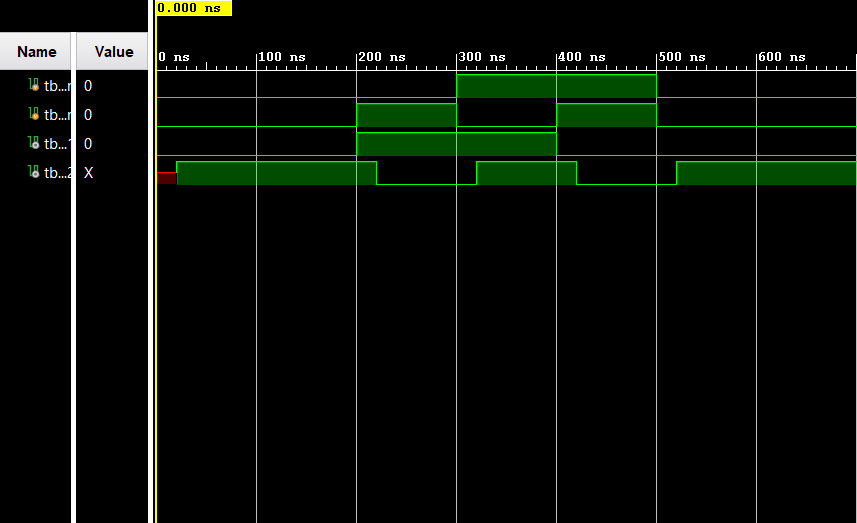

Figure 9: Gvim code showing the use of the 20NS delay, before assigning 'out2'.

Figure 10: Vivado simulation, showing the result from the 20NS delay on 'out2' in example 2.5.

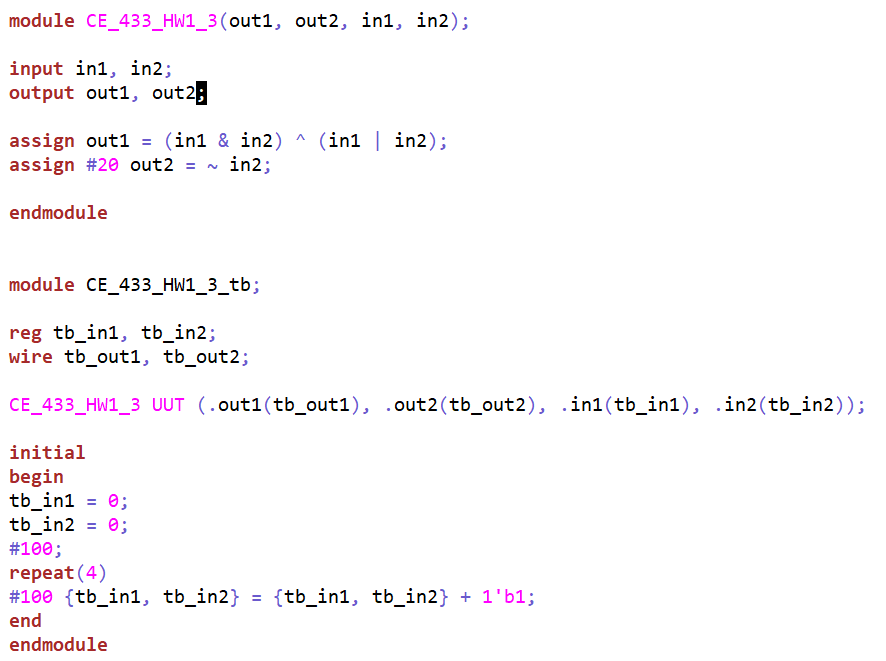

Task 4. For the example in section 2.5, move the 20 NS delay from Line 25 to Line 24 and run the simulation. (20 points)

Example 2.5 (part 2) Timing and Delay in Modeling.

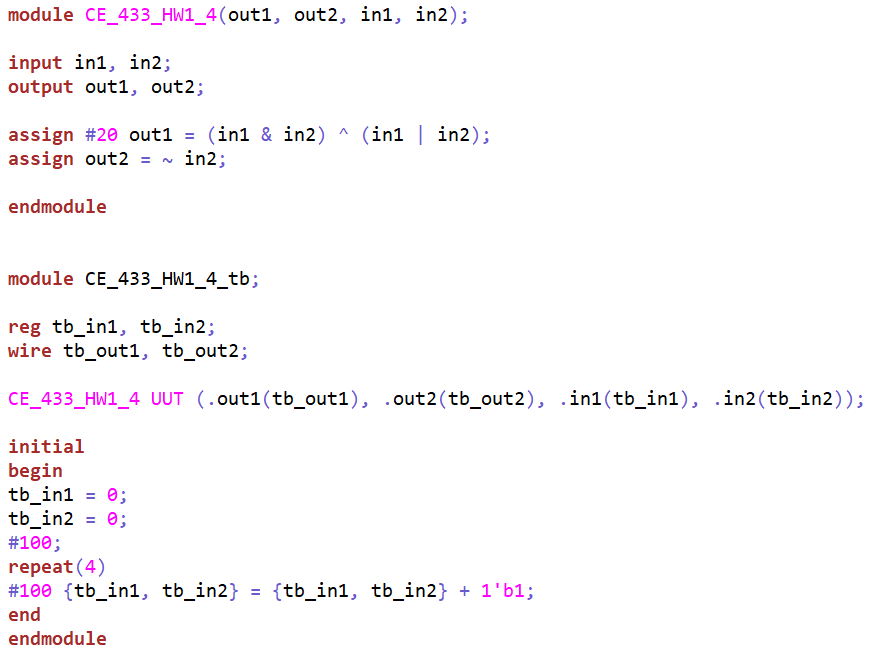

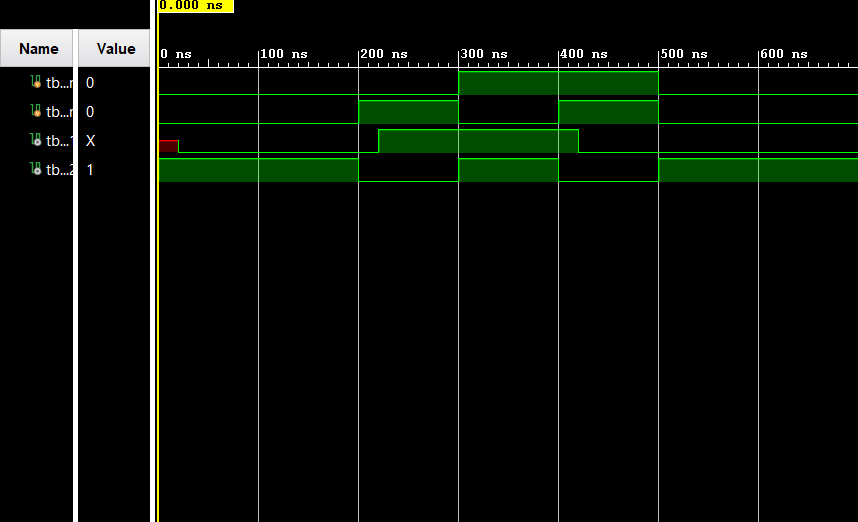

Figure 11: Gvim code which demonstrates the 20NS time delay like example 2.5 (part 1). with the time delay before 'out1' instead.

Figure 12: Vivado simulation showing the 20NS time delay on the output 'out1'.

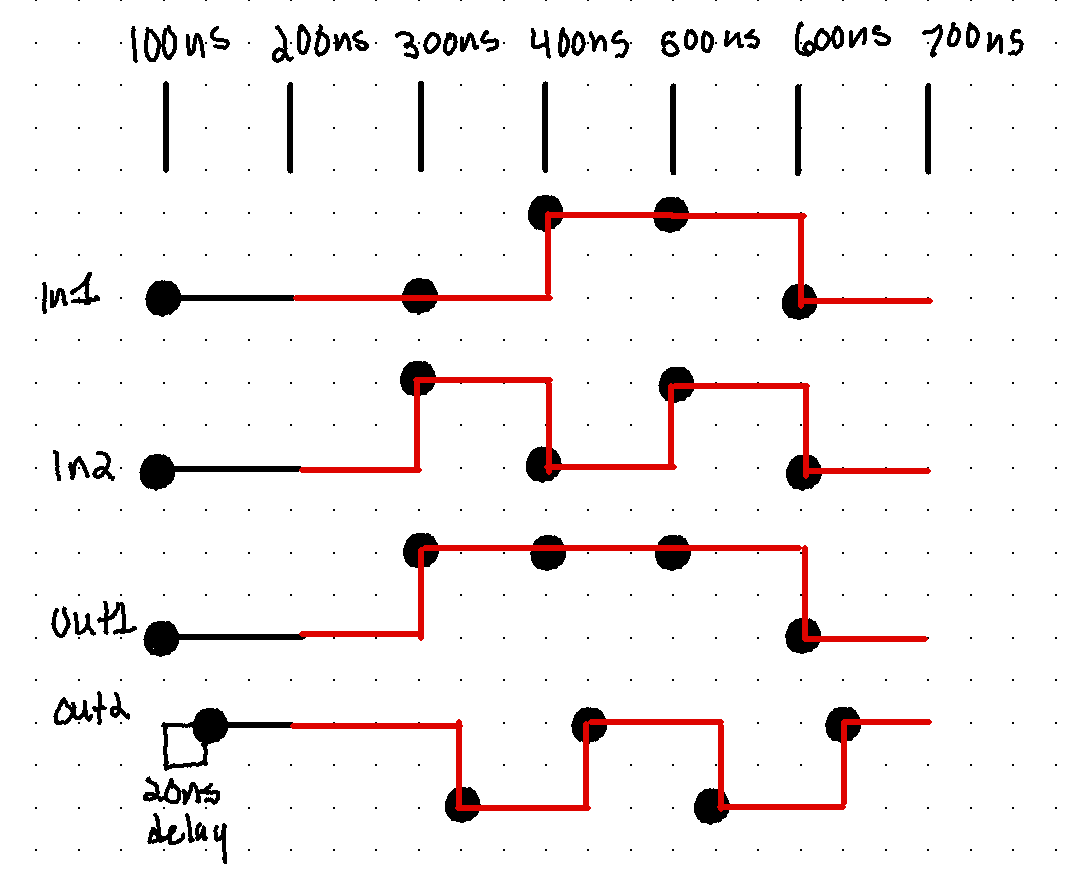

Hand-draw the timing diagram on a piece of paper as follows. Take a picture of the drawing and insert it into your report as a picture.

Figure 13: Hand drawing, (artist: Joel Nash), depicting the influence of the 20NS time delay on the outputs.

Task 5. Use gvim and vivado, repeat the example in section 2.6. Post the gvim windows and the vivado simulation windows for credit. (20 points)

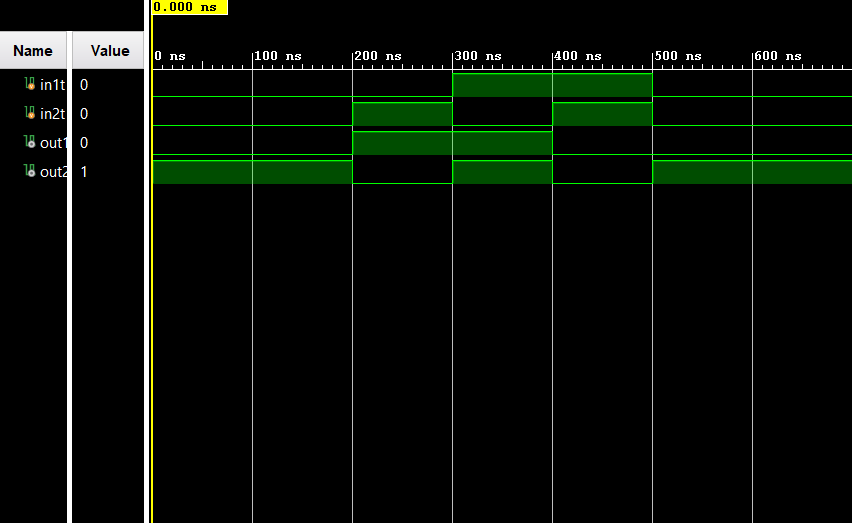

Example 2.6 Hierarchical Module Representation.

Figure 14: Gvim code demonstrating the hierarchies within using multiple modules in one '.v' file.

Figure 15: Vivado simulation of example 2.6.