SAR Projext

ENGR 338

James Ferguson

Introduction

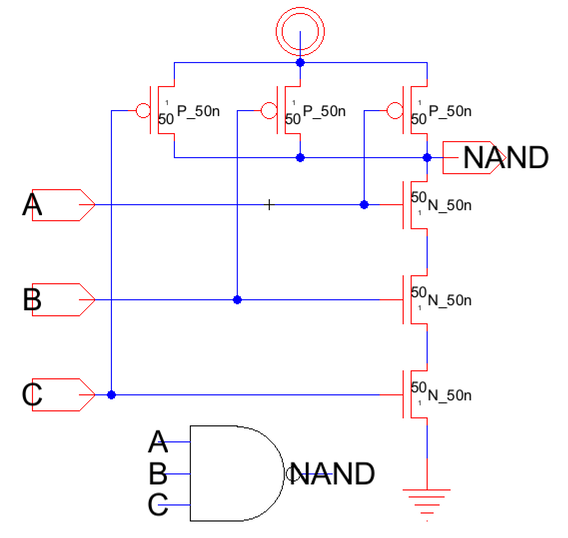

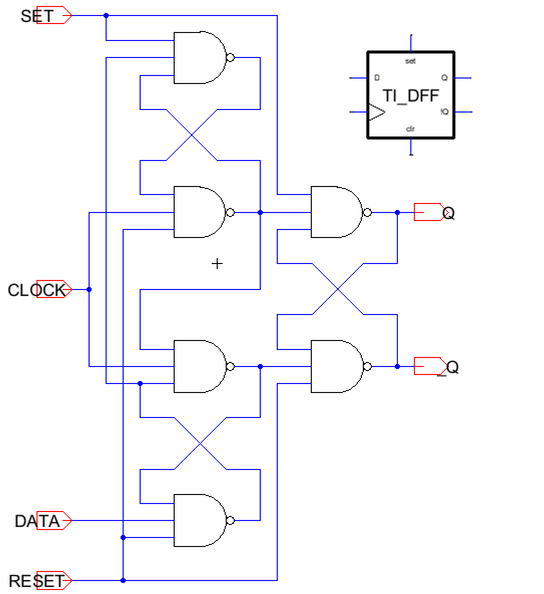

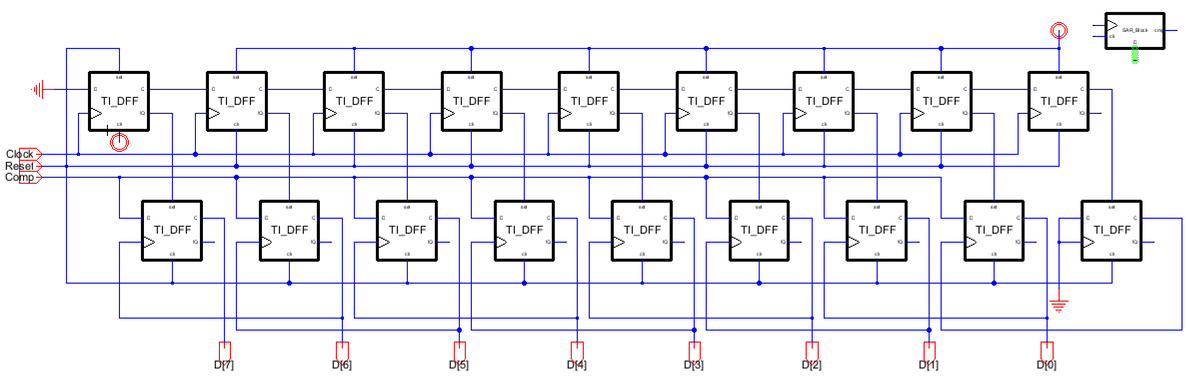

The goal of this project is to design the Successive approximation (SAR) block for a SAR analog to digital converter at the schematic level. This was done in GNU Electric VLSI with simulations performed in LTspice using 50nm technology.

Methods

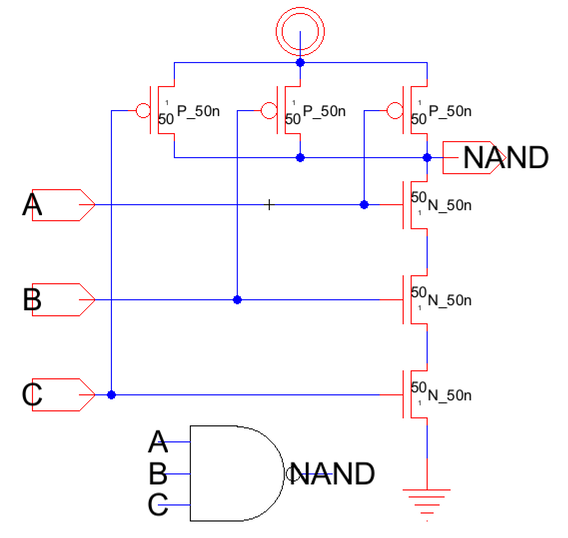

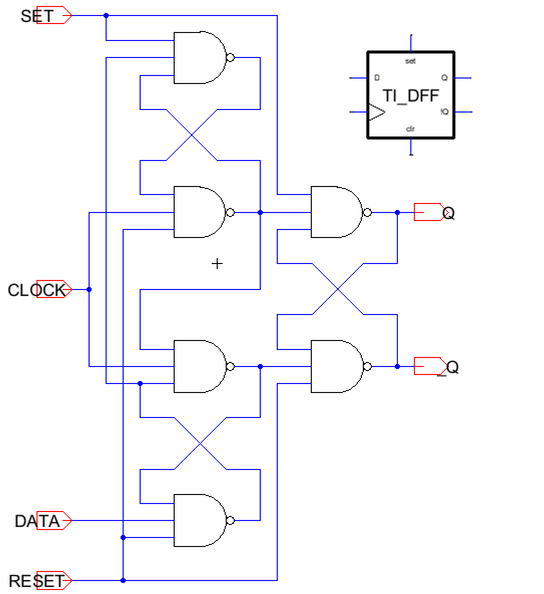

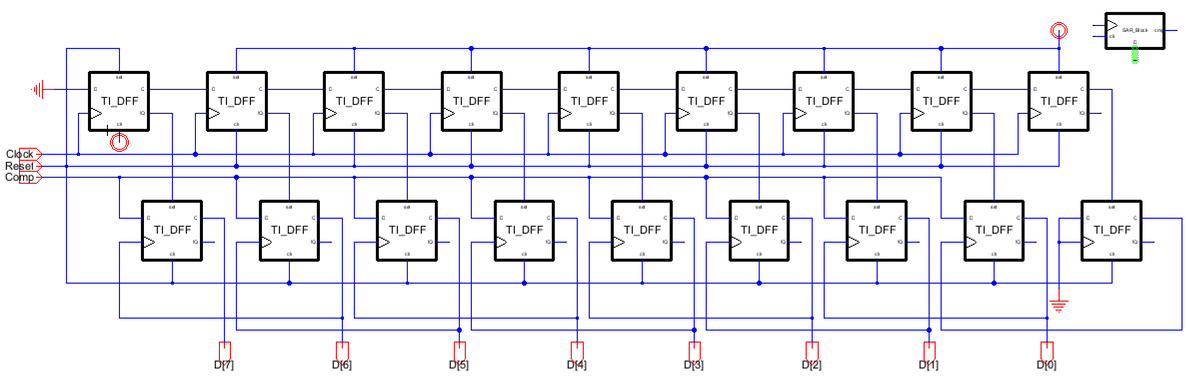

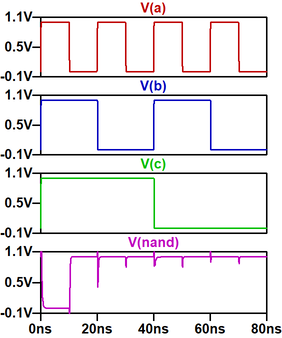

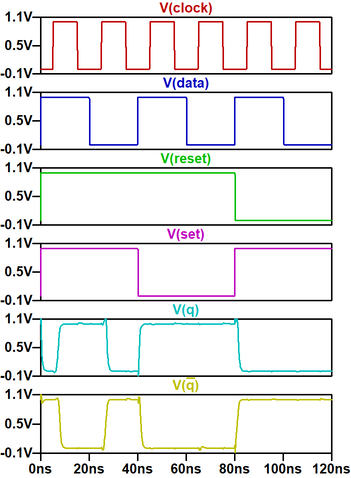

The following shows the schematics for the 3 input NAND gate, the TI DFF and the SAR block.

Results

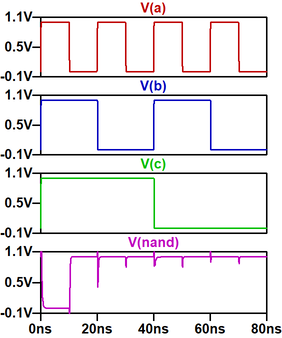

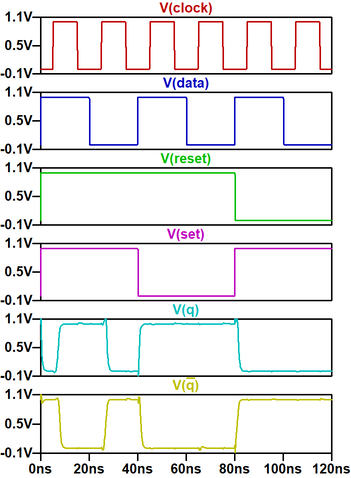

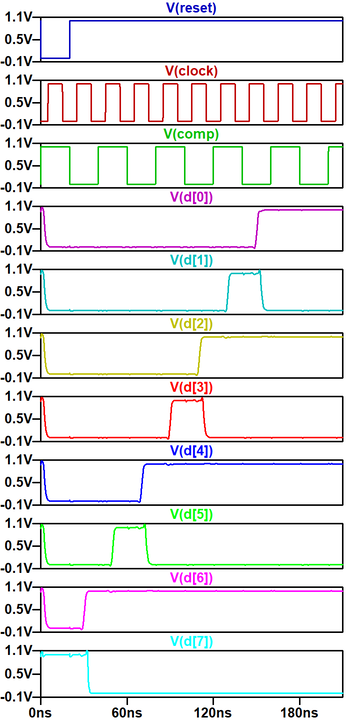

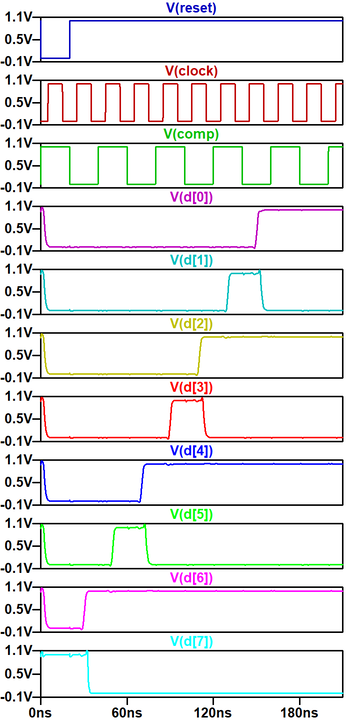

The following shows the simulation results for each of the schematics.

Discussion

The SAR block functions as expected and is ready to be connected to a opamp, DAC and sample and hold circuits to create a working SAR ADC.