ENGR 433- HW 1 2024 Fall

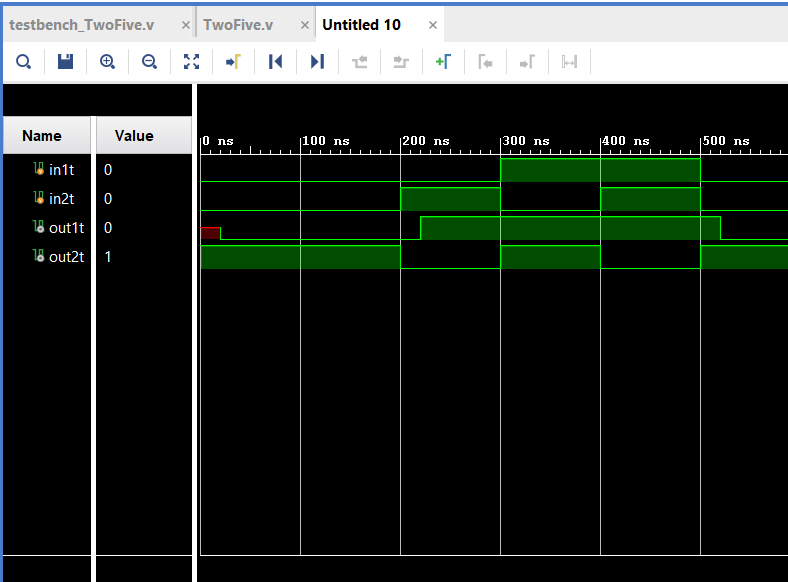

Name: Ian Van Horn

Email: imvanhorn1@gmail.com

Hoemwork 1 Verilog and FPGA basics

Task 1: 2.1, 2.2, 2.3 (20 points).

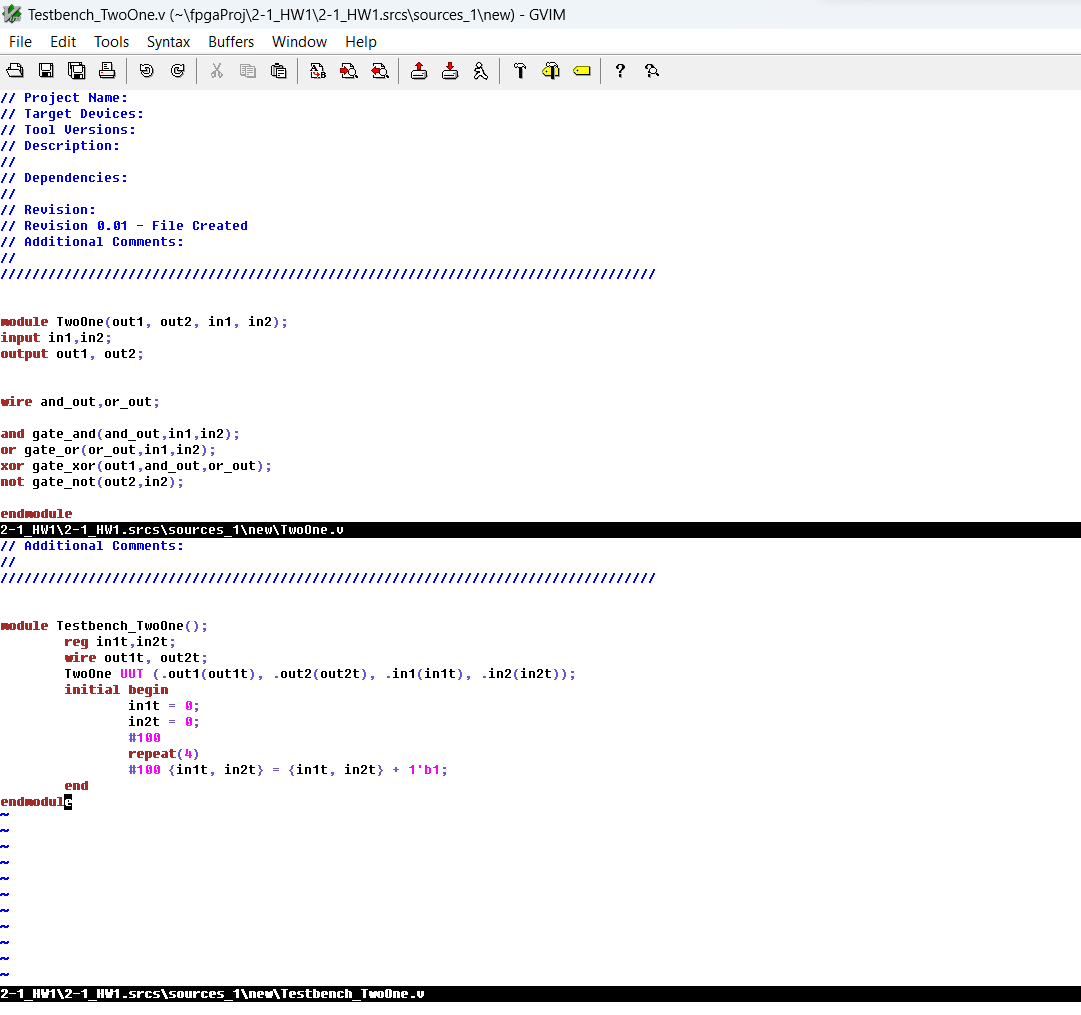

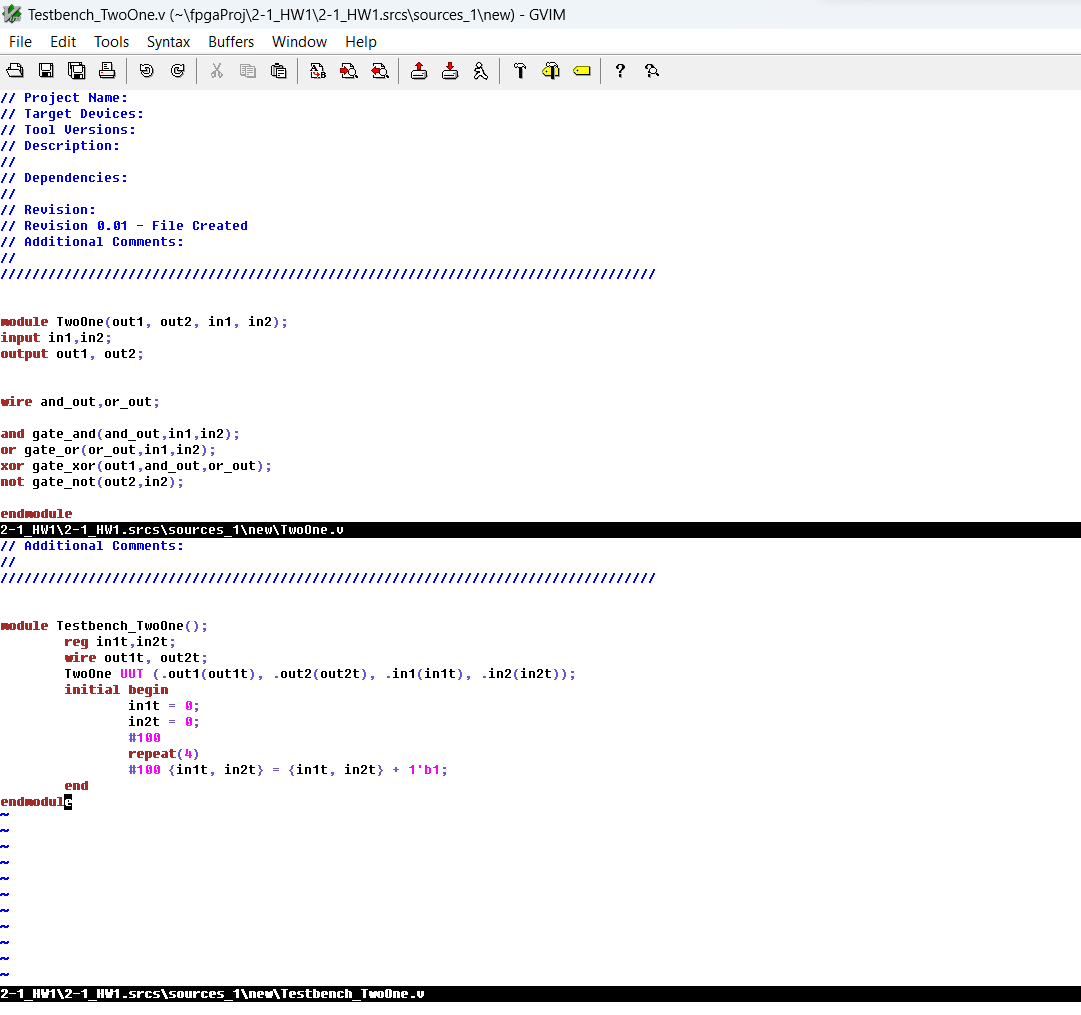

Figure 1.1: Gvim code for example 2.1 (Structural Modeling)

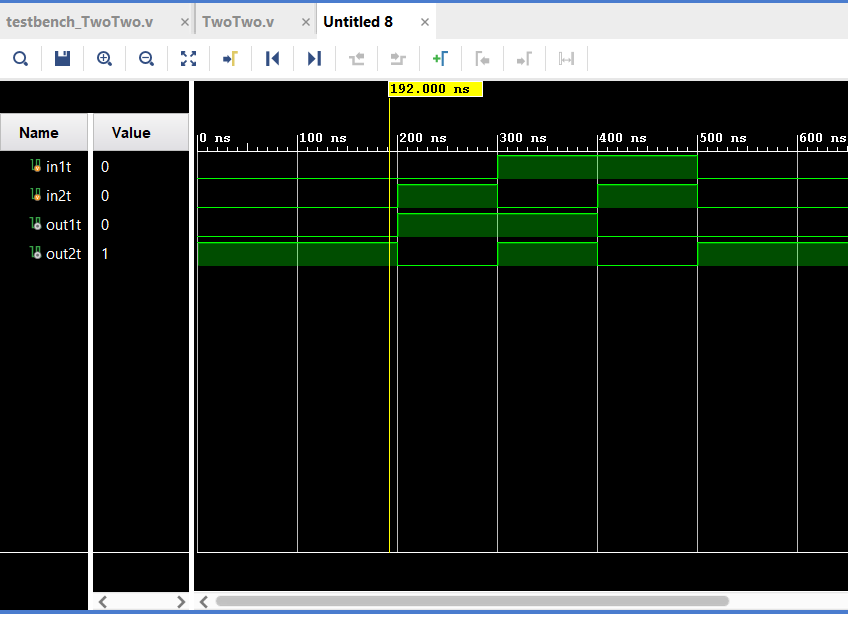

Figure 1.2: Vivado Simulation for Gvim code in Figure 1.1

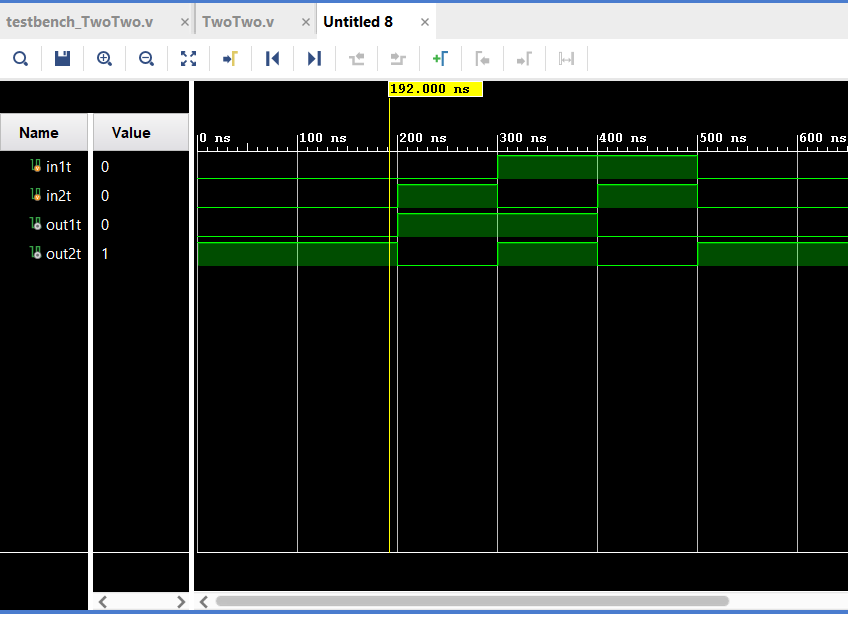

Figure 1.3: Gvim code for example 2.2 (Dataflow Modeling)

Figure 1.4: Vivado Simulation for code in Figure 1.3

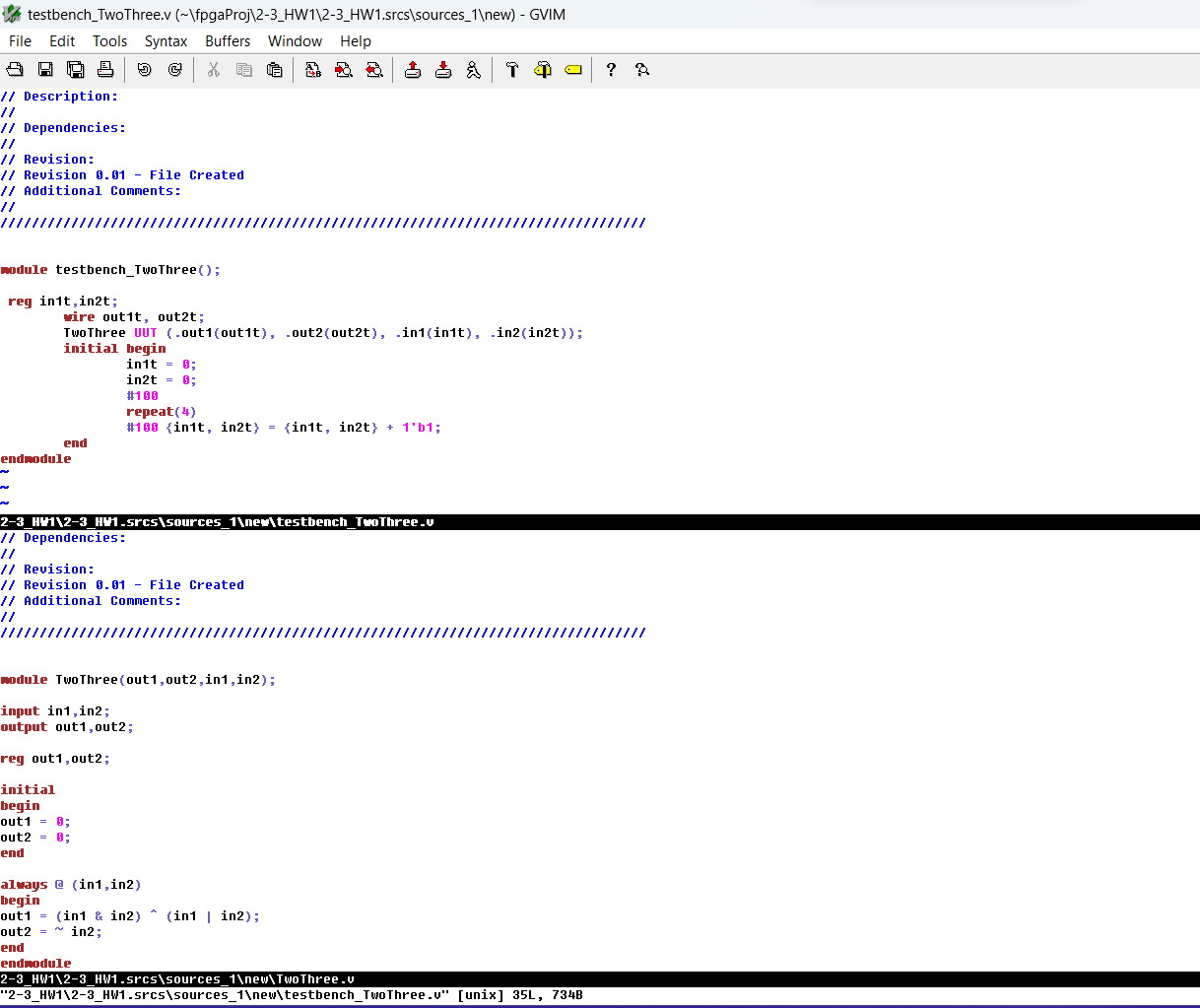

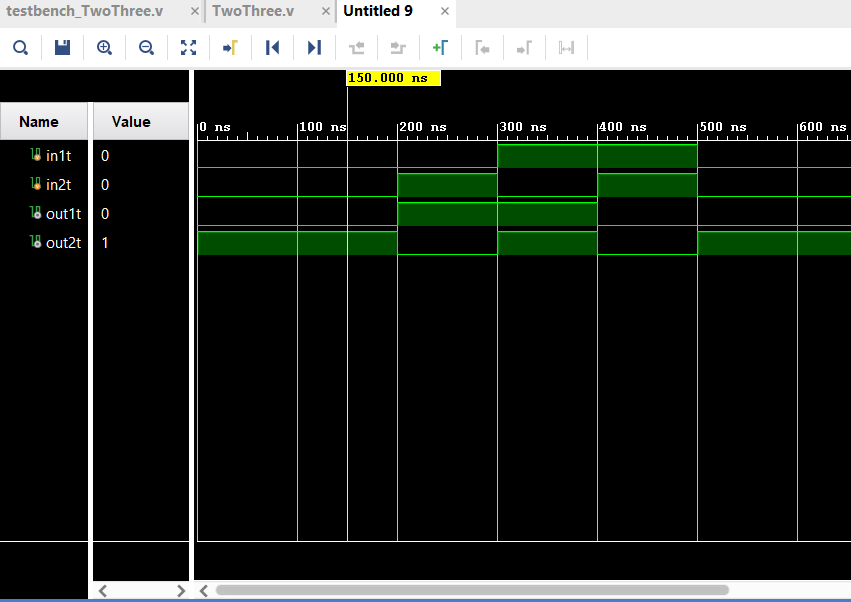

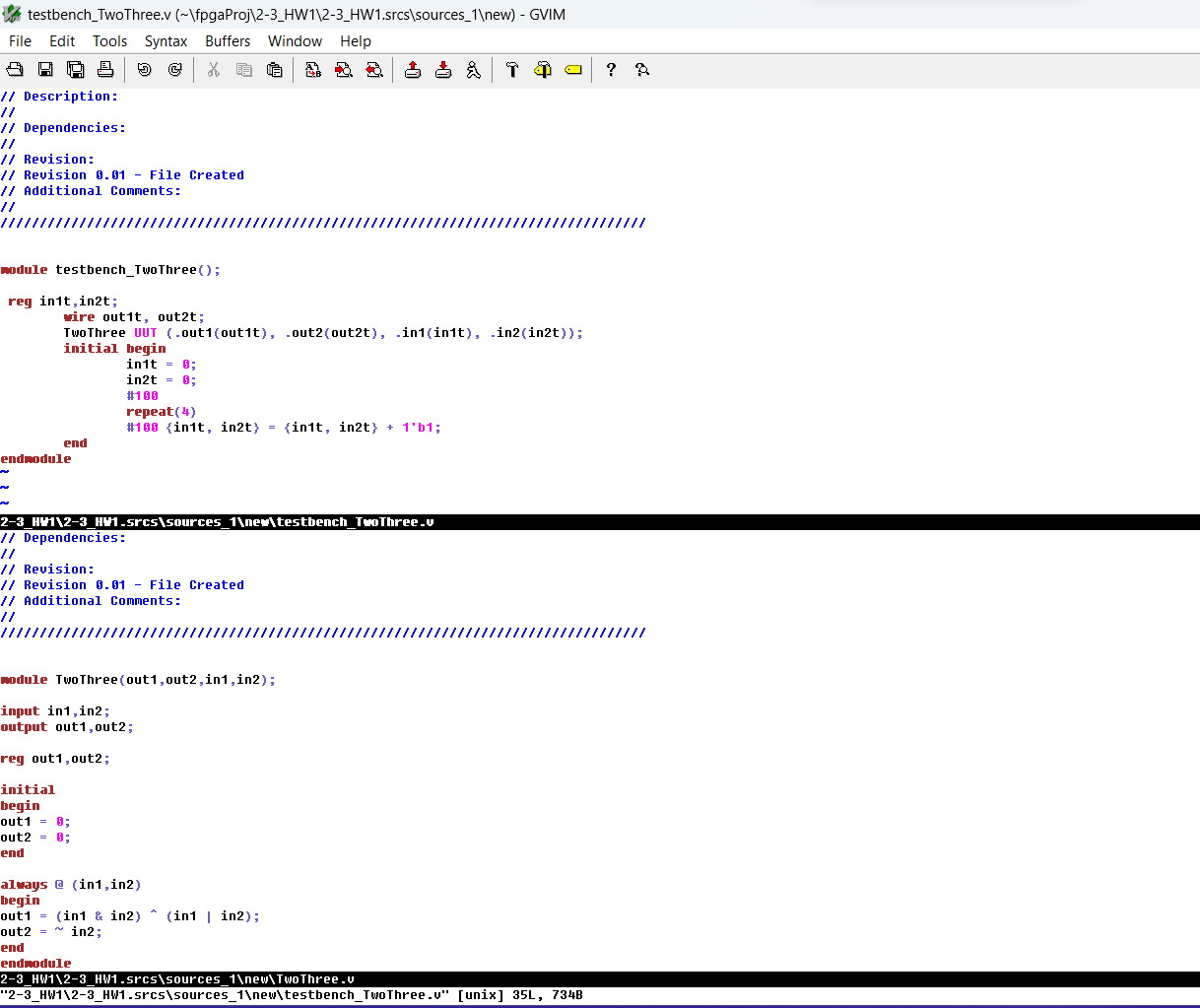

Figure 1.5: Gvim code for example 2.3 (Behavioral modeling)

Figure 1.6: Vivado simulation for Figure 1.5

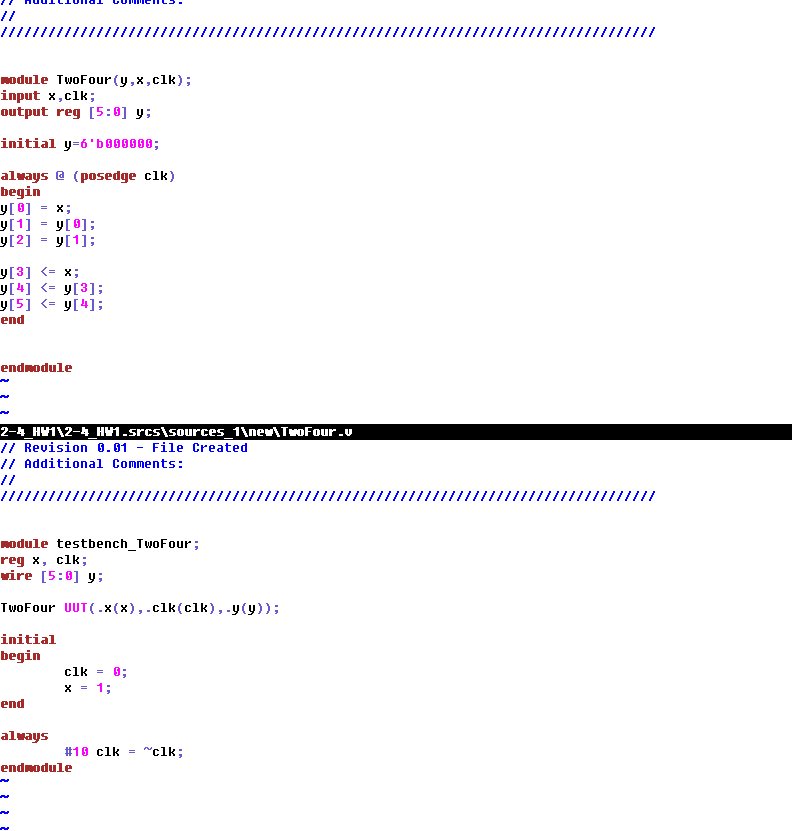

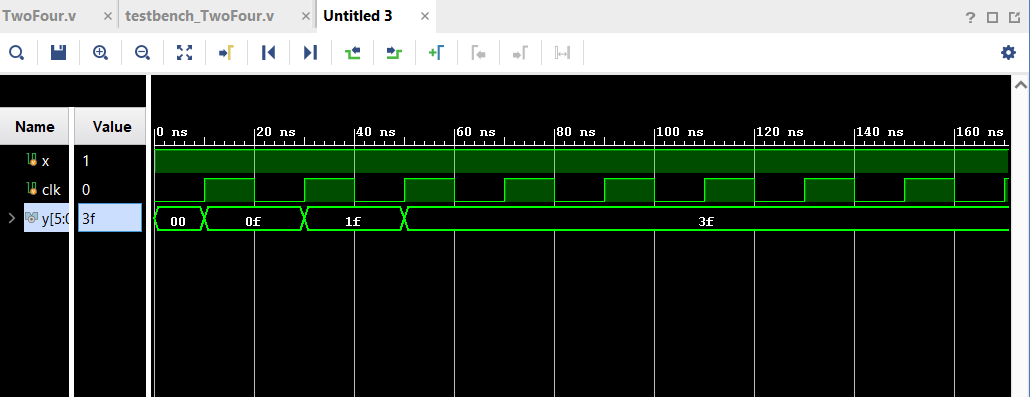

Task 2: Blocking versus Non-Blocking (2.4) (20 points).

Figure 2.1: Gvim code for blocking and non-blocking demonstration

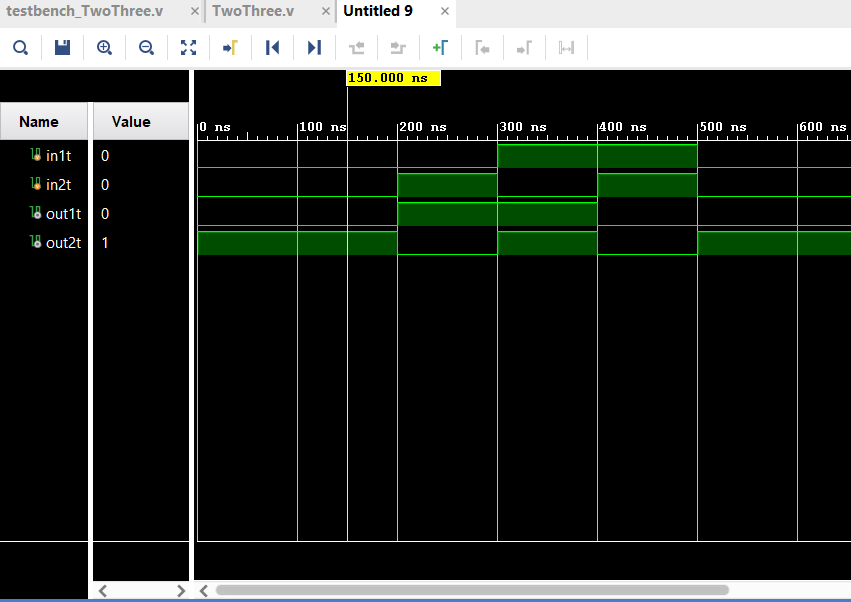

Figure 2.2: Vivado simulation results for code in Figure 2.1

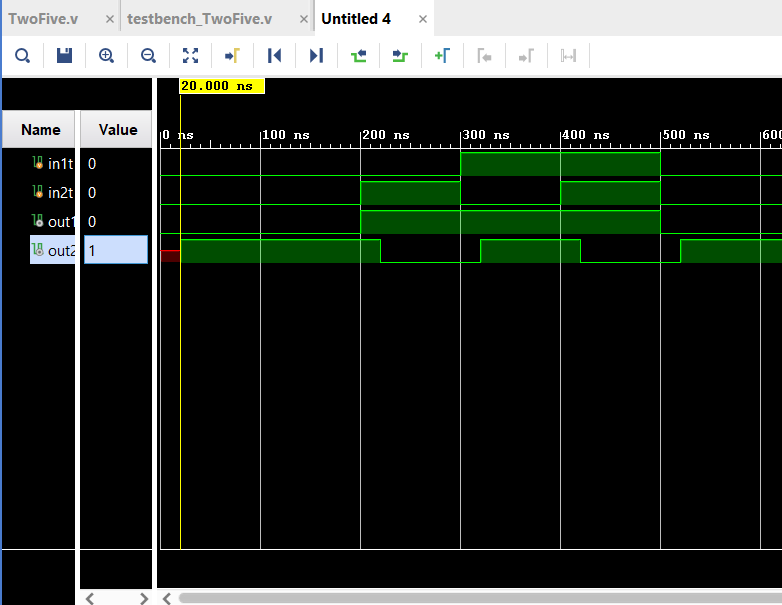

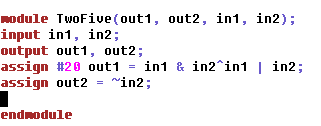

Task 3: Time delay in modeling (2.5) (20 points).

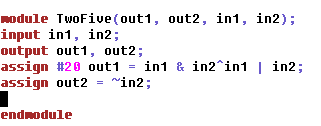

Figure 3.1: Gvim code to demonstrate the effect of a delay

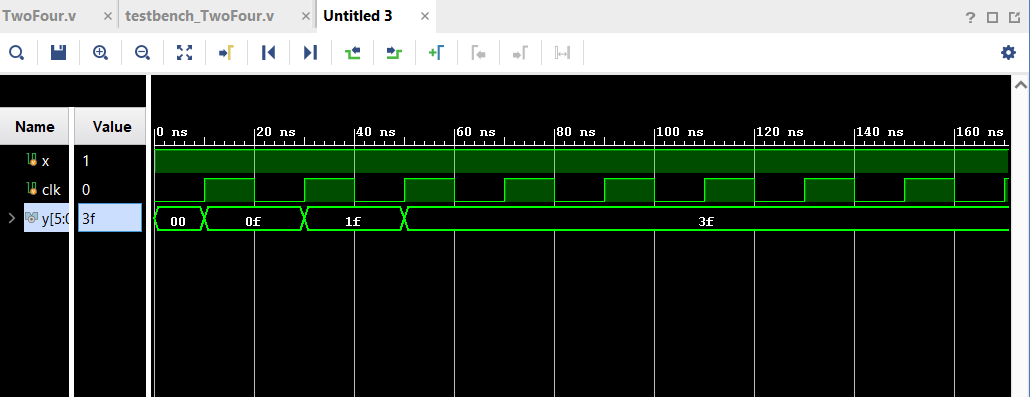

Figure 3.2: Vivado simulation for code in Figure 3.1

Figure 3.3: Hand drawn timing diagram for code in Figure 3.1

Task 4: Altering delay in 2.5 (20 points).

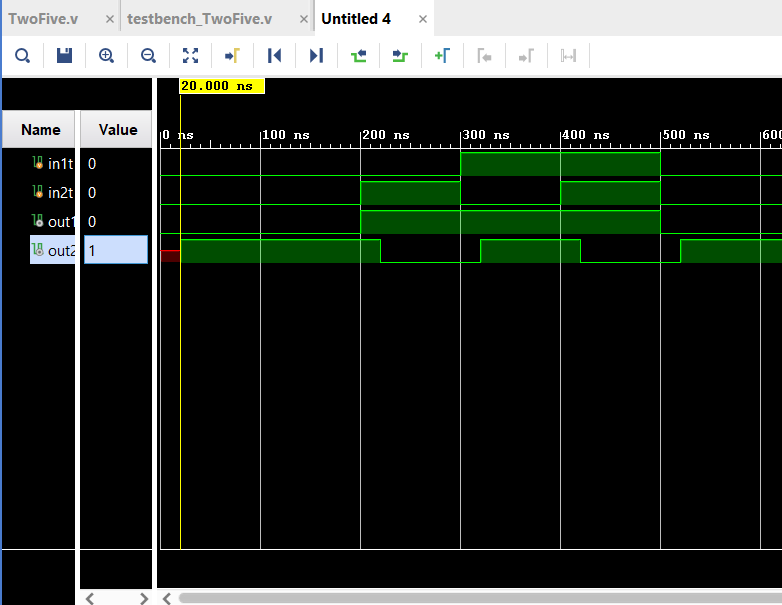

Figure 4.1: Altered code from Figure 3.1, delay is moved from out 2 assignment to out 1 expearment

Figure 4.2: Vivado simulation for Figure 4.1 code

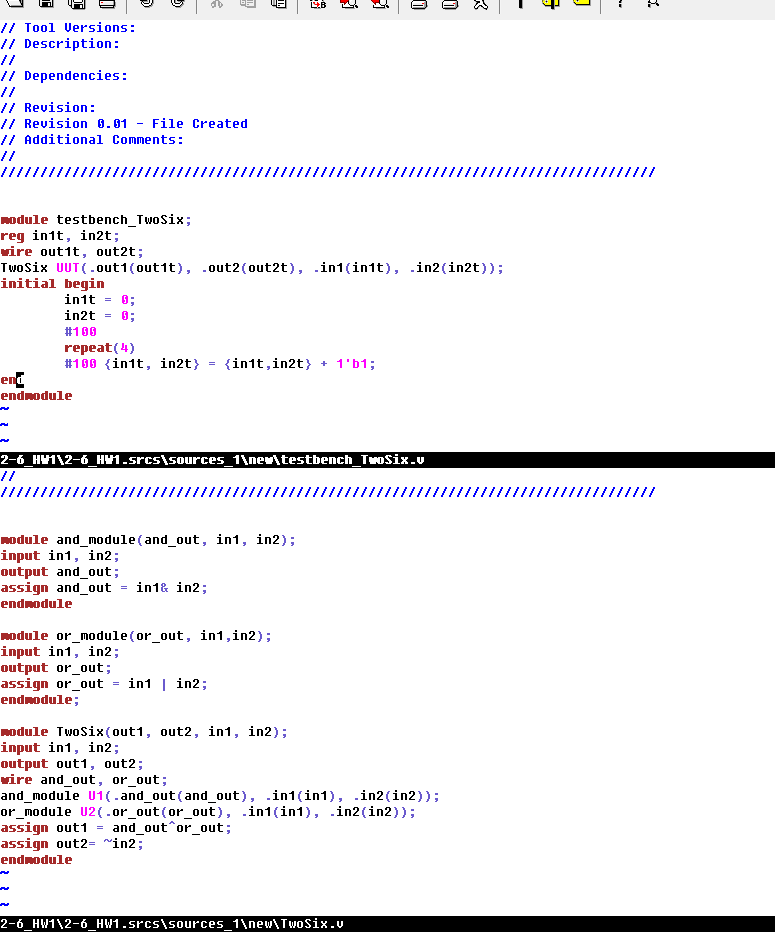

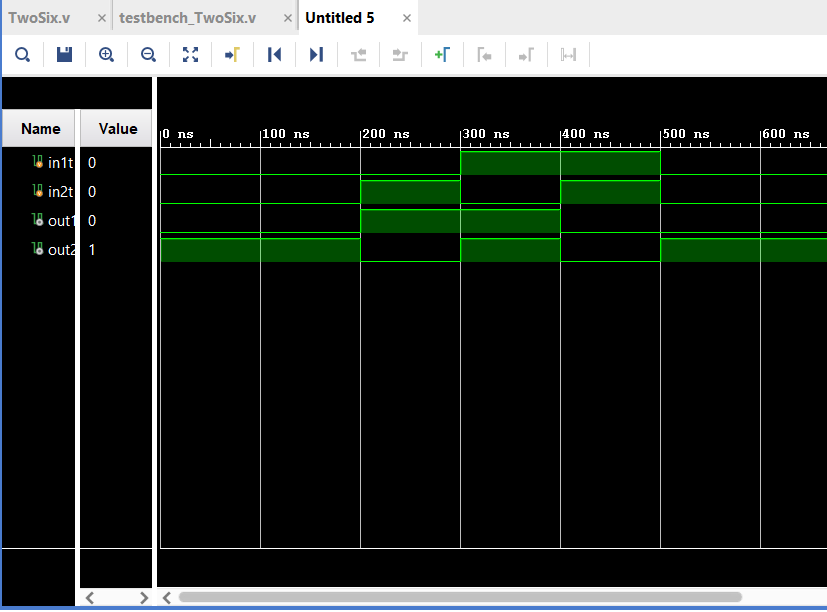

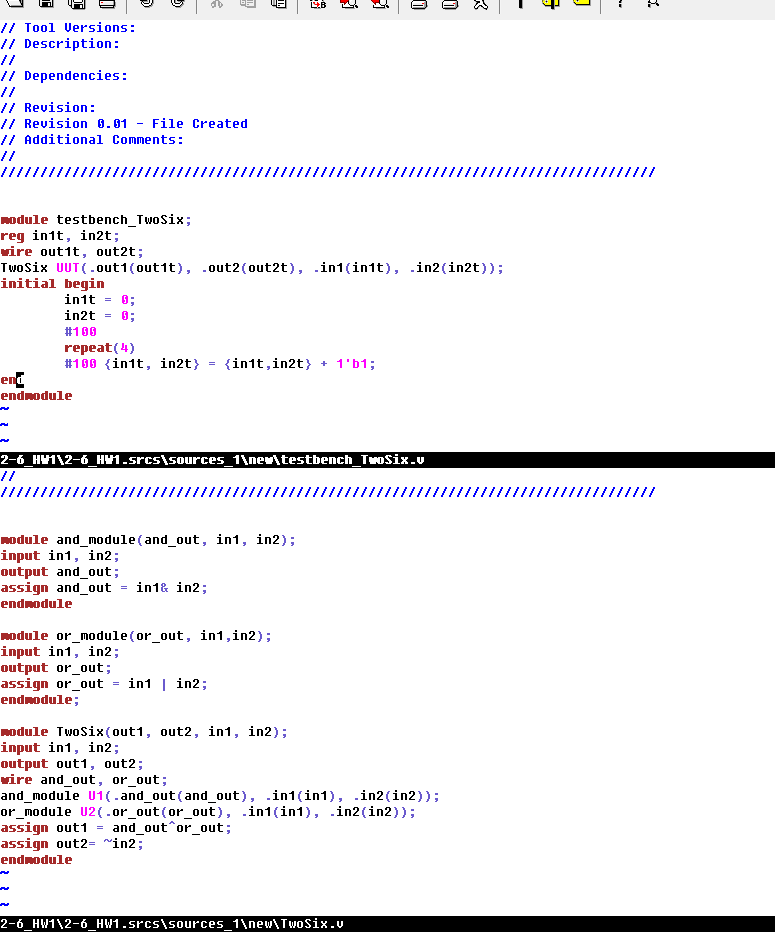

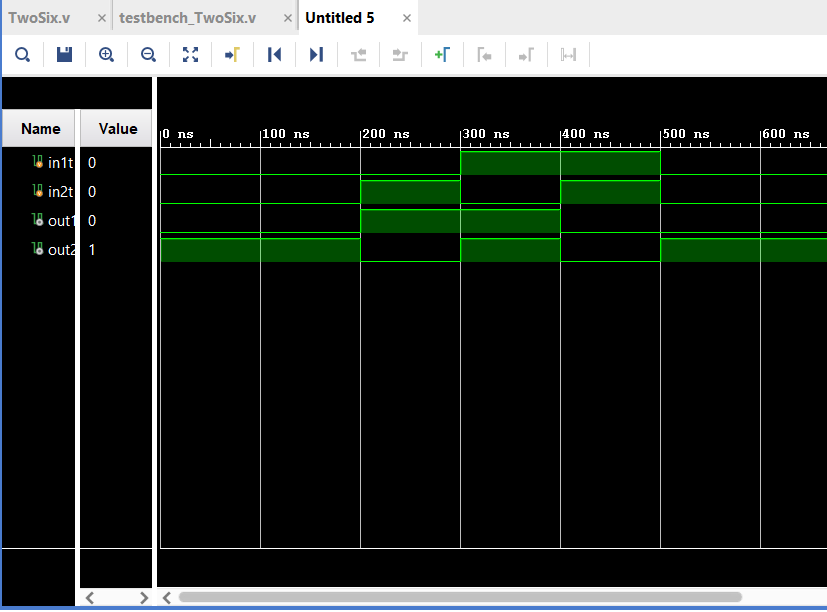

Task 5: Hierarchial Module Representation (20 points).

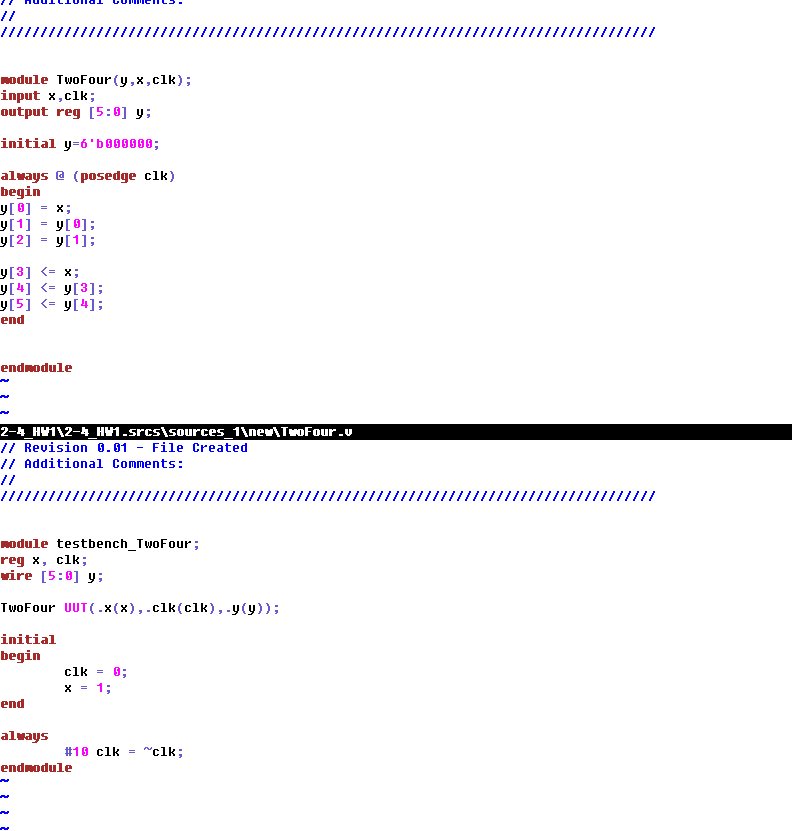

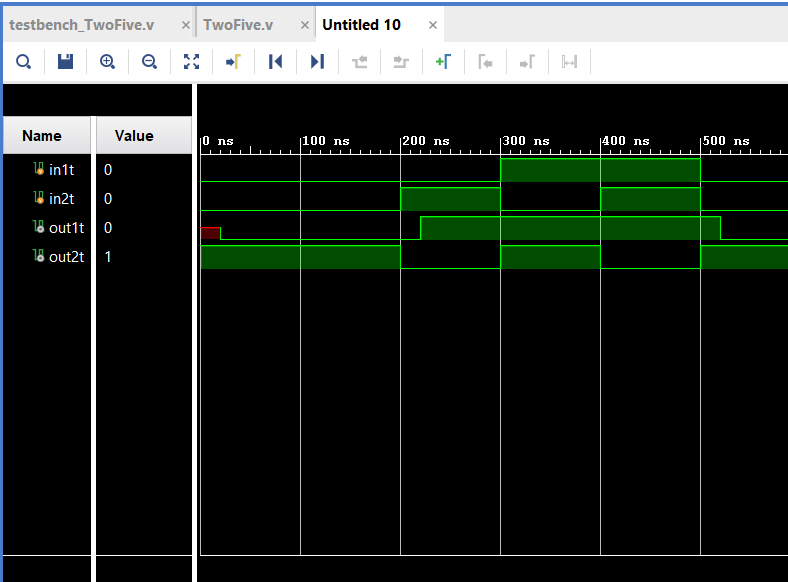

Figure 5.1: Gvim code for multiple modules in a single file

Figure 5.2: Vivado simulation for code in Figure 5.2

Conclusion: This lab sucessfully taught how to use LTSpice inside Eletric VLSI and how to layout a basic DAC