ENGR 338 - Lab 4 2023 Fall

Name: Ian Van Horn

Email: imvanhorn1@gmail.com

Lab 4 MOSFETs and IV Curves

This lab

introduces NMOS and PMOS MOSFET transistors. The schematics and layouts

of both transistor styles were fabricated. Simulations were run in

LTSpice

This lab requires the Eletric VLSI software

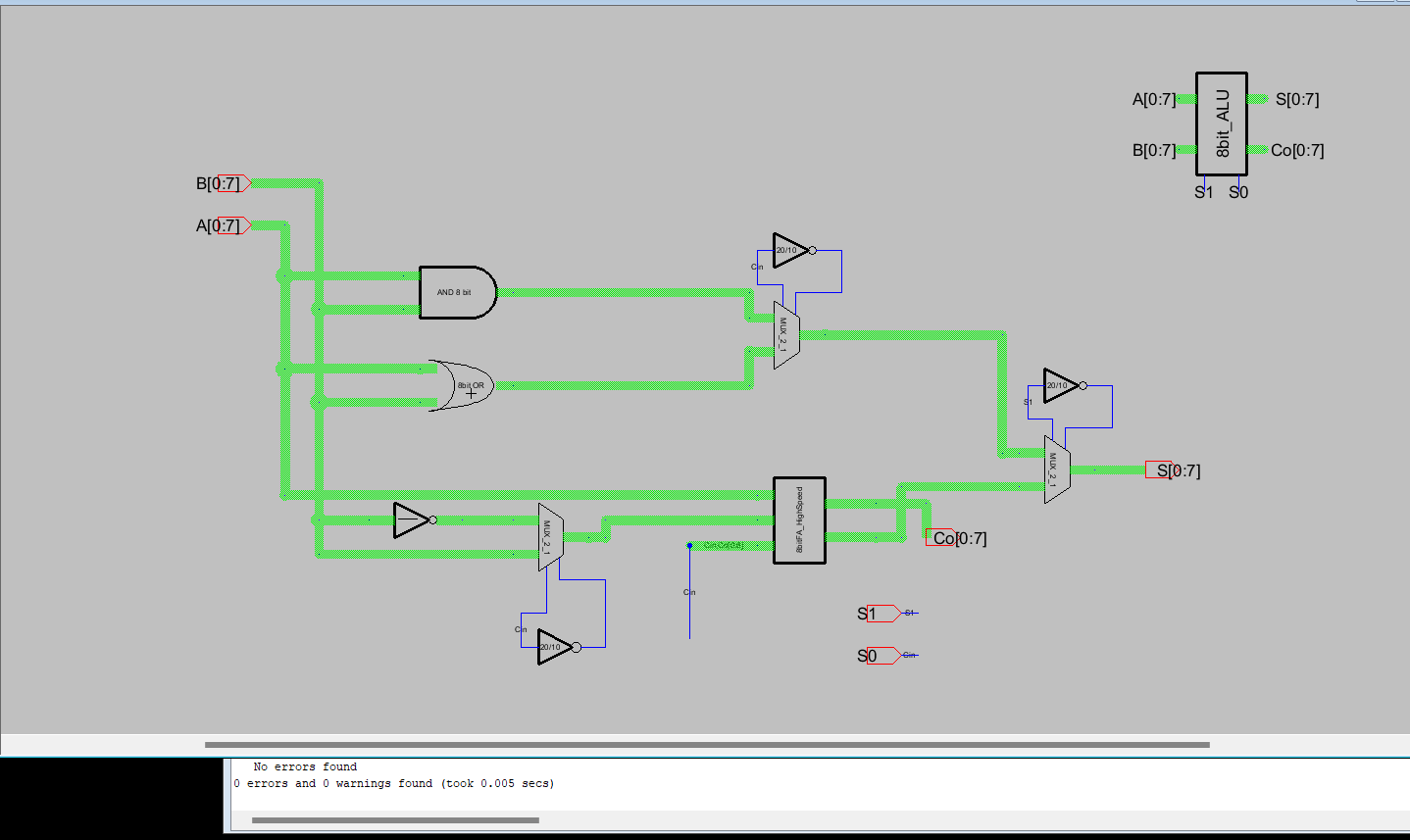

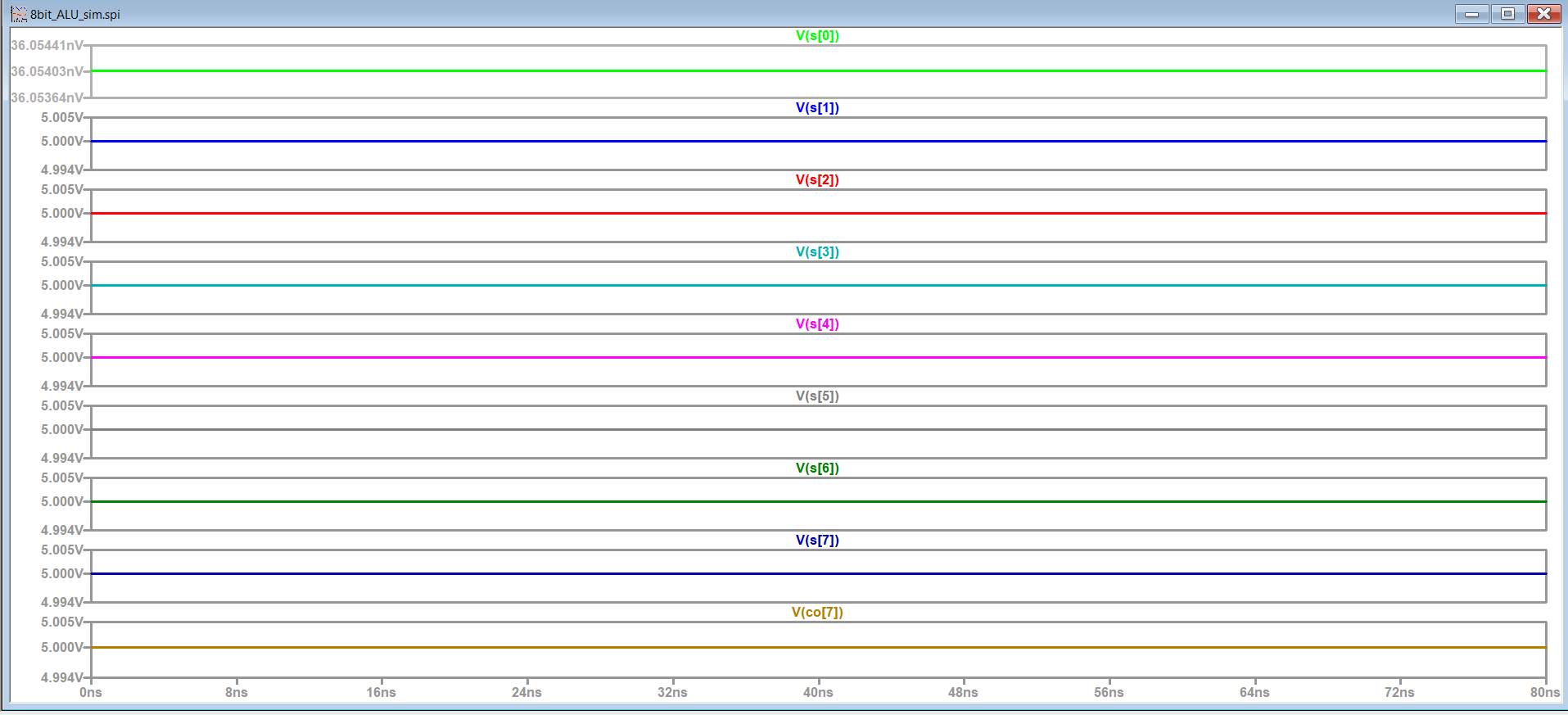

Task 1: Design the logic circuit of the ALU. (40 points)

Figure 1: ALU Schematic

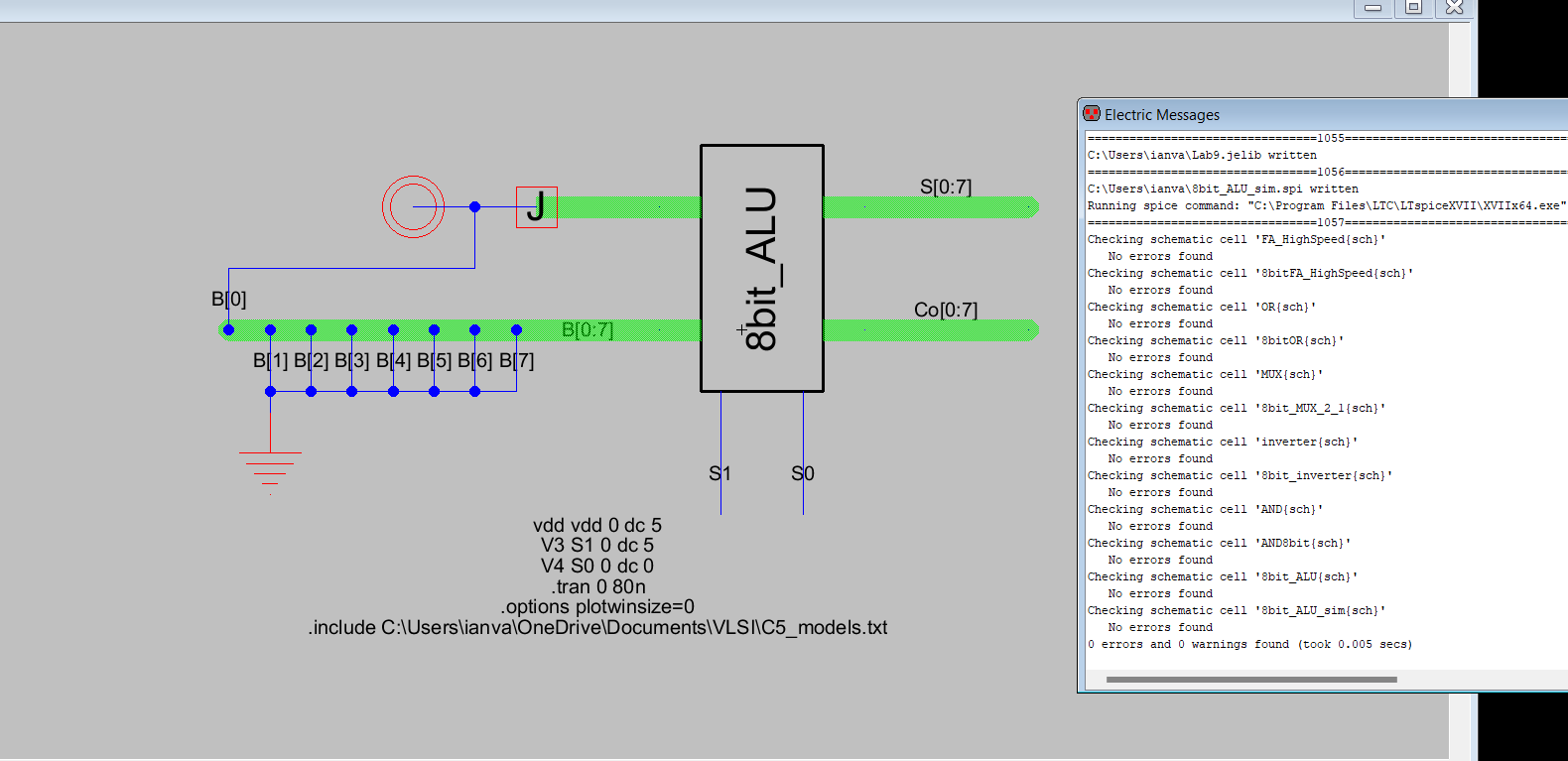

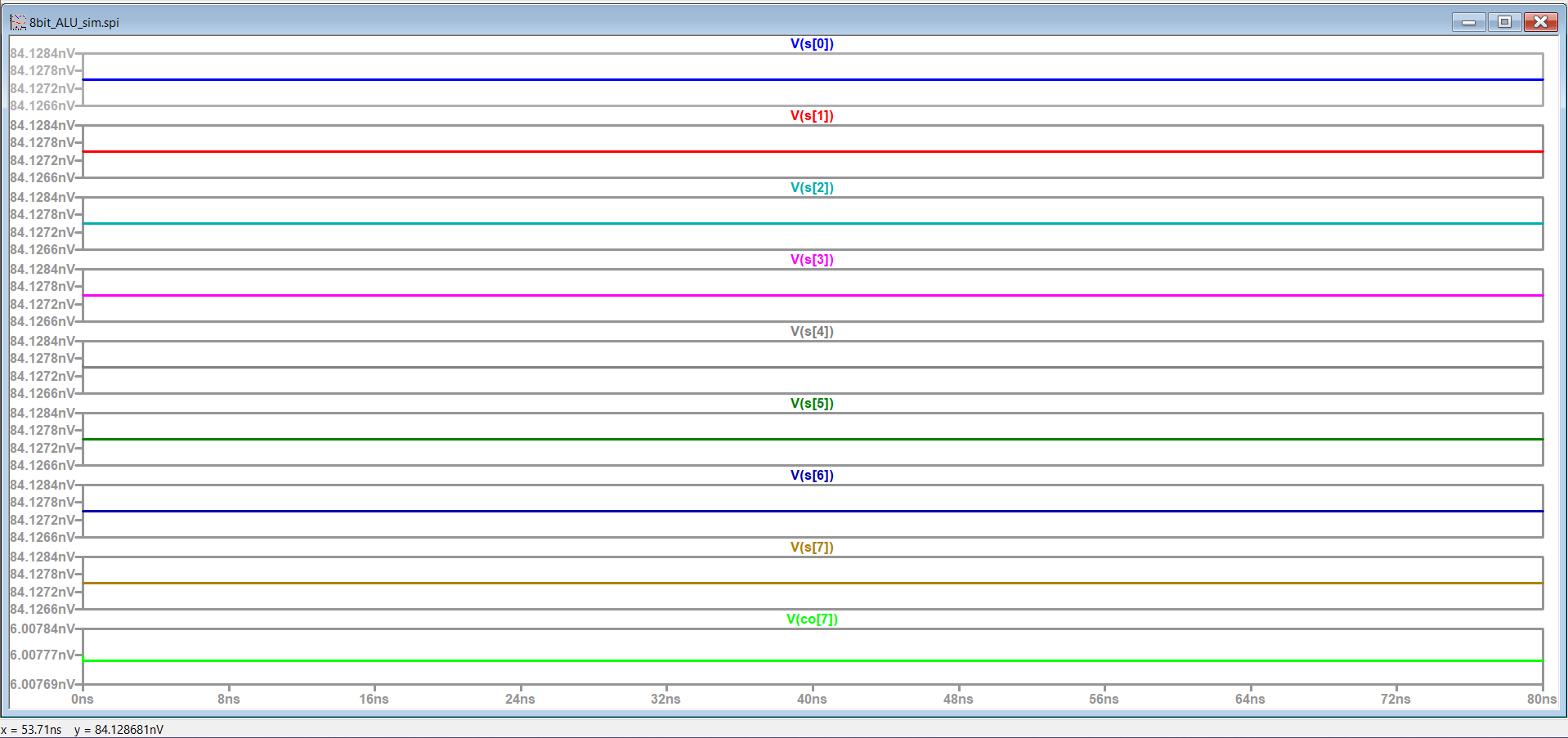

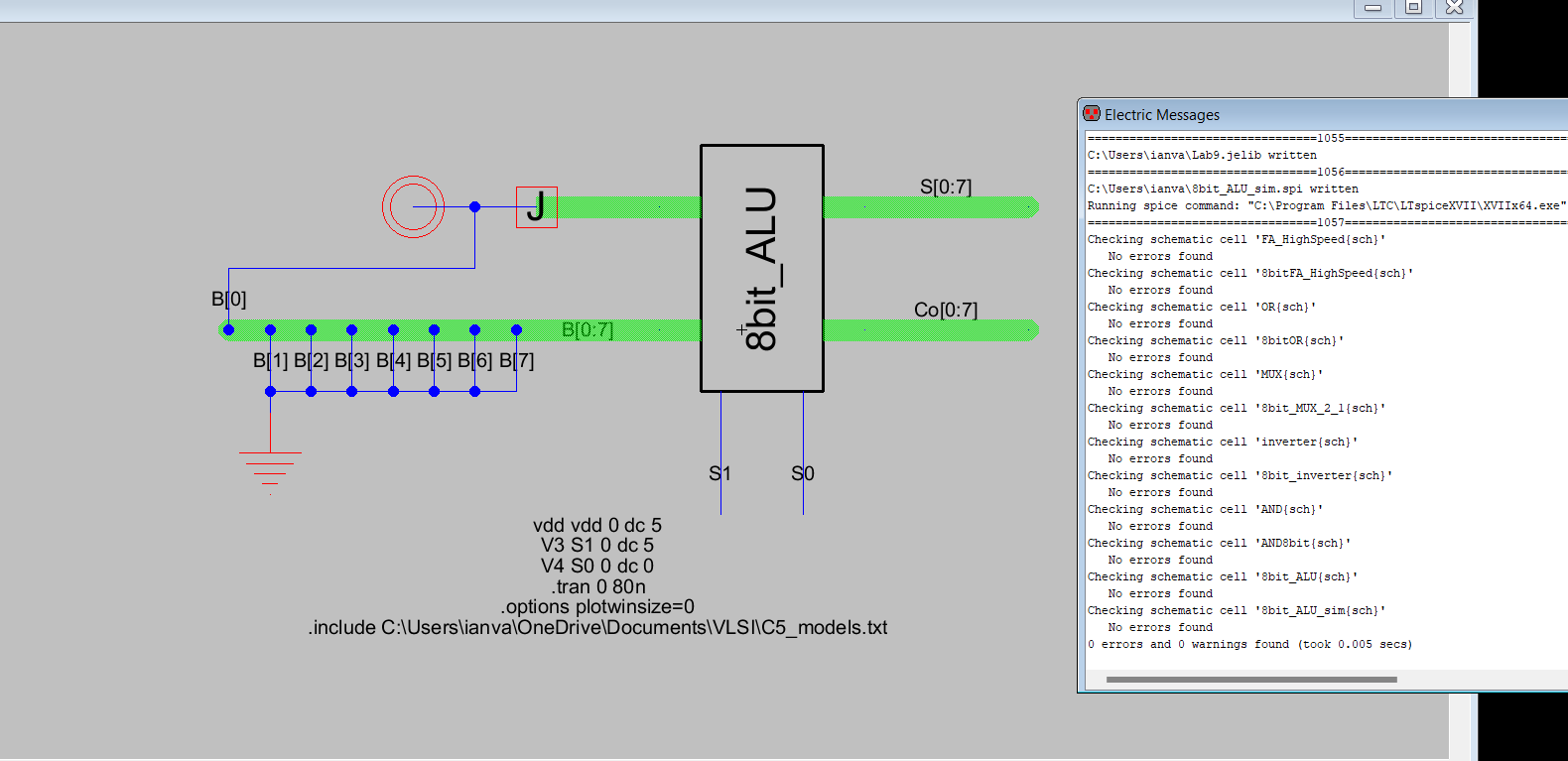

Figure 2. Simulation Schematic of ALU with A inputs high, B inputs low, S0 and S1 low

Figure 3: Simulation results of Figure 2

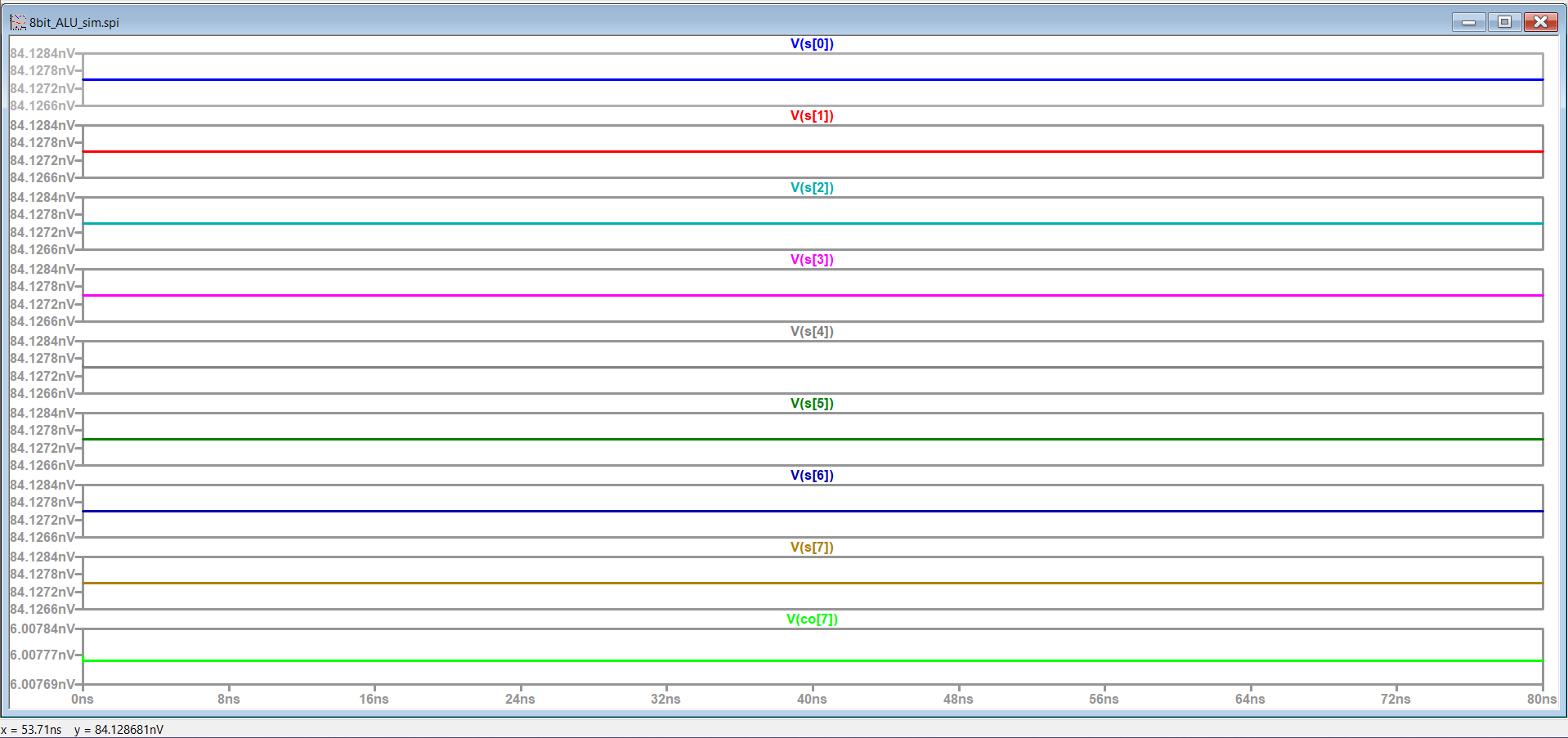

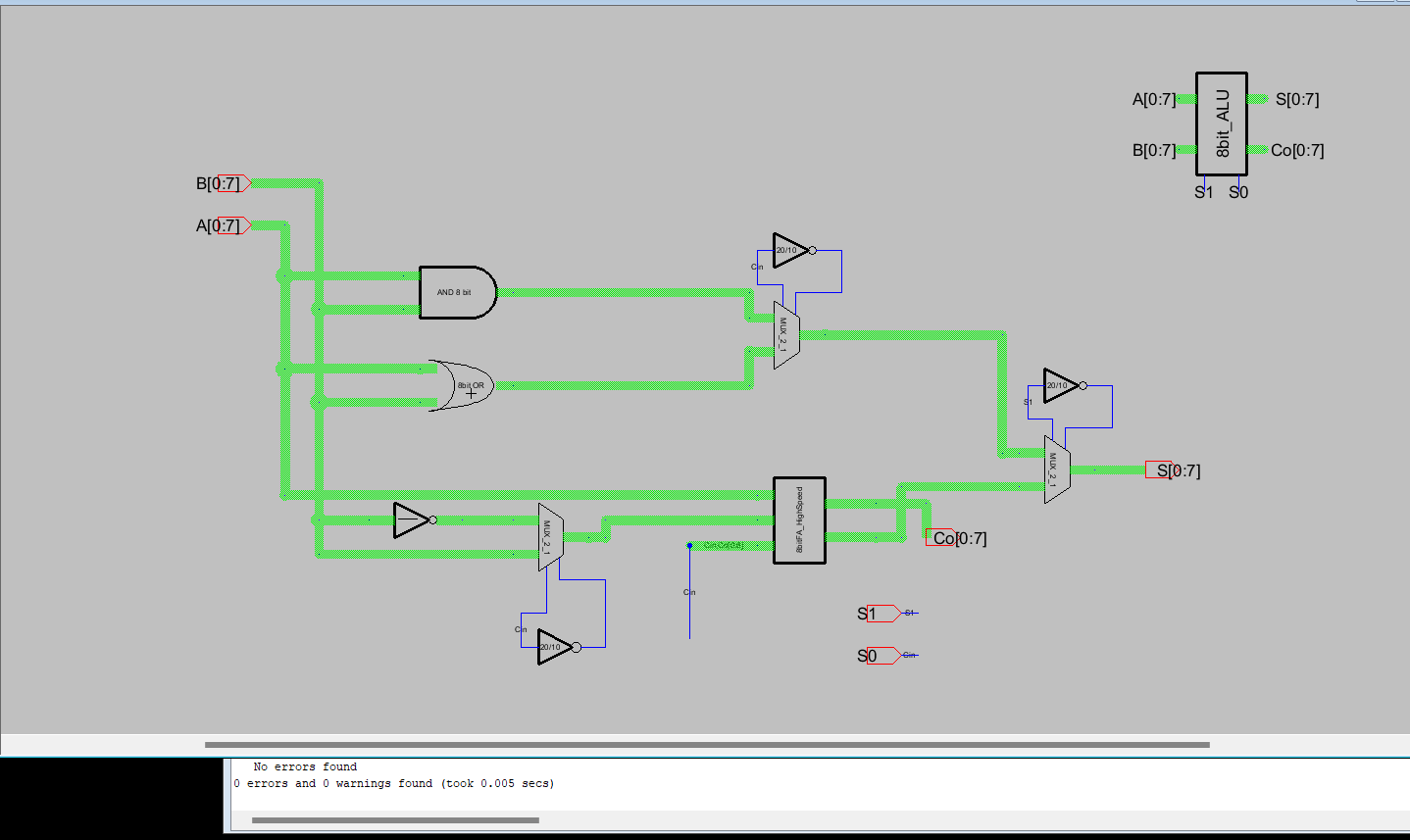

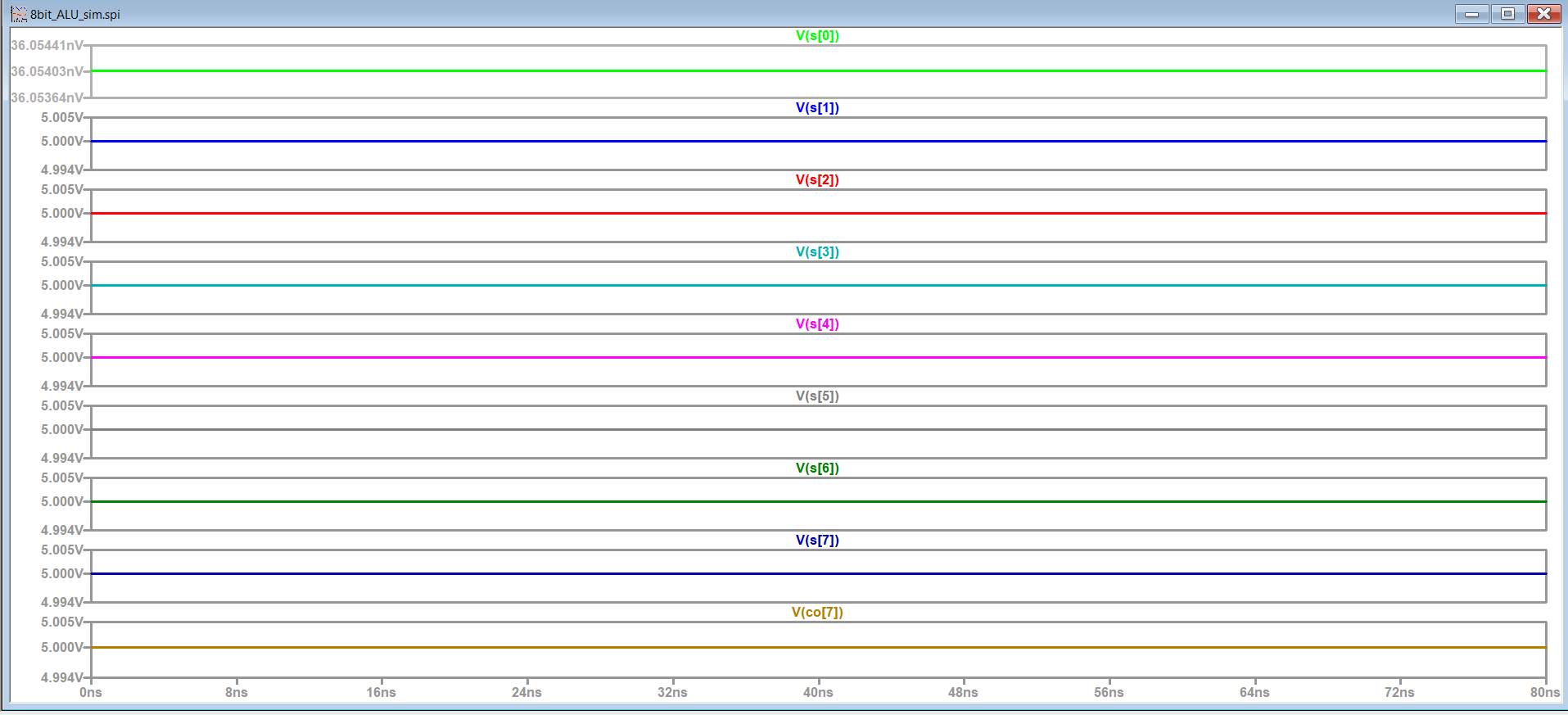

Figure 4: SPICE results with all A inputs low, all B inputs high, S0 high, and S1 low

Figure 5: ALU simulation schematic with all A inputs and B[0] high, B[1]-B[7] low, S0 low, and S1 low.

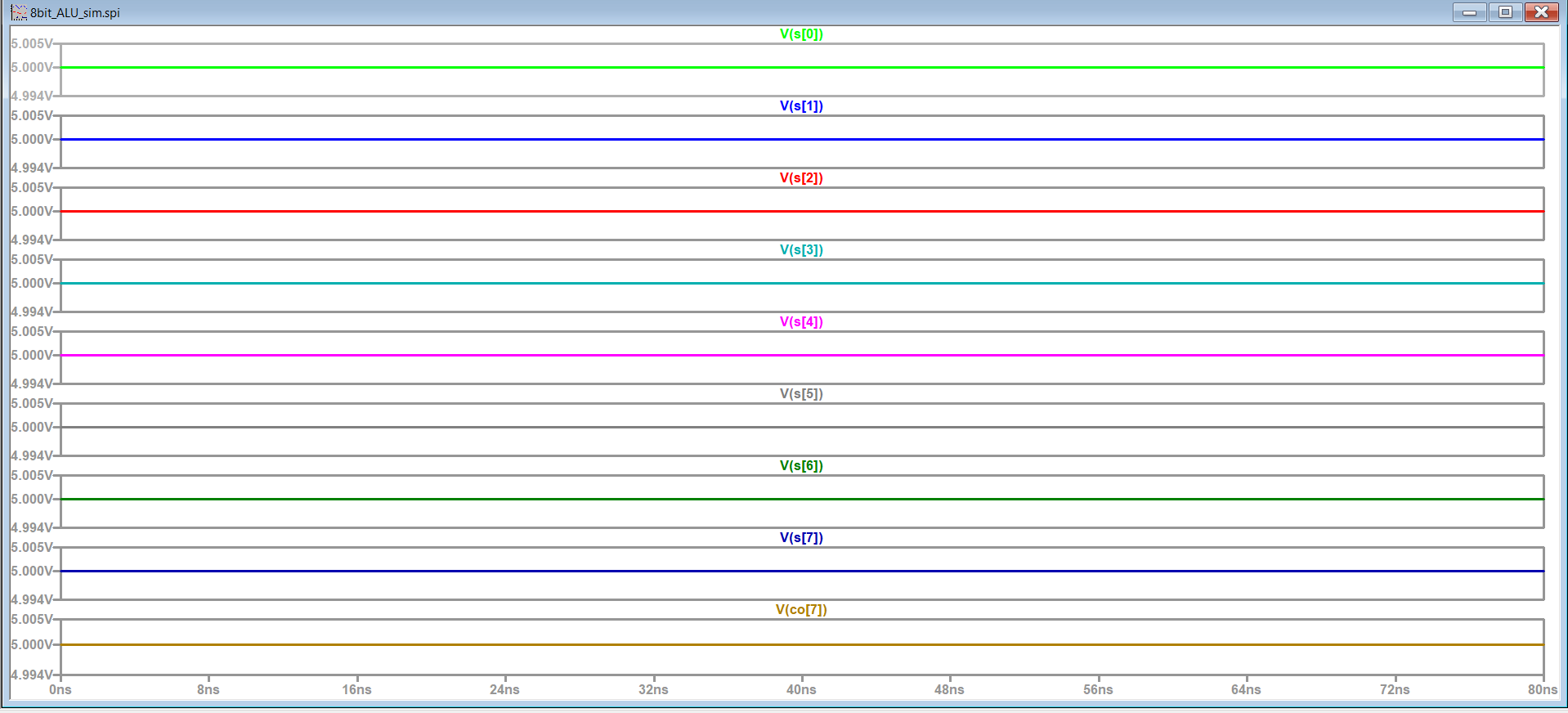

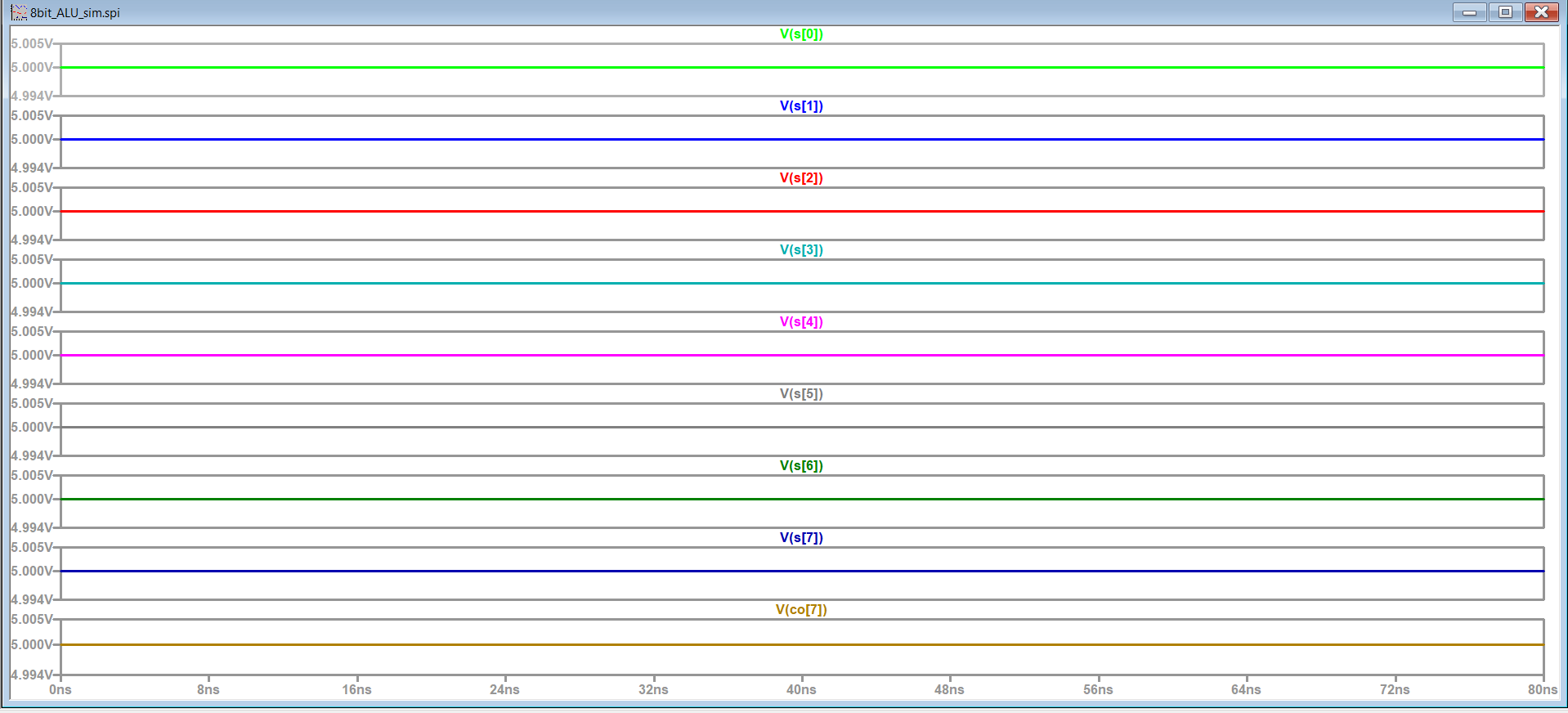

Figure 6: Spice results of Figure 5

Figure 7: Spice results of Figure 5 with S0 written to ground

Task 2: Finish the layout of the ALU. (50 points).

Conclusion: This lab integrated all of the previous labs to create a larger scale layout