ENGR 338 - Lab 6 2023 Fall

Name: Ian Van Horn

Email: imvanhorn1@gmail.com

Lab 6 Build a NAND, NOR, XOR, and Full Adder

This lab provides extensive practice with the layout of transistors

This lab requires the Eletric VLSI software

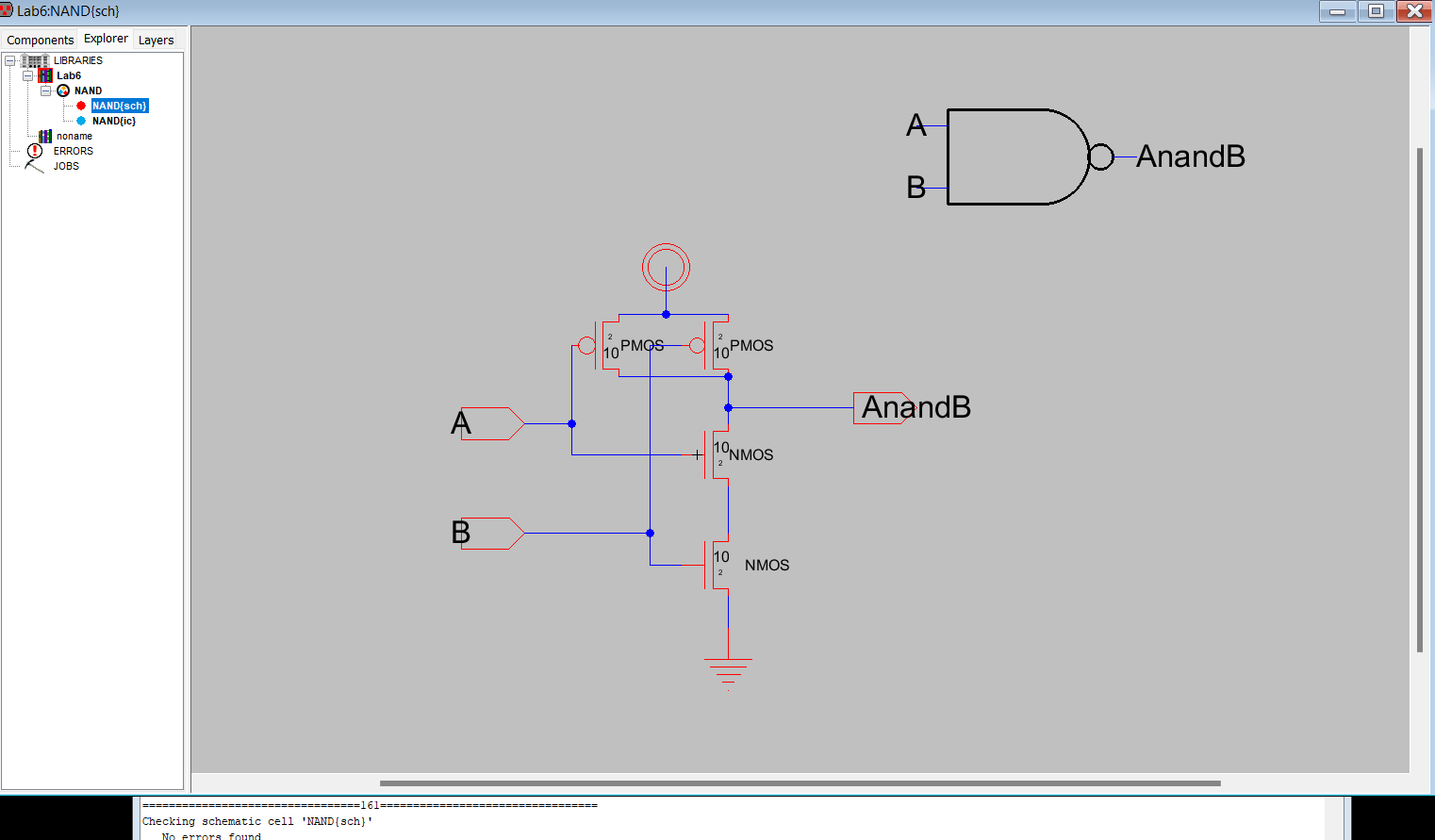

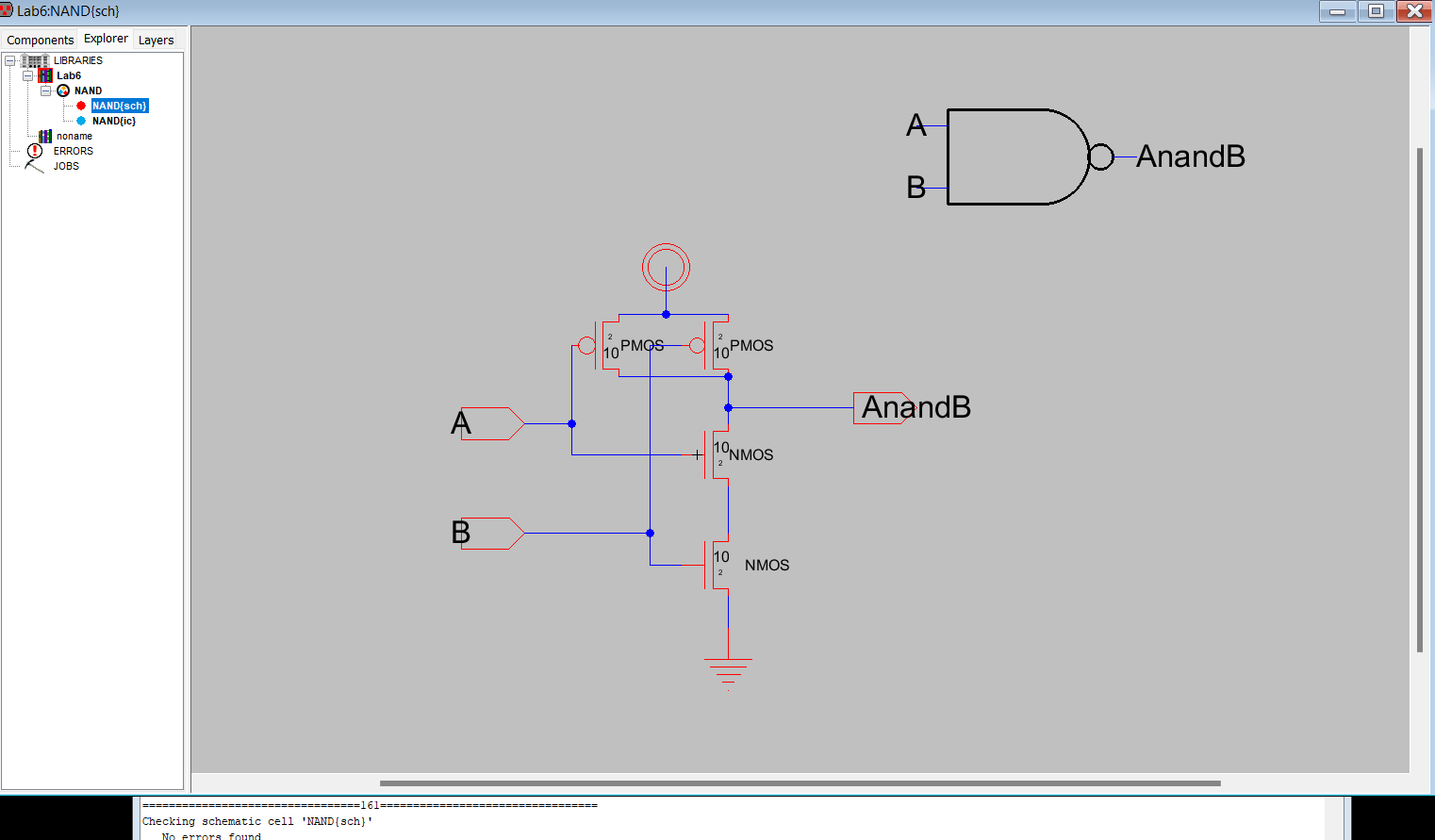

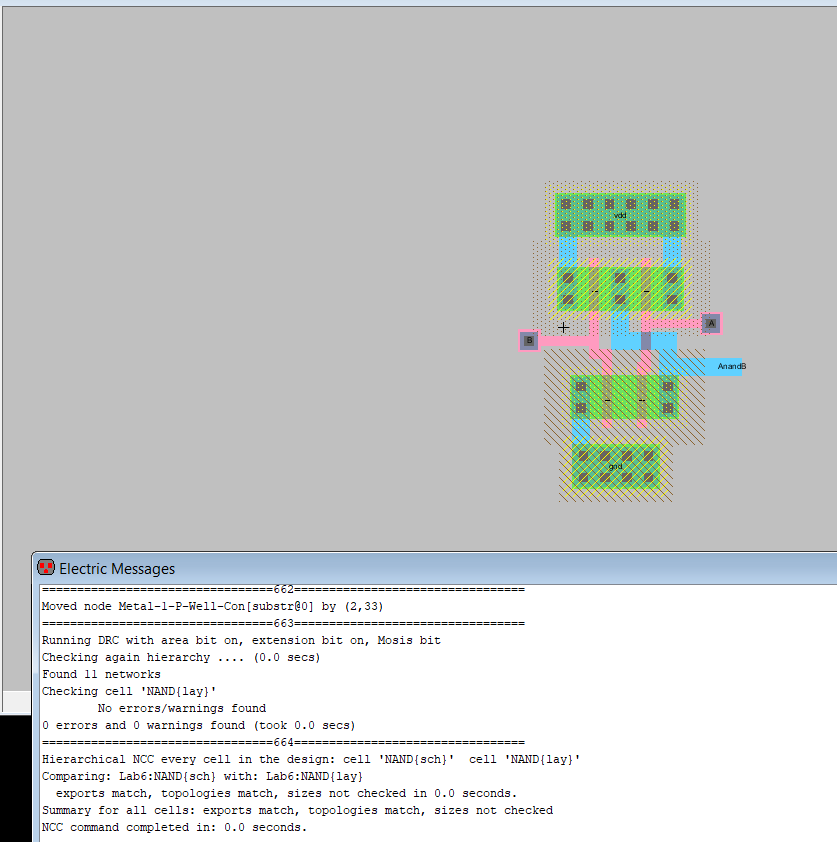

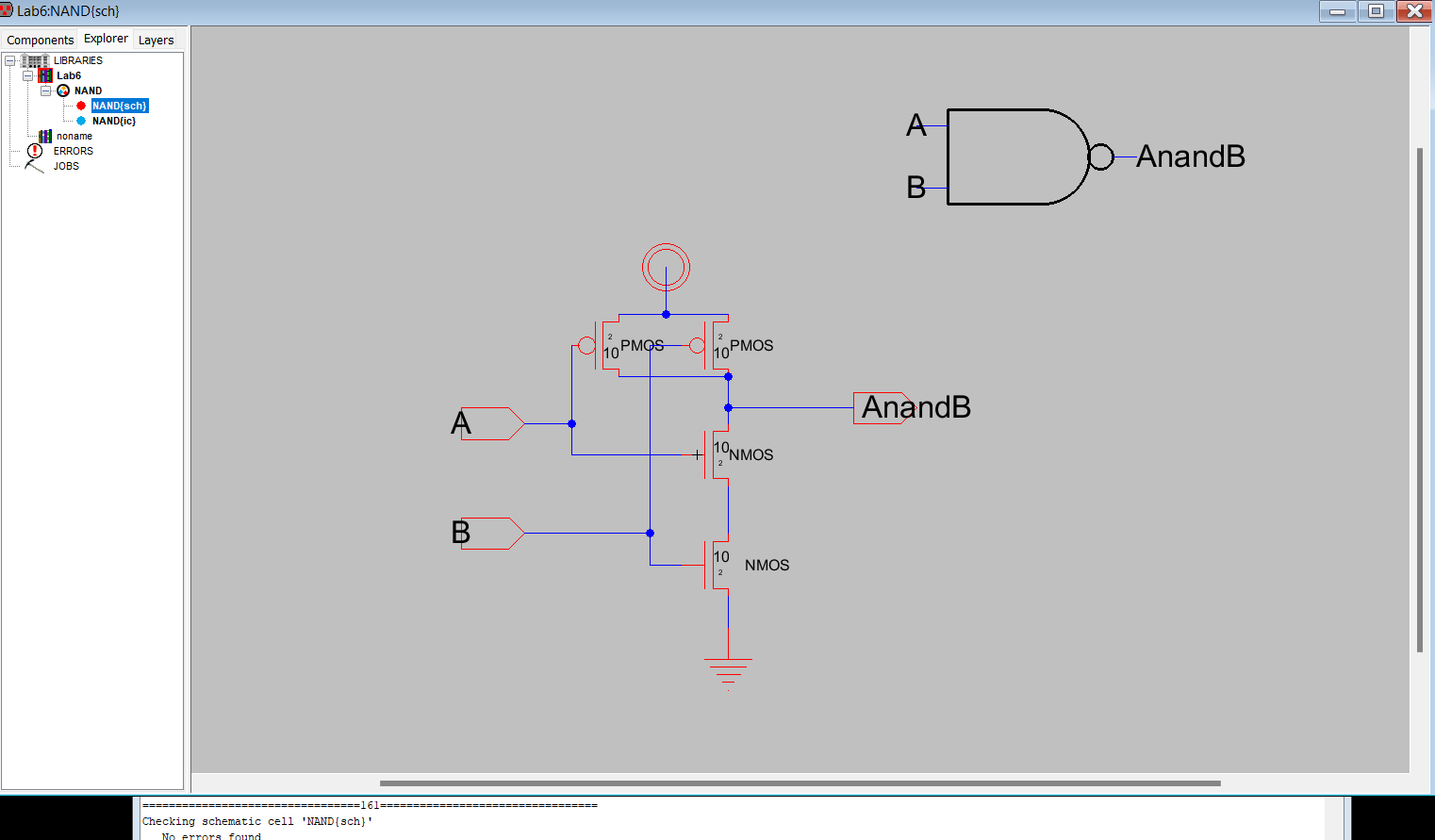

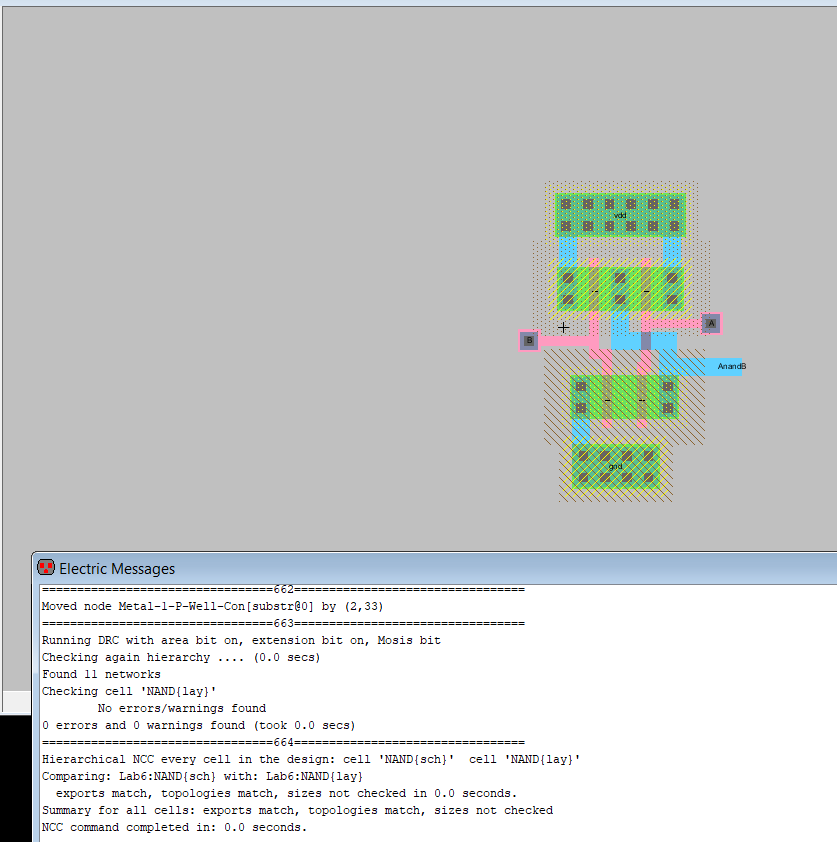

Task 1: Create the schematic and layout of the NAND gate. (15 points)

Figure 1: Error free schematic of NAND

Figure 2. NAND error free layout

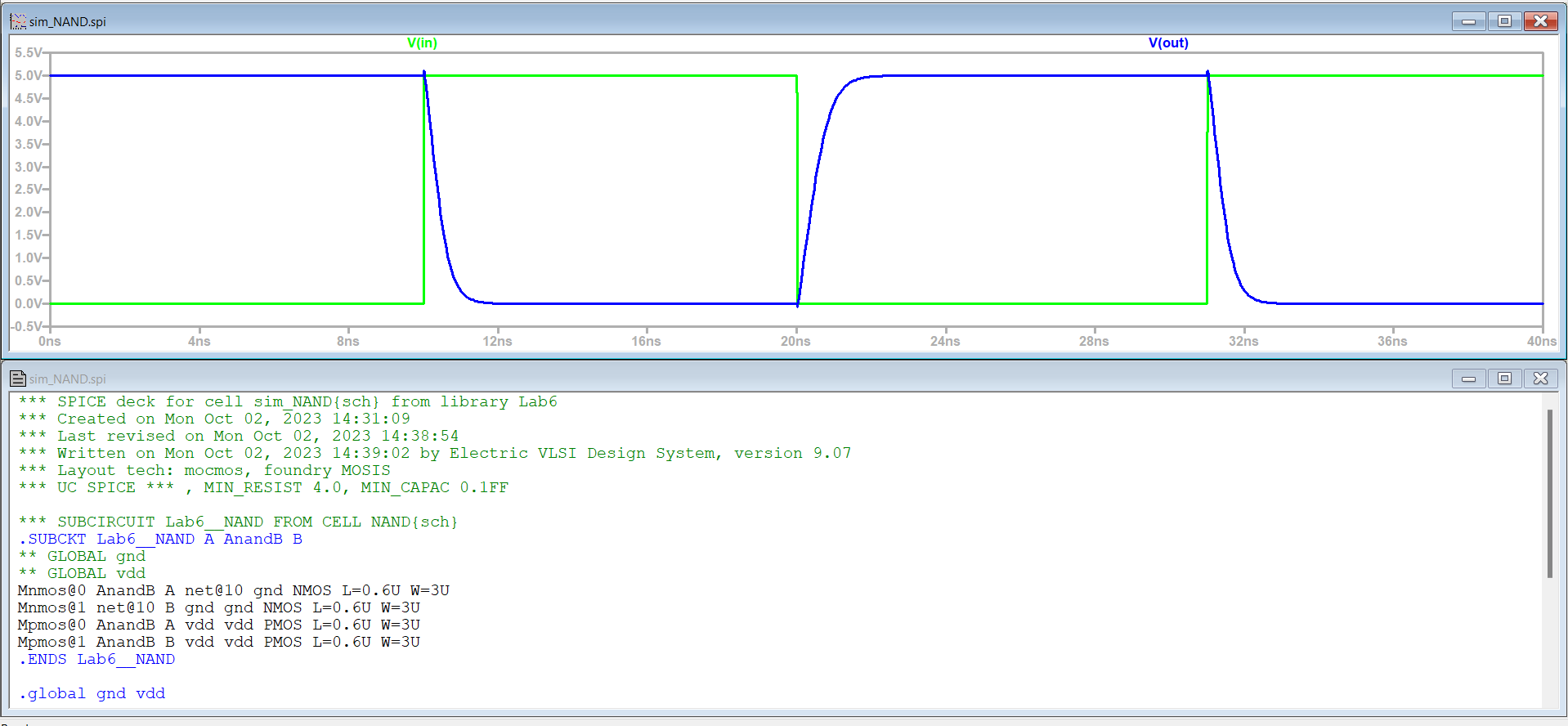

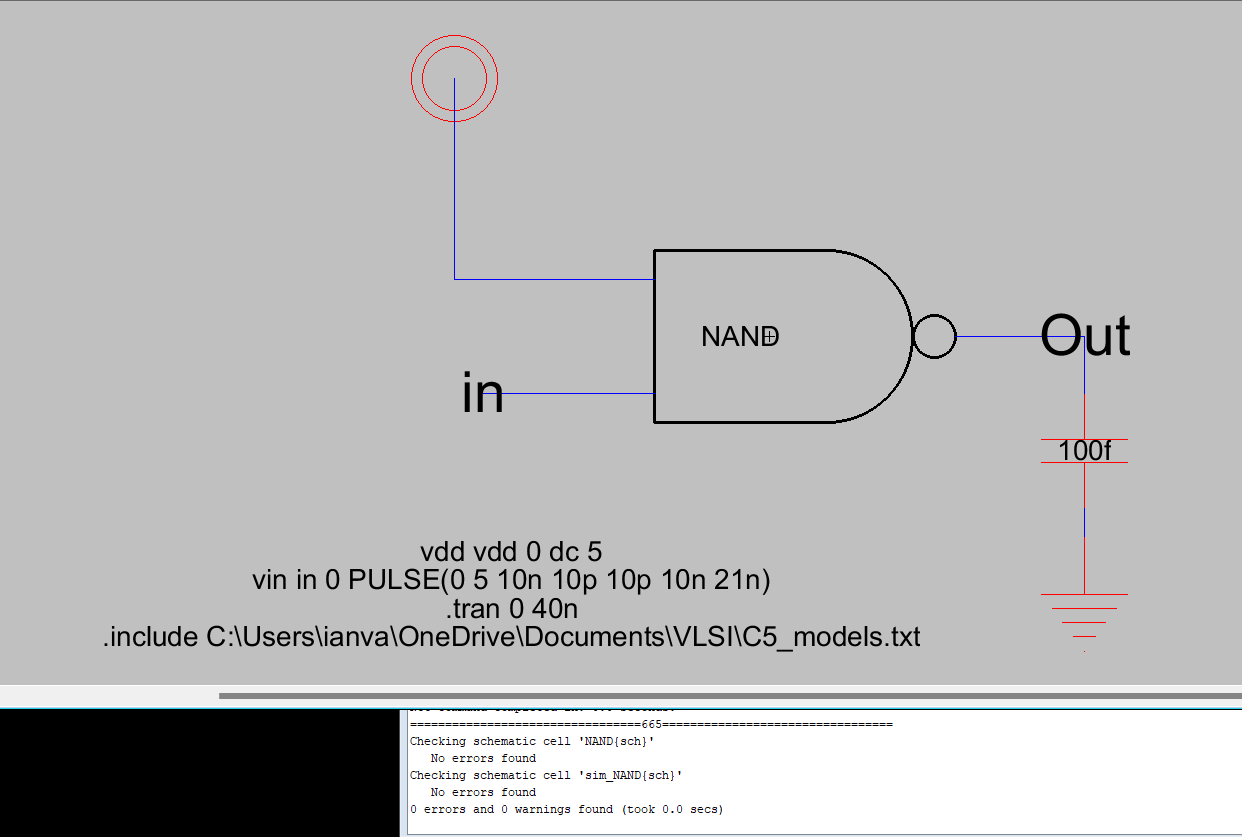

Figure 3: Error free NAND simulation schematic and SPICE code

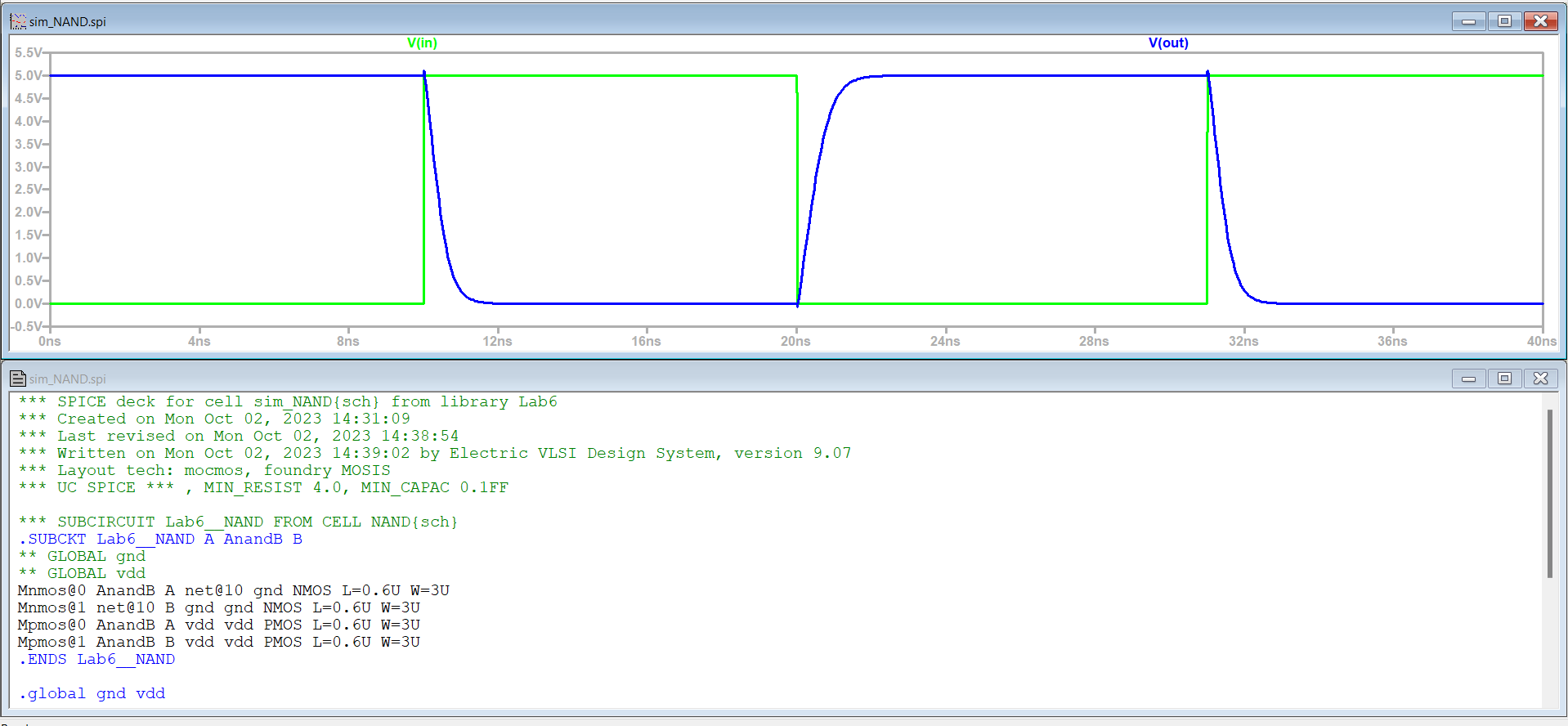

Figure 4: NAND simulaton in spice

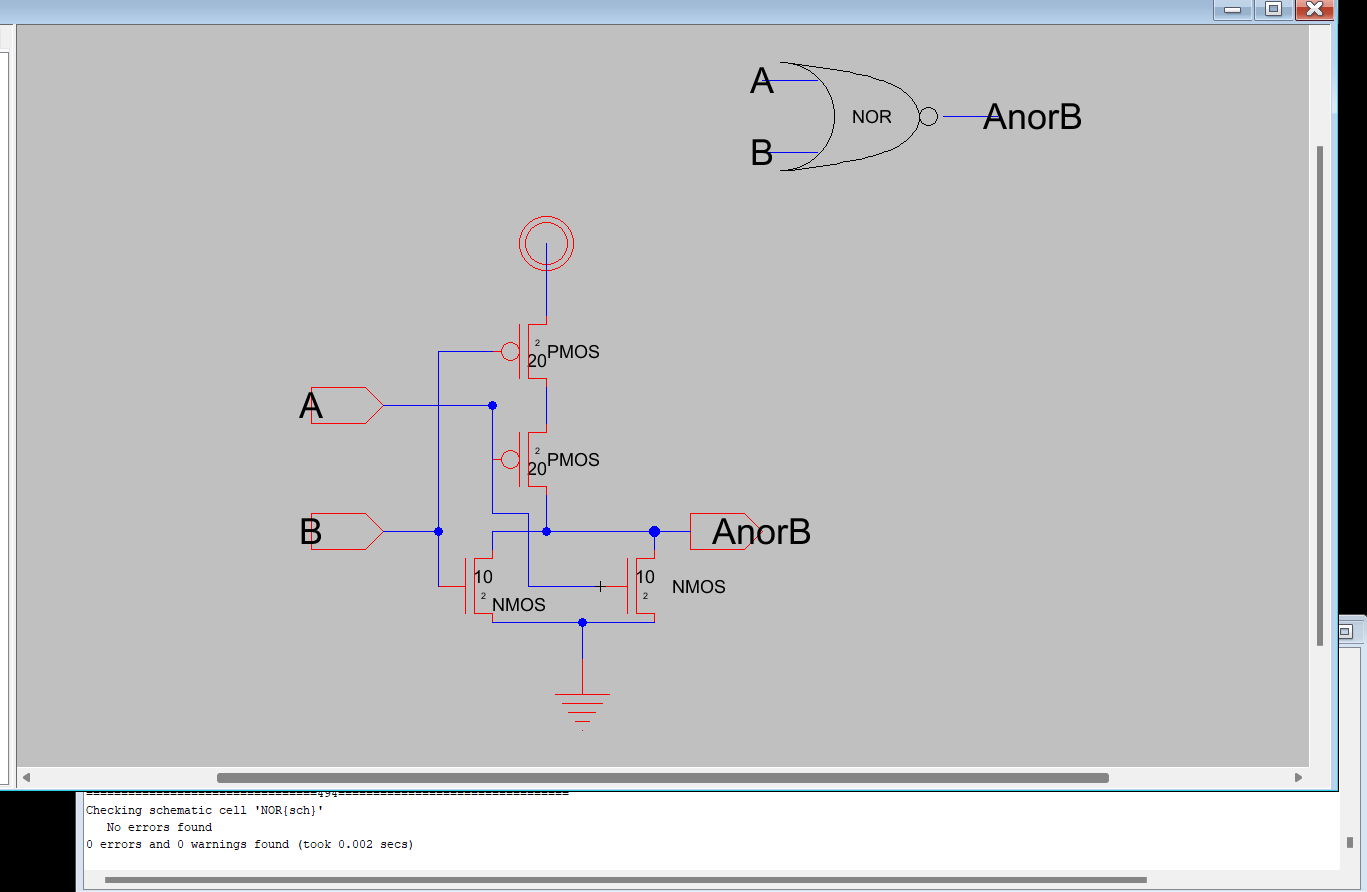

Task 2: Create the schematic and layout of the NOR gate. (15 points)

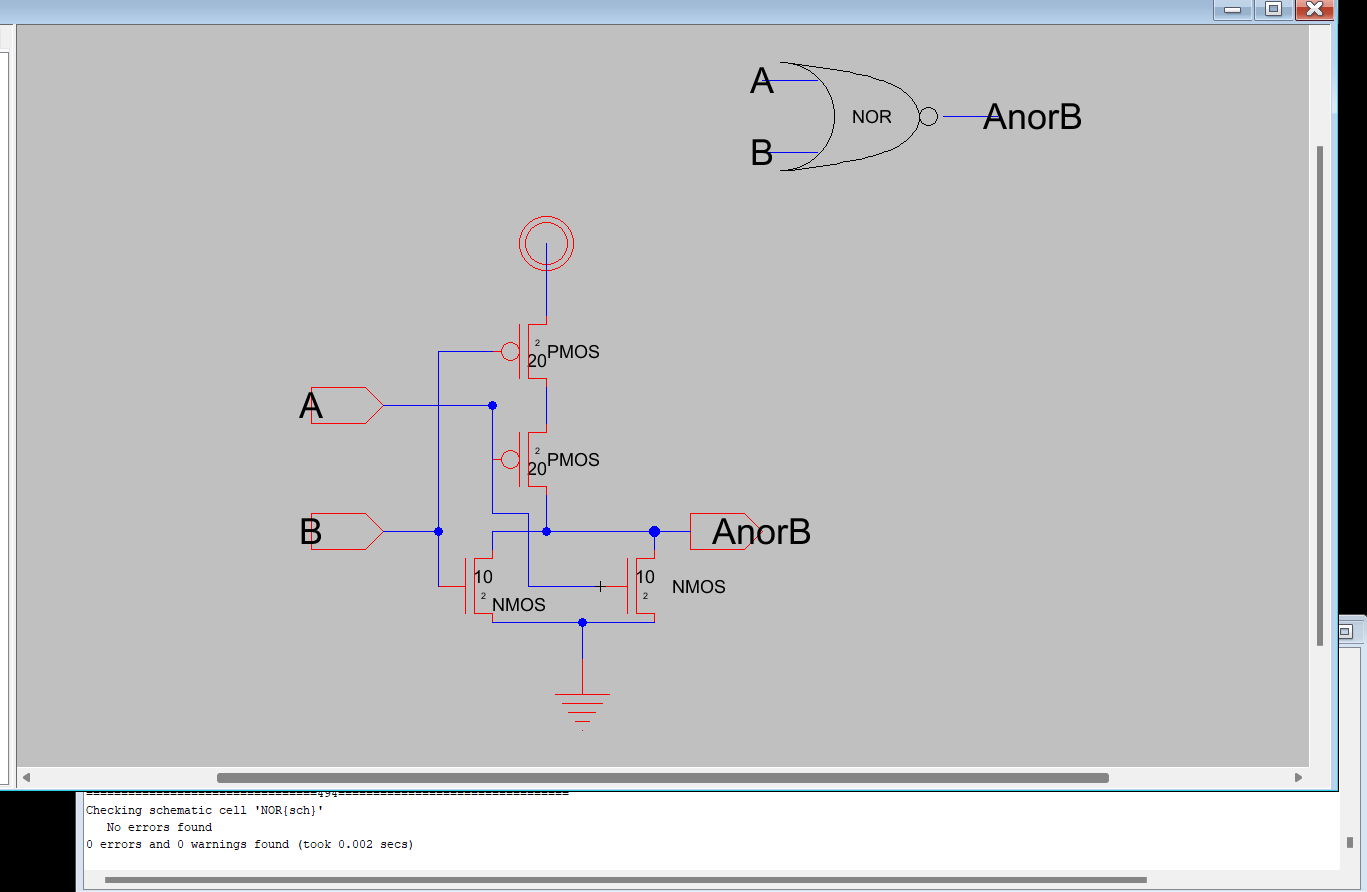

Figure 5: Error free schematic of NOR gate

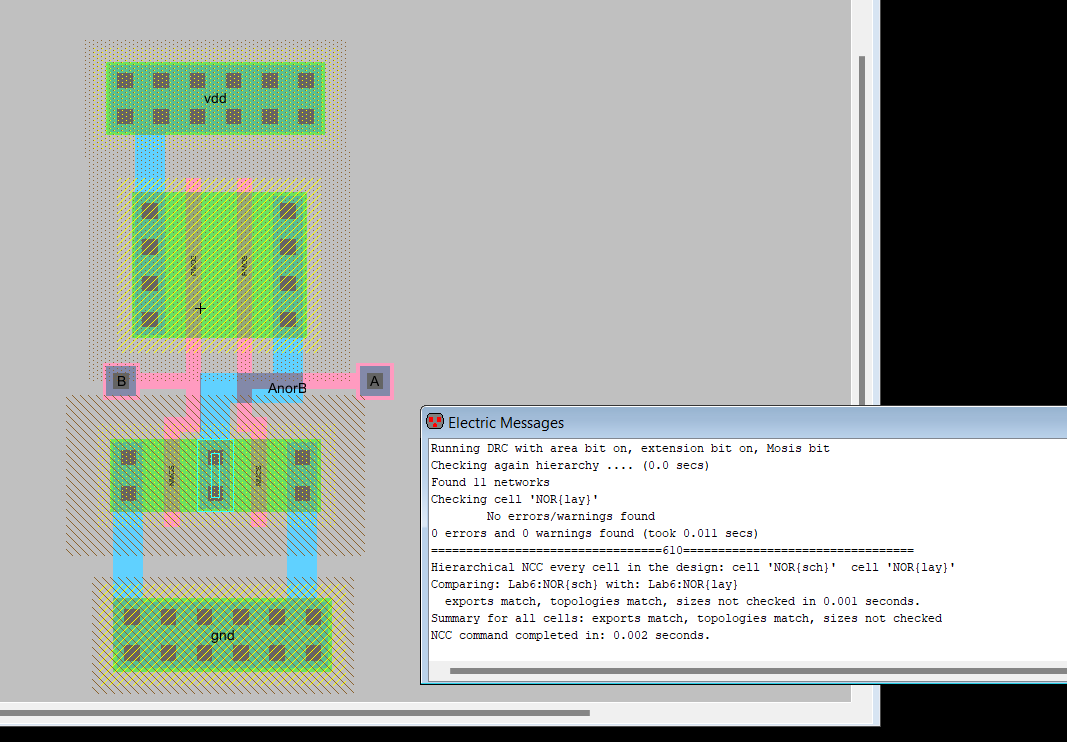

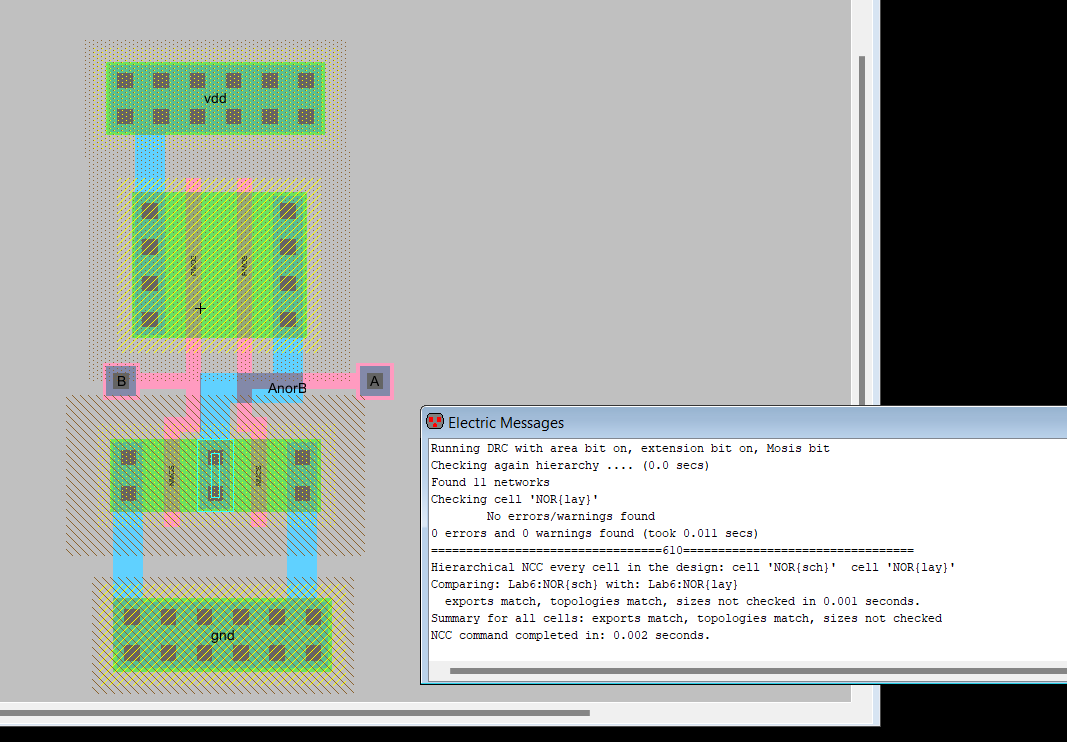

Figure 6: Error free layout of NOR

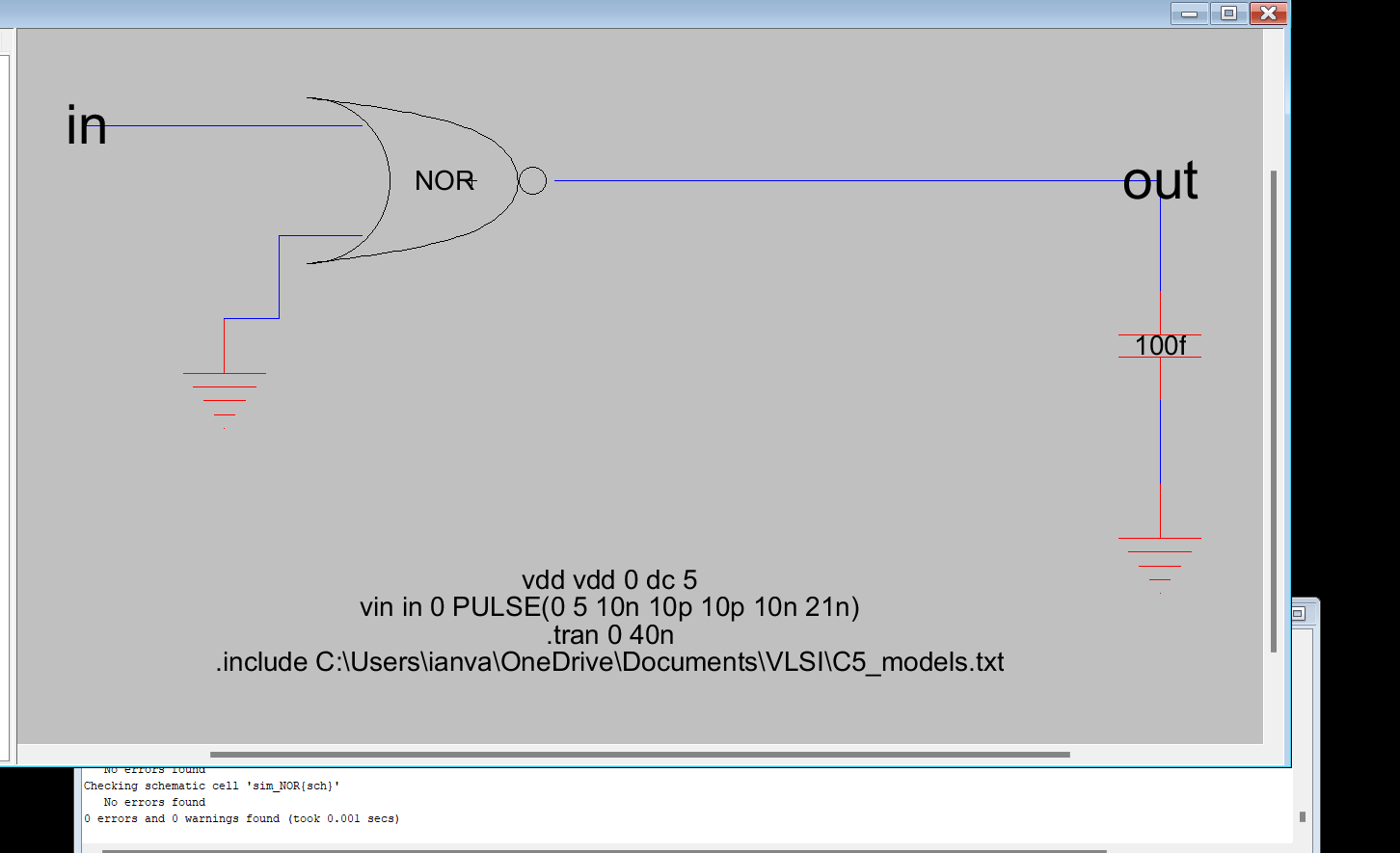

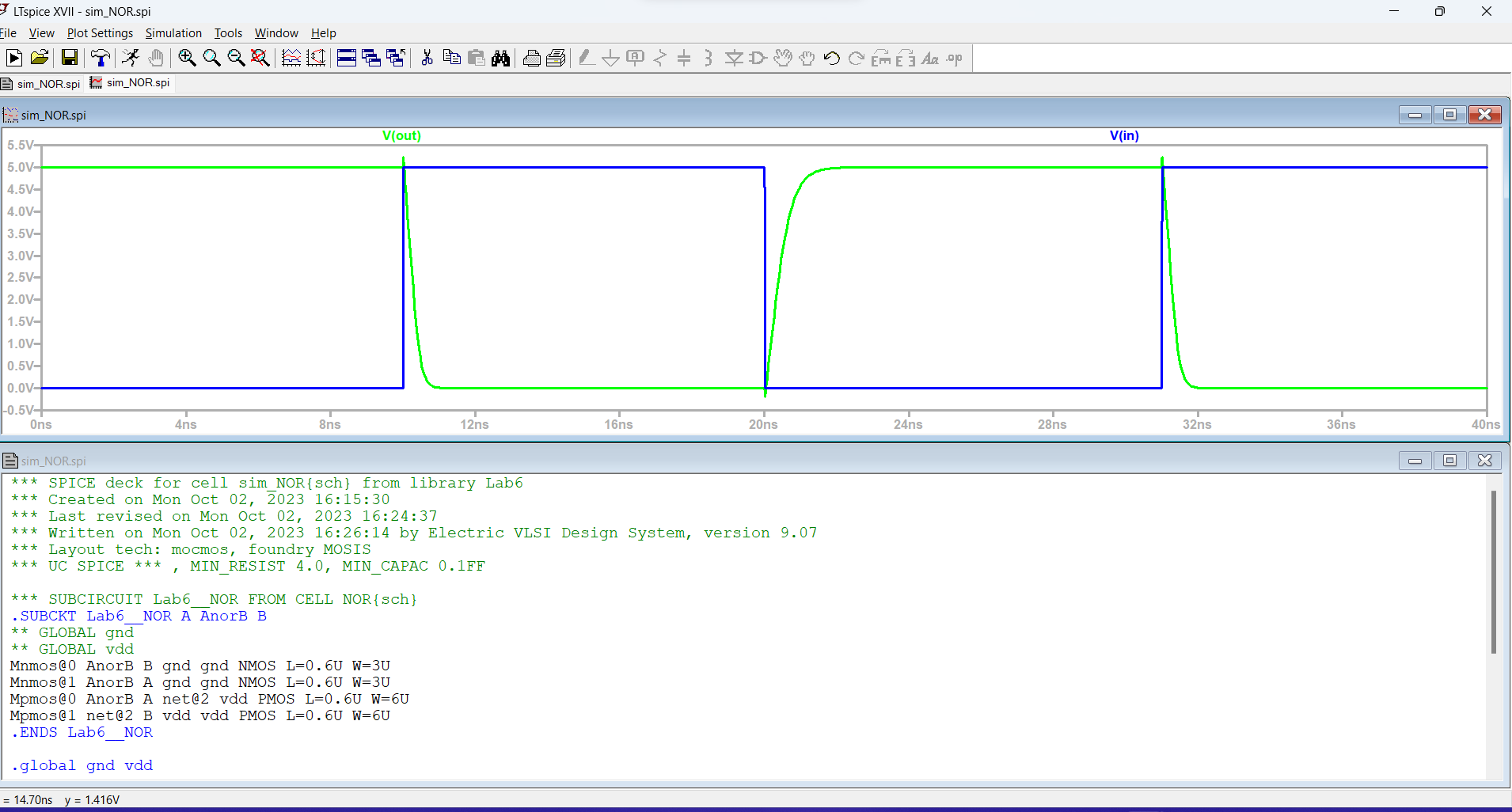

Figure 7: Error free schematic and spice code for NOR

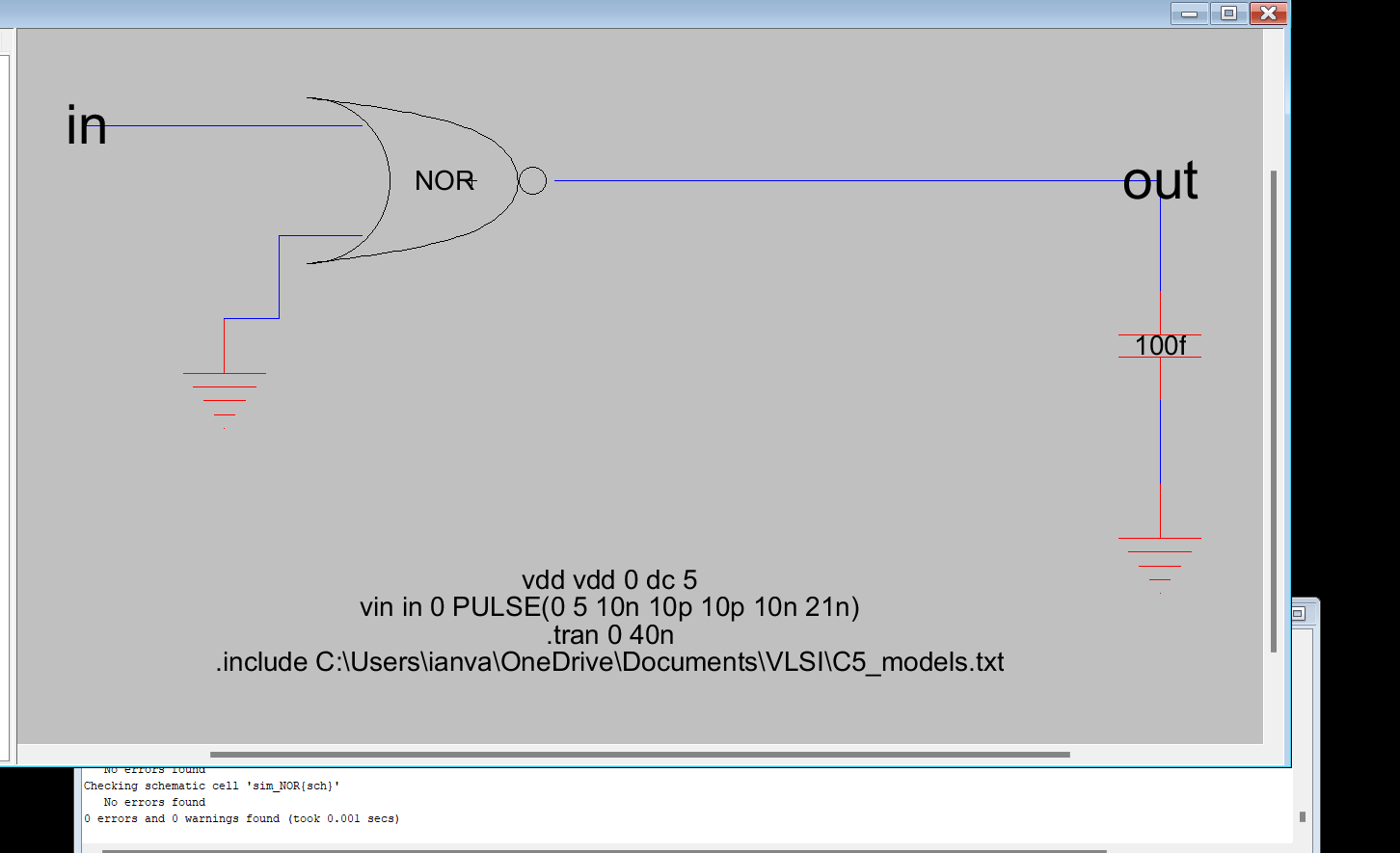

Figure 8: NOR SPICE simulation

Task 3: Design, simulate, and layout XOR gate. (30 points)

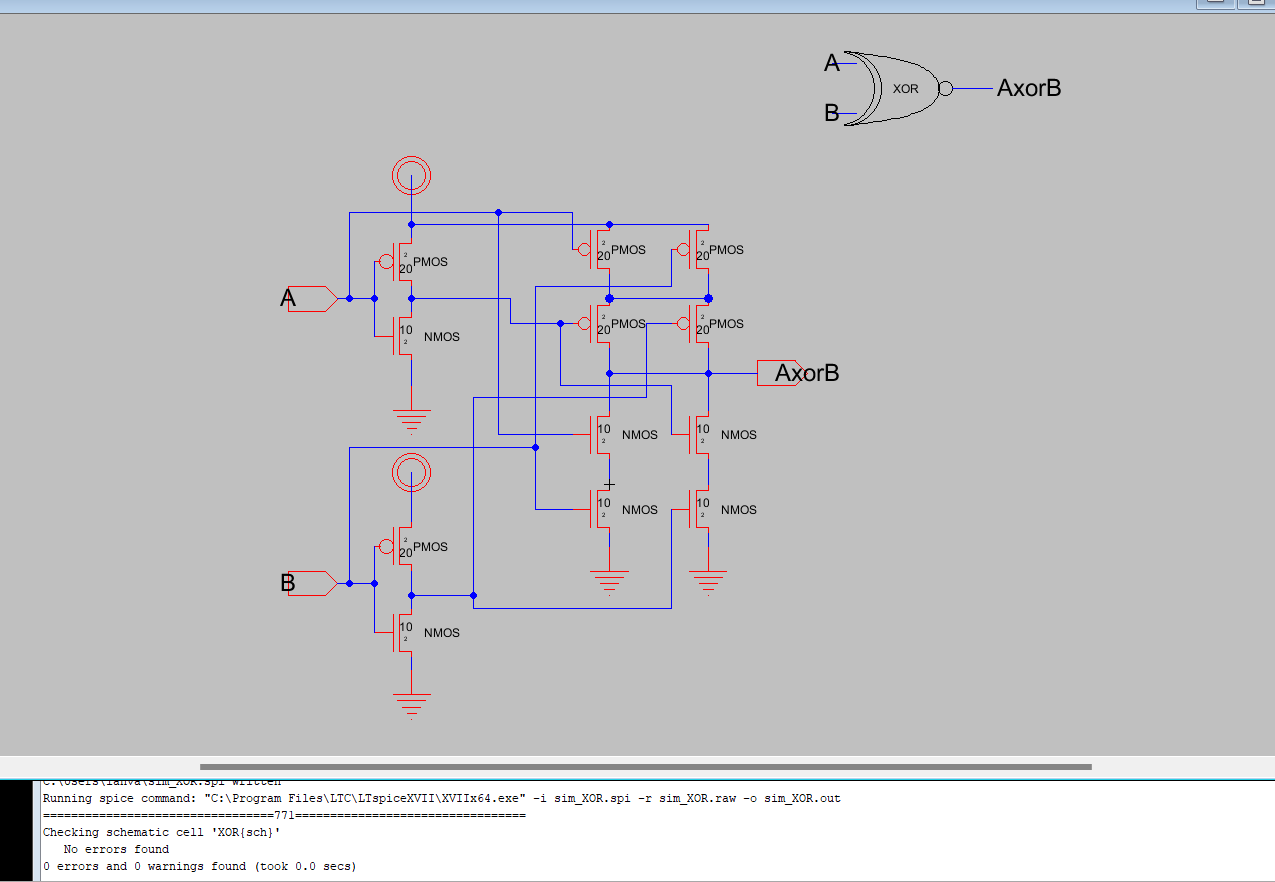

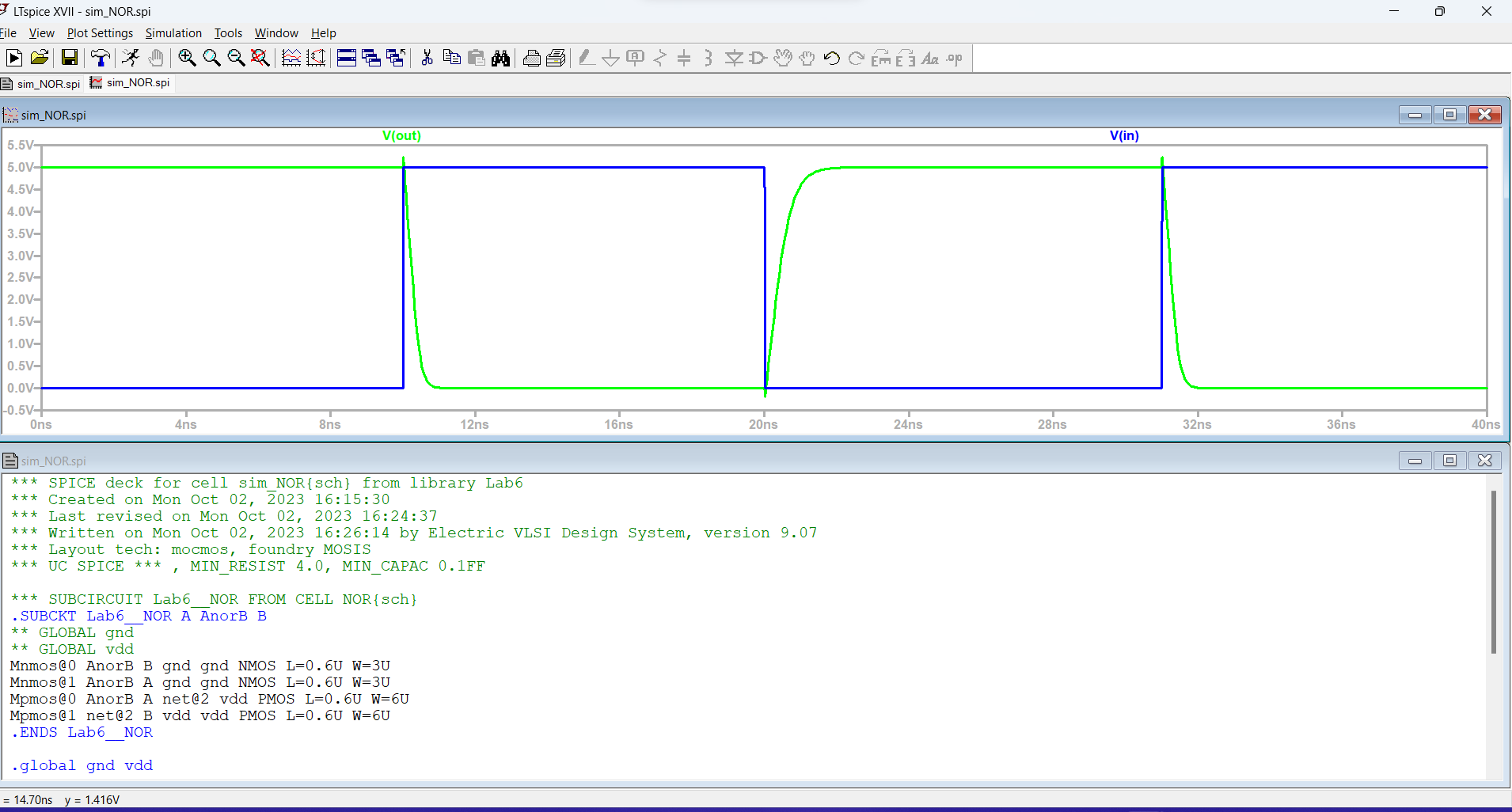

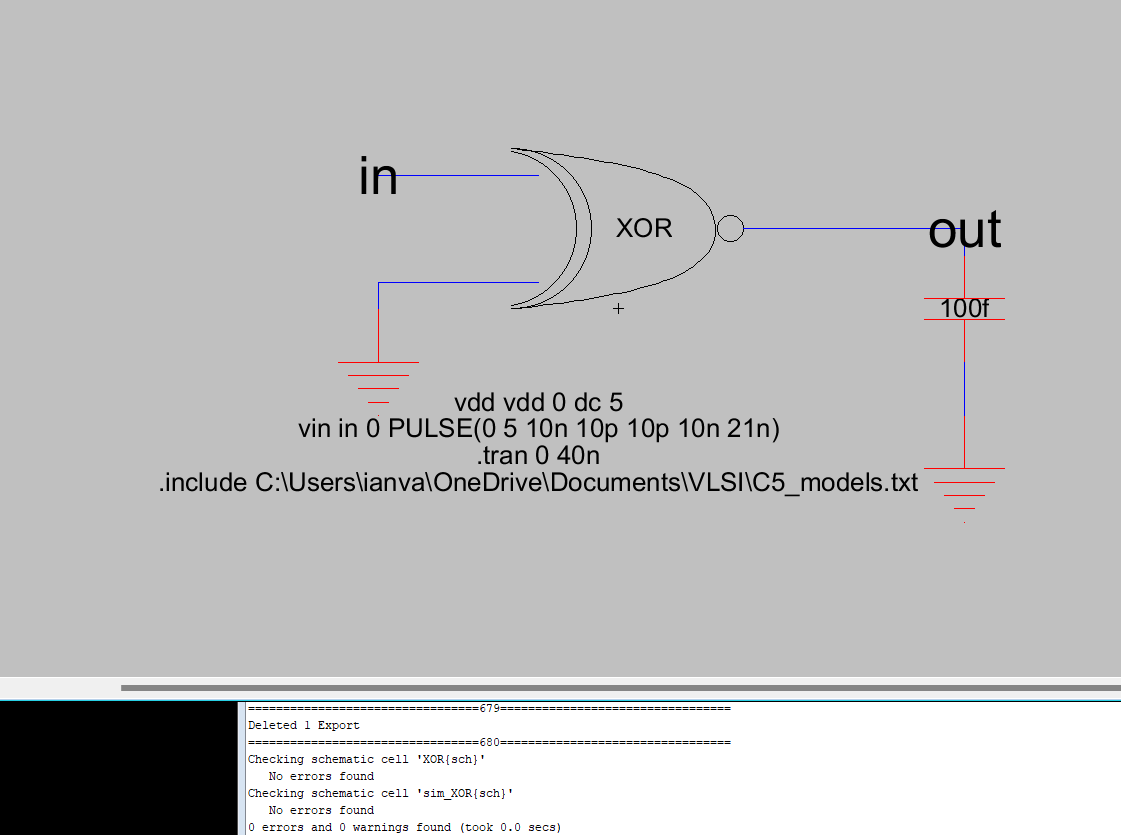

Figure 9: Error free XOR schematic

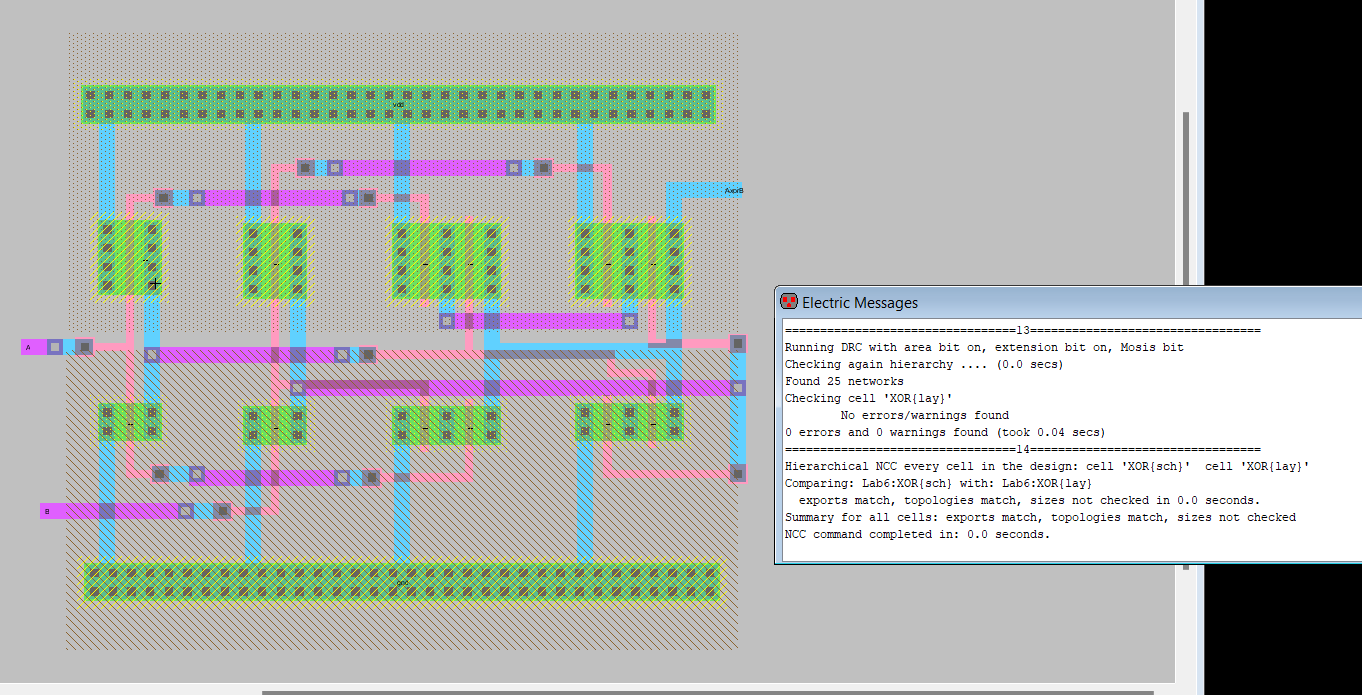

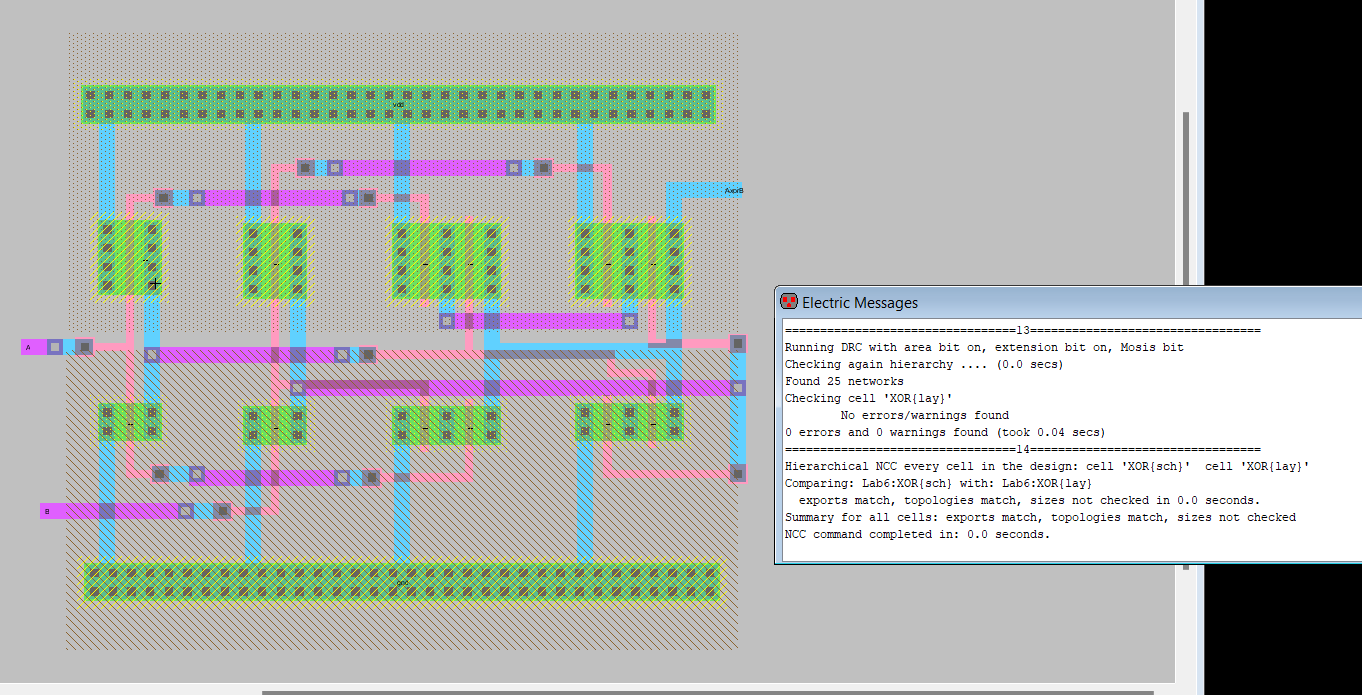

Figure 10: Error free XOR layout

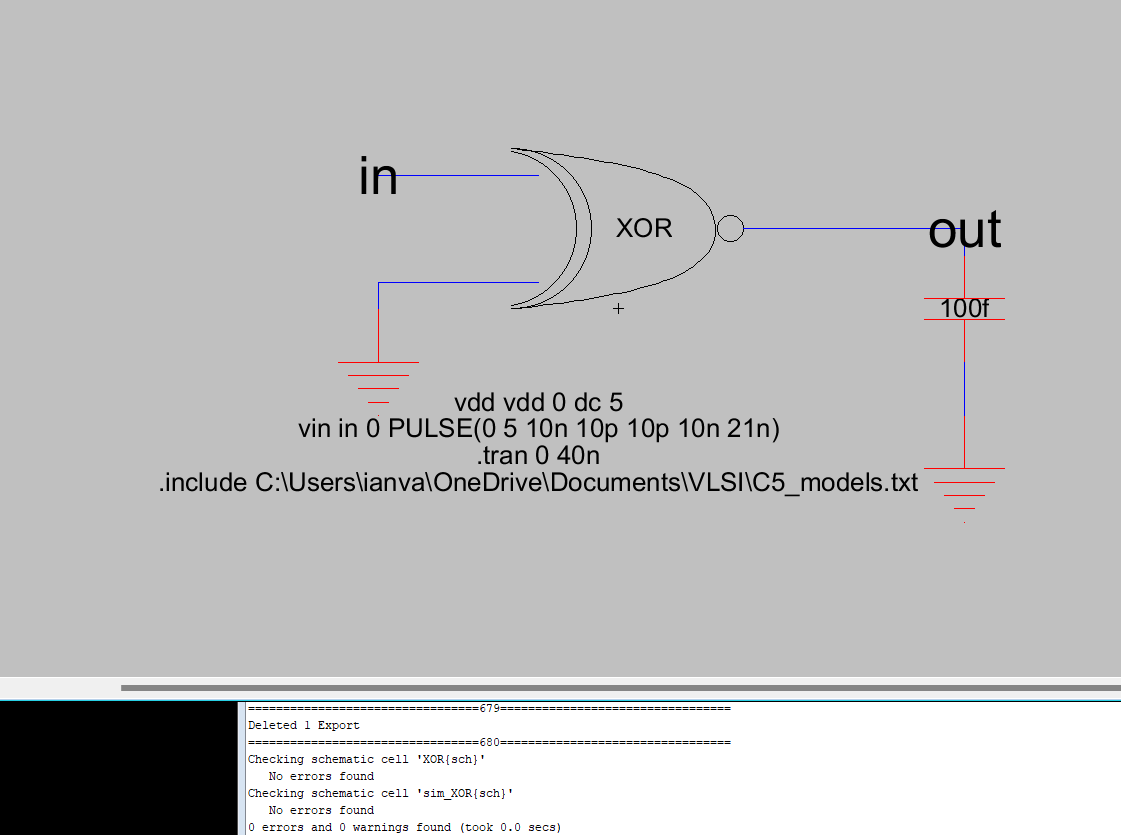

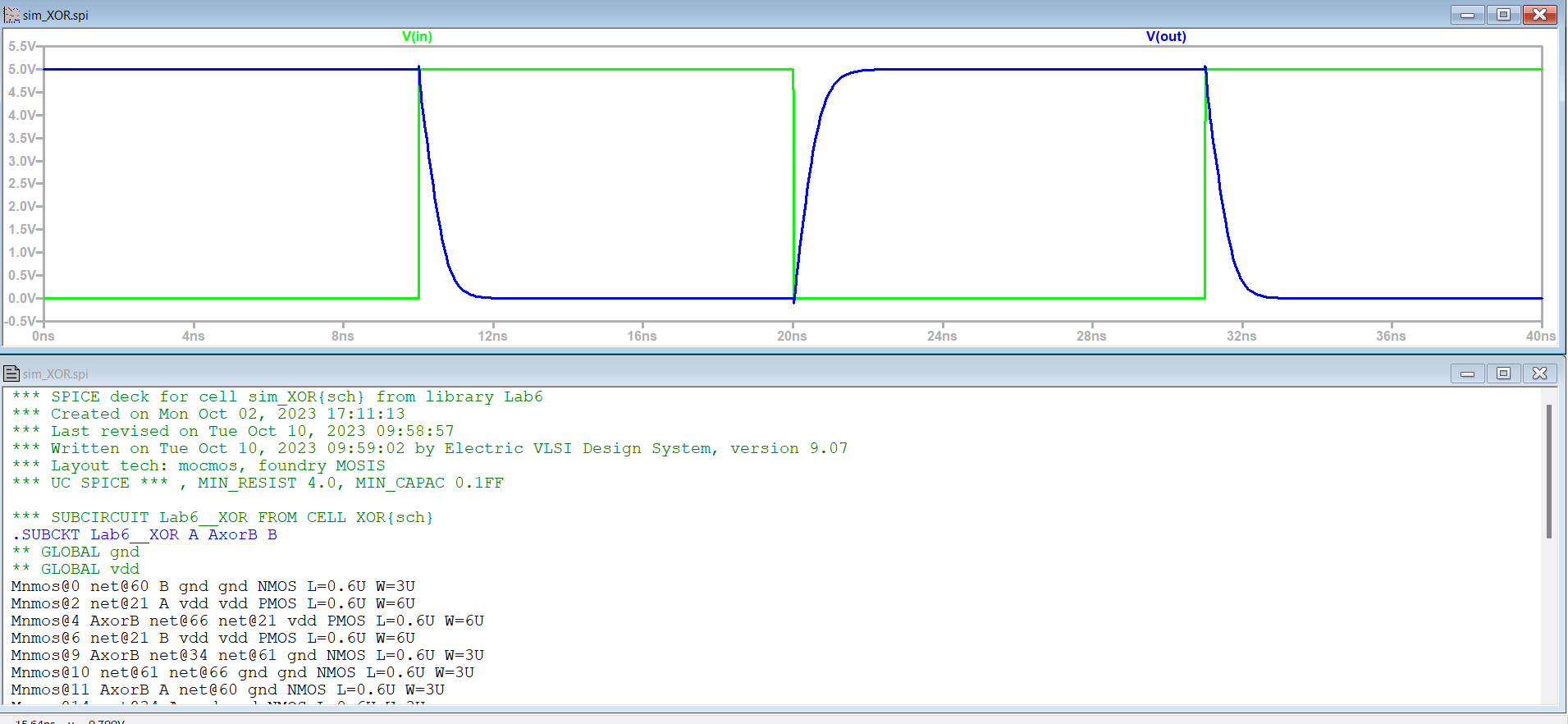

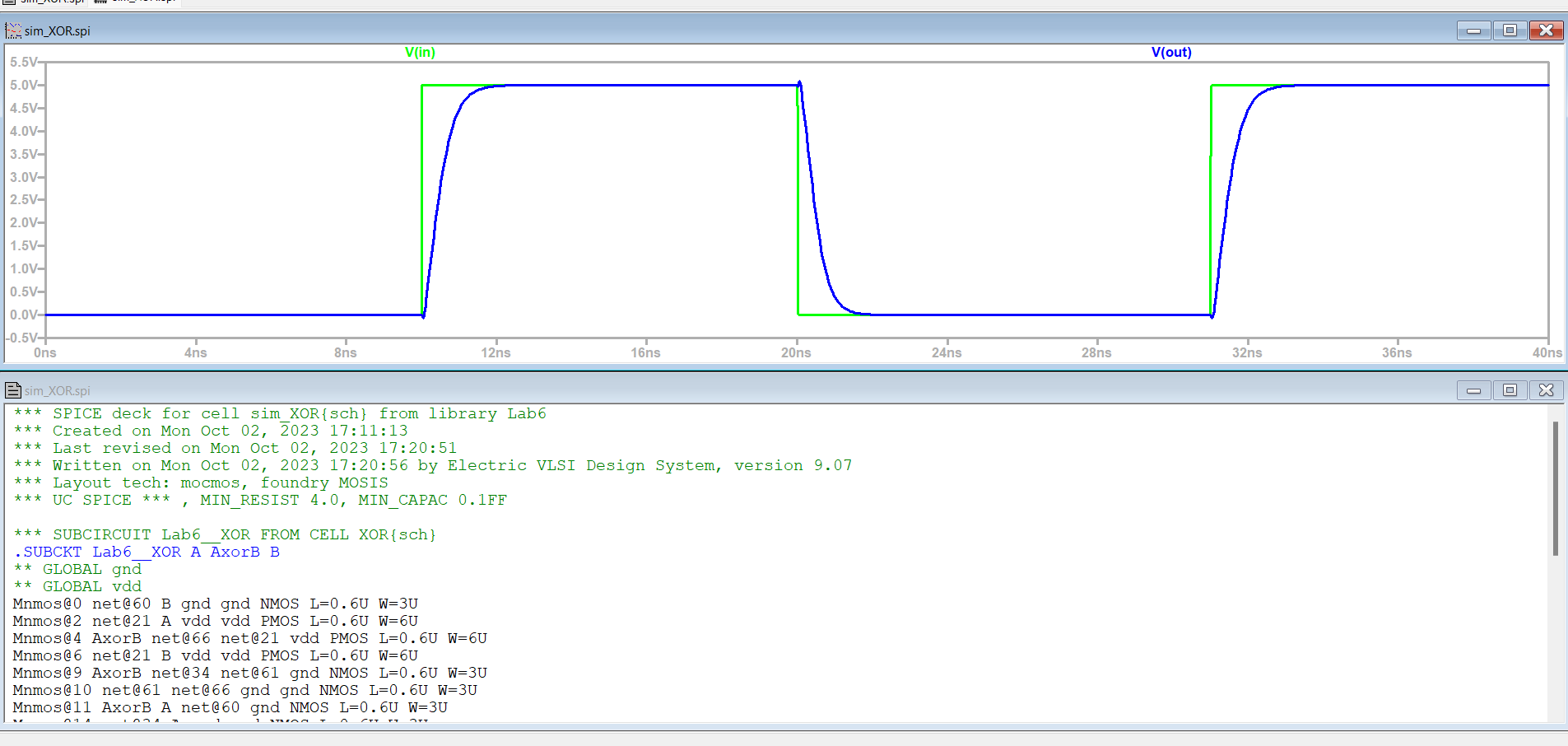

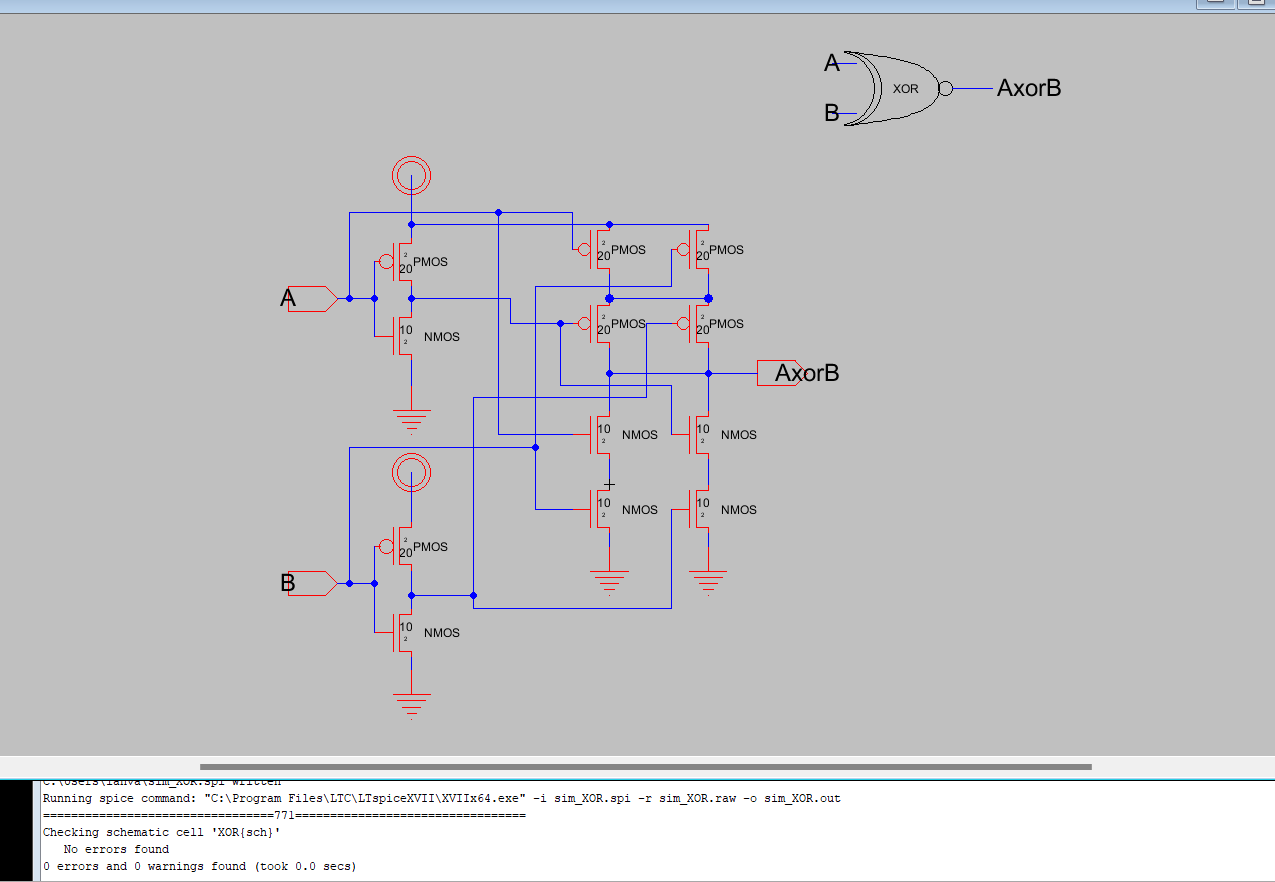

Figure 11: Error free XOR simulation schematic and spice code

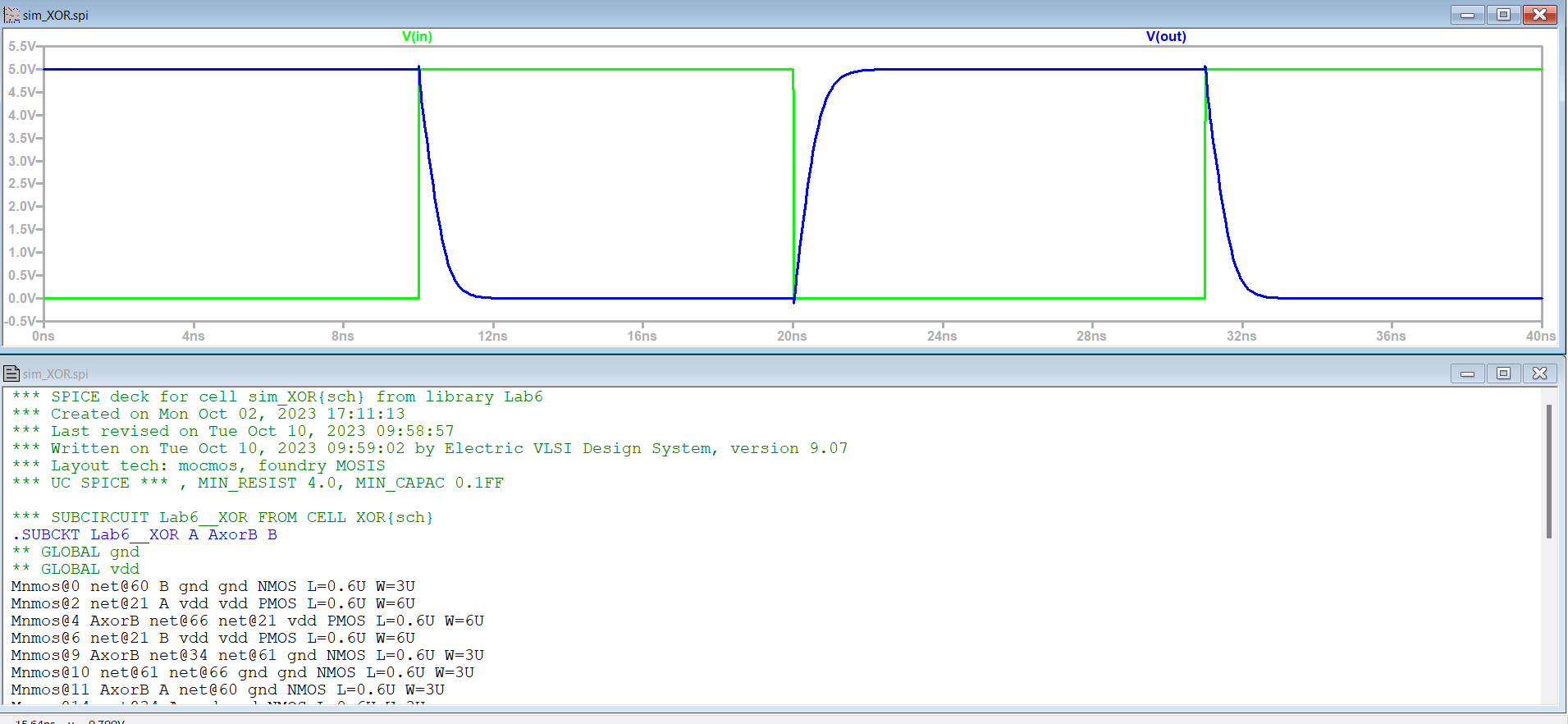

Figure 12: XOR spice sim

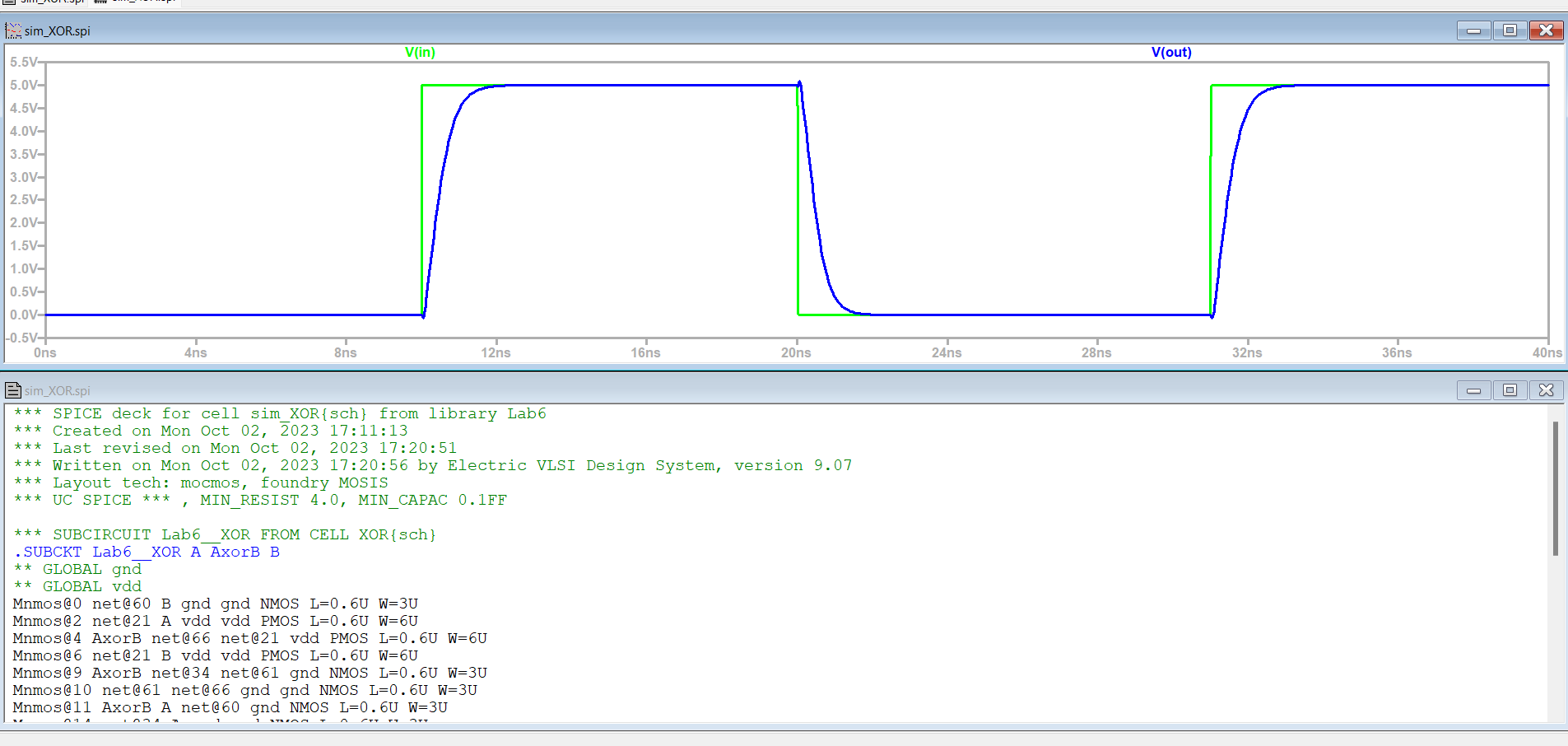

Figure 13: XOR spice simulation with gnd in palce of Vdd

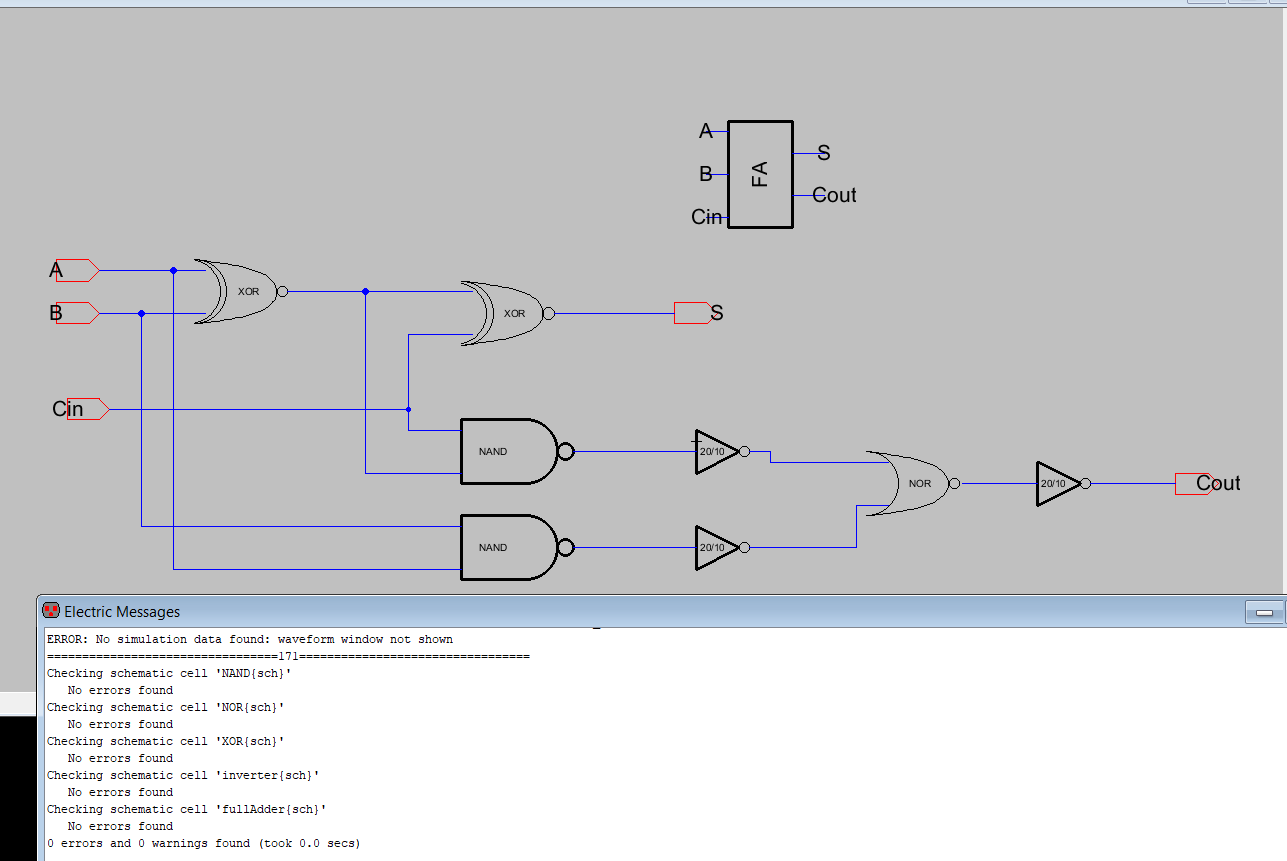

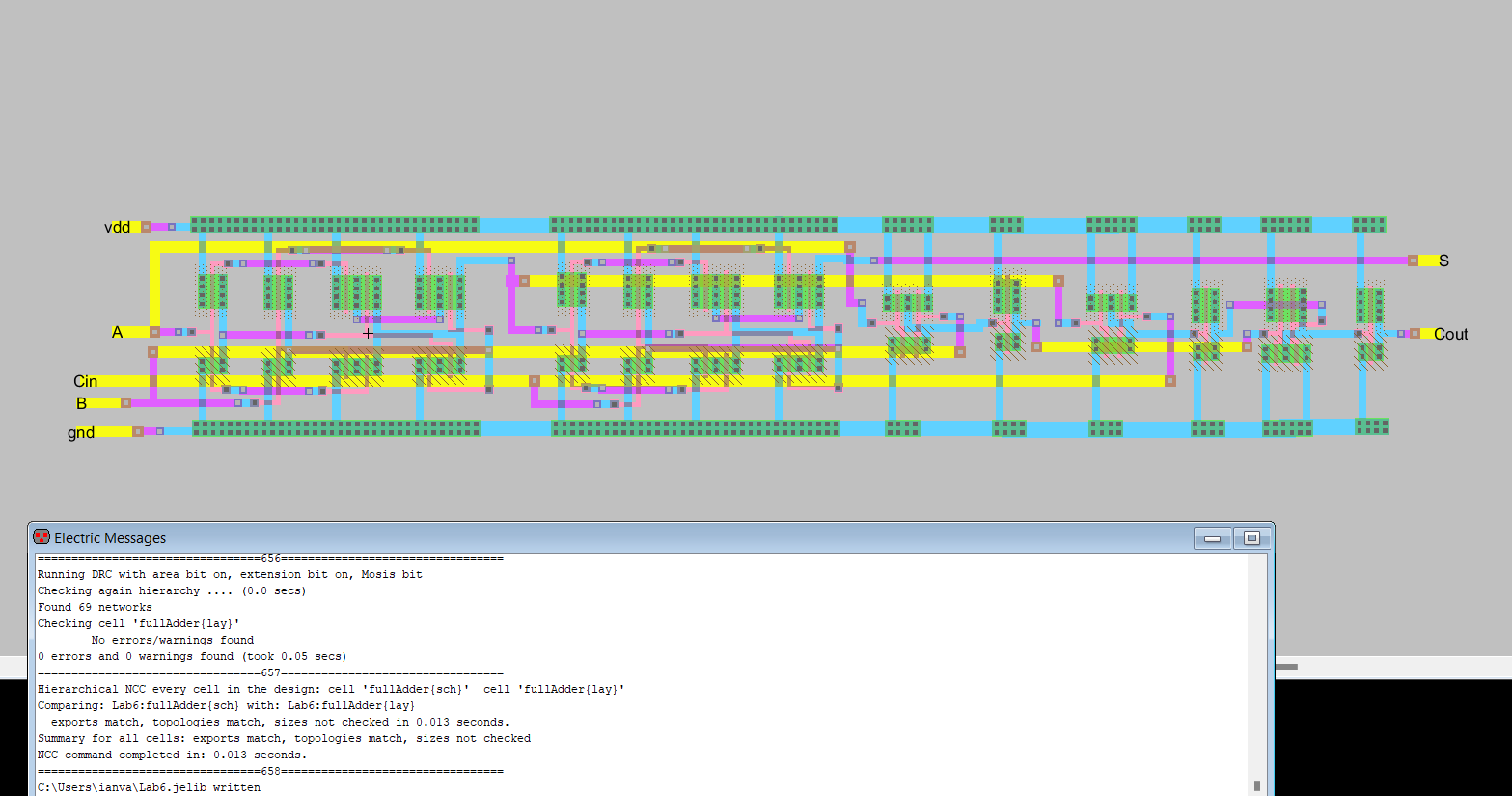

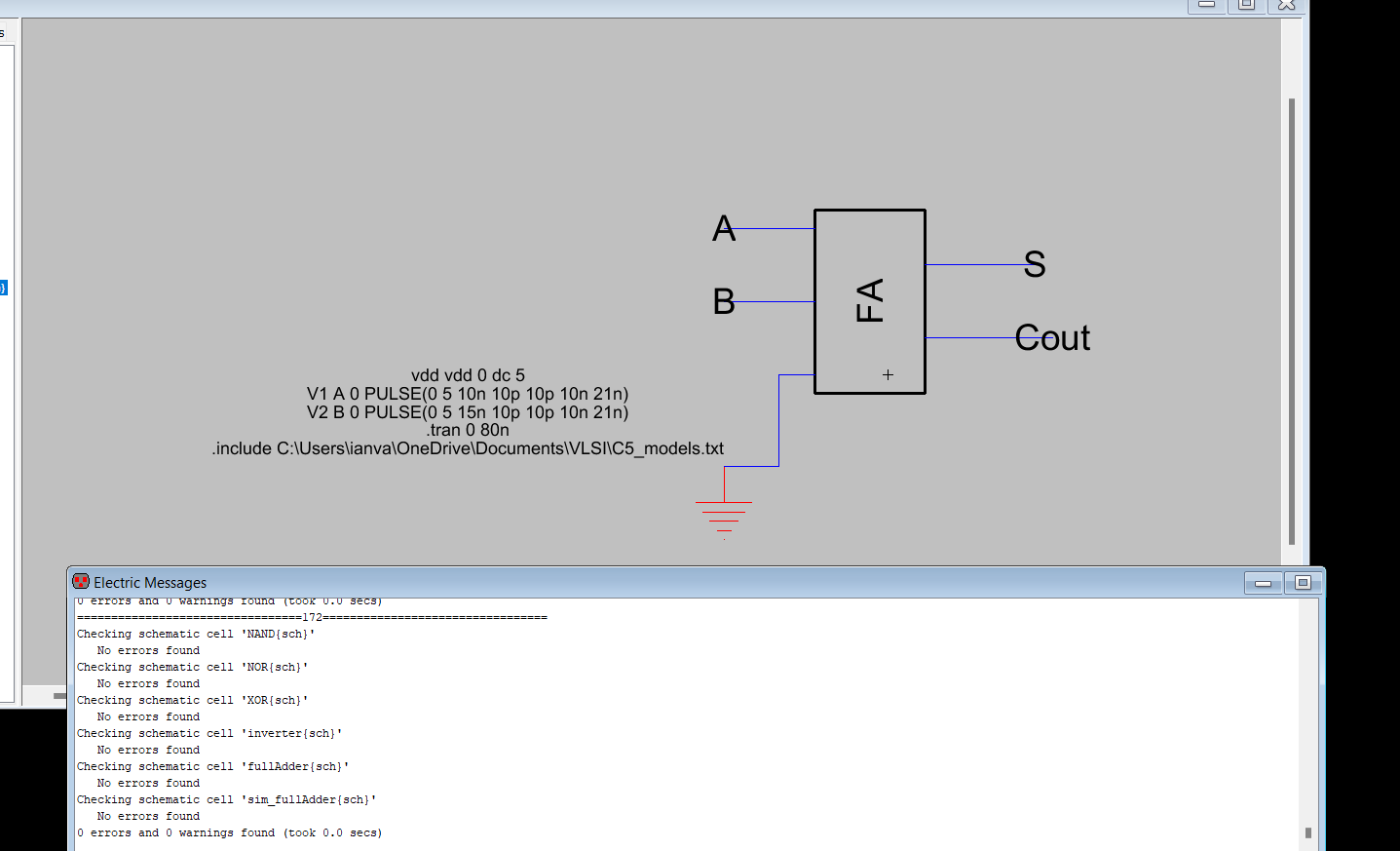

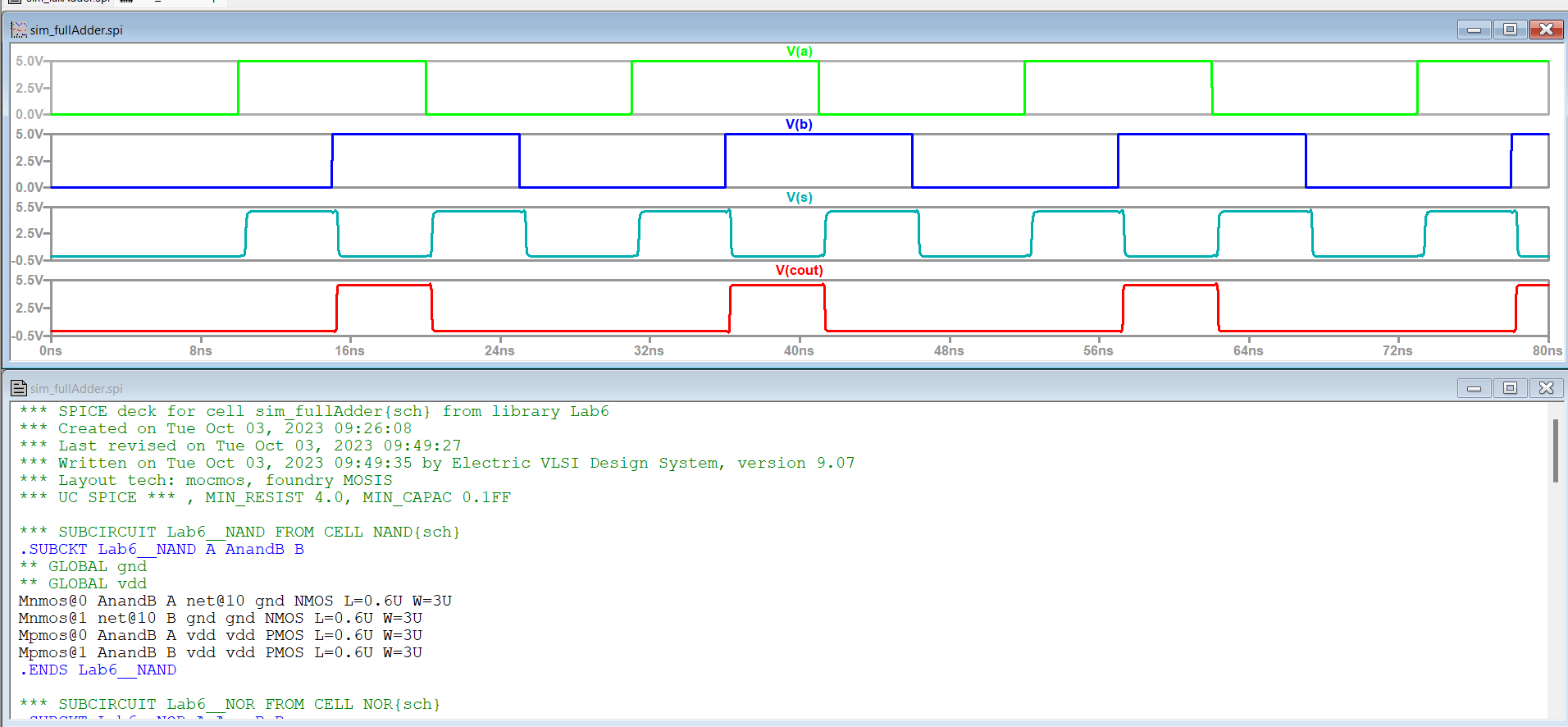

Task 4: Design, simulate, and layout Full Adder. (30 points)

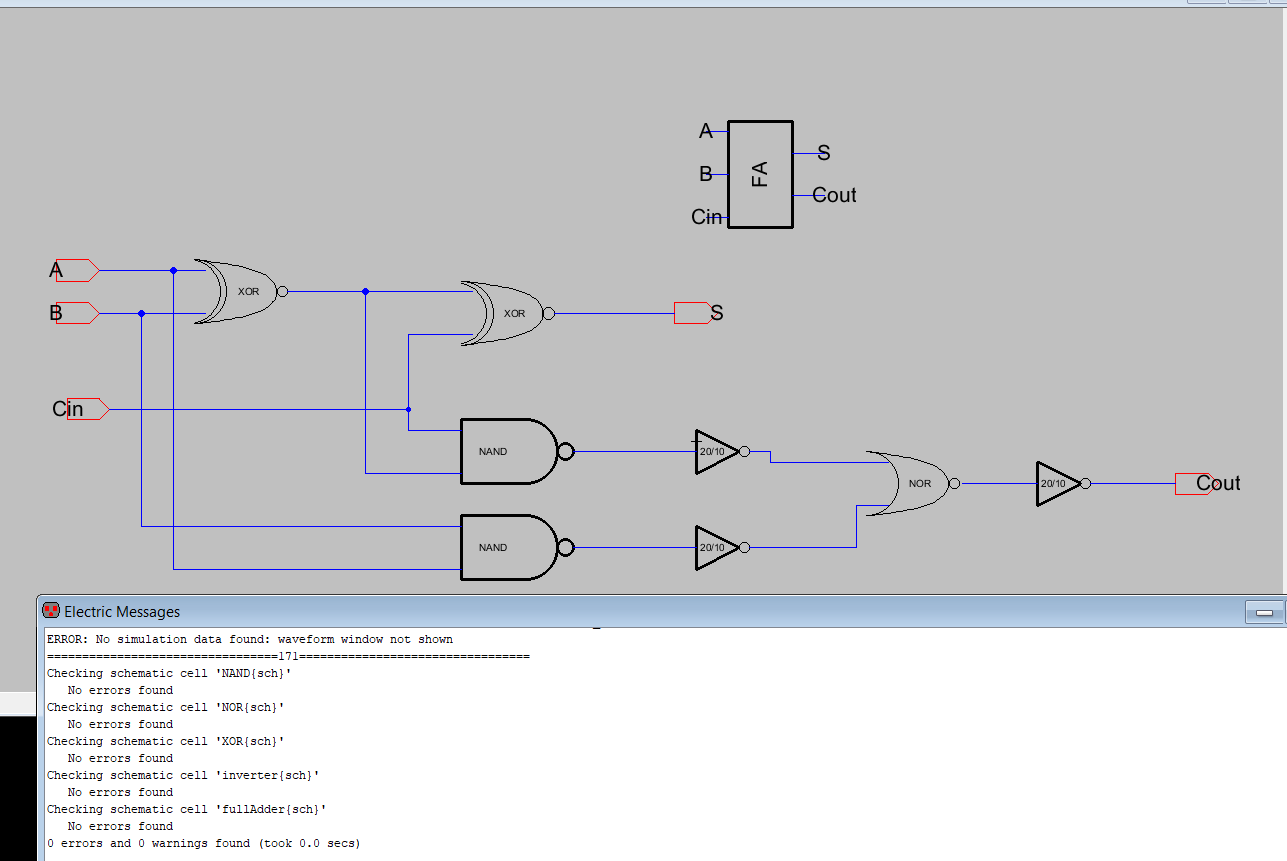

Figure 14: Error free Full Adder schematic

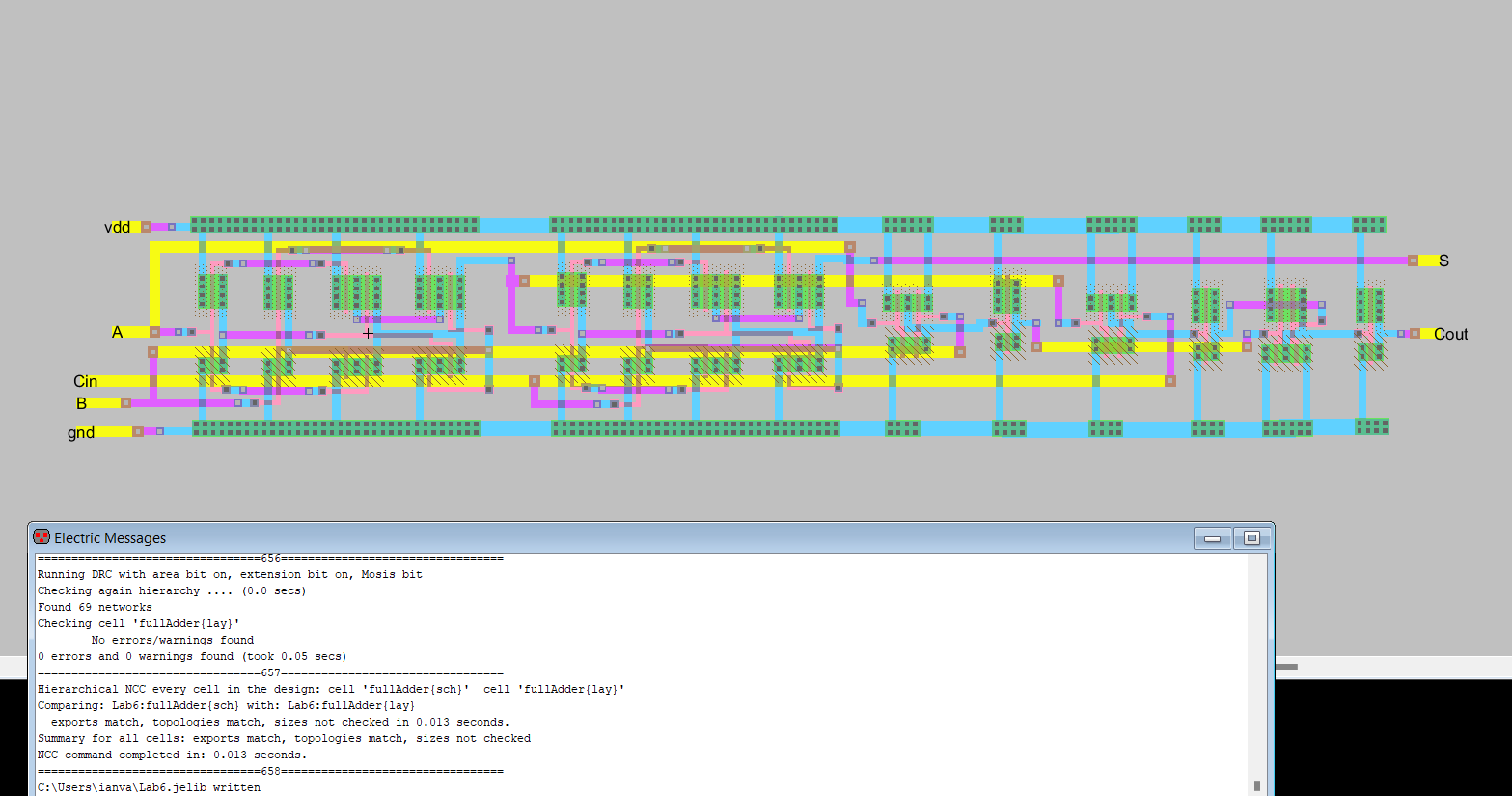

Figure 15: Error free Full Adder layout

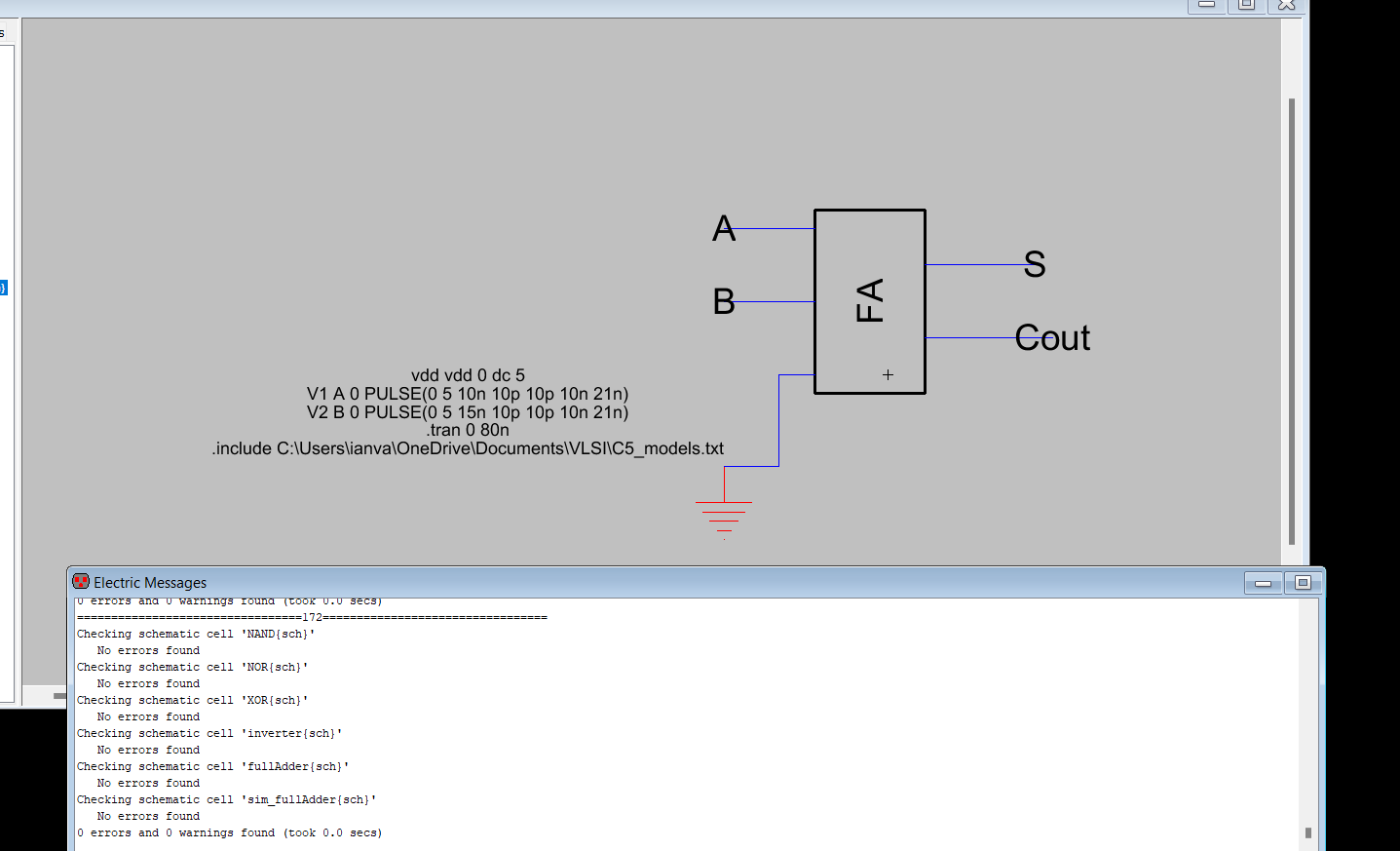

Figure 16: Error free Full Adder simulation schematic and spice code

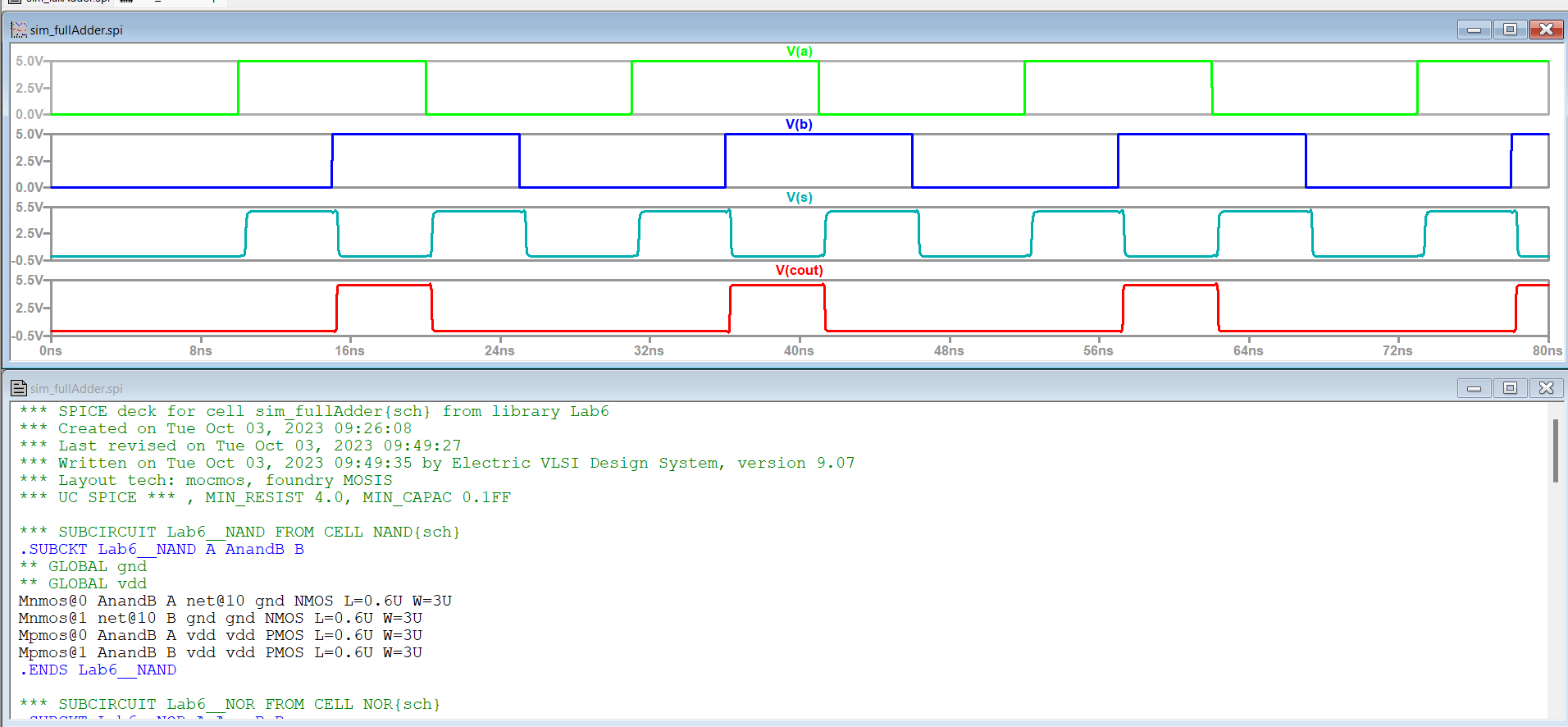

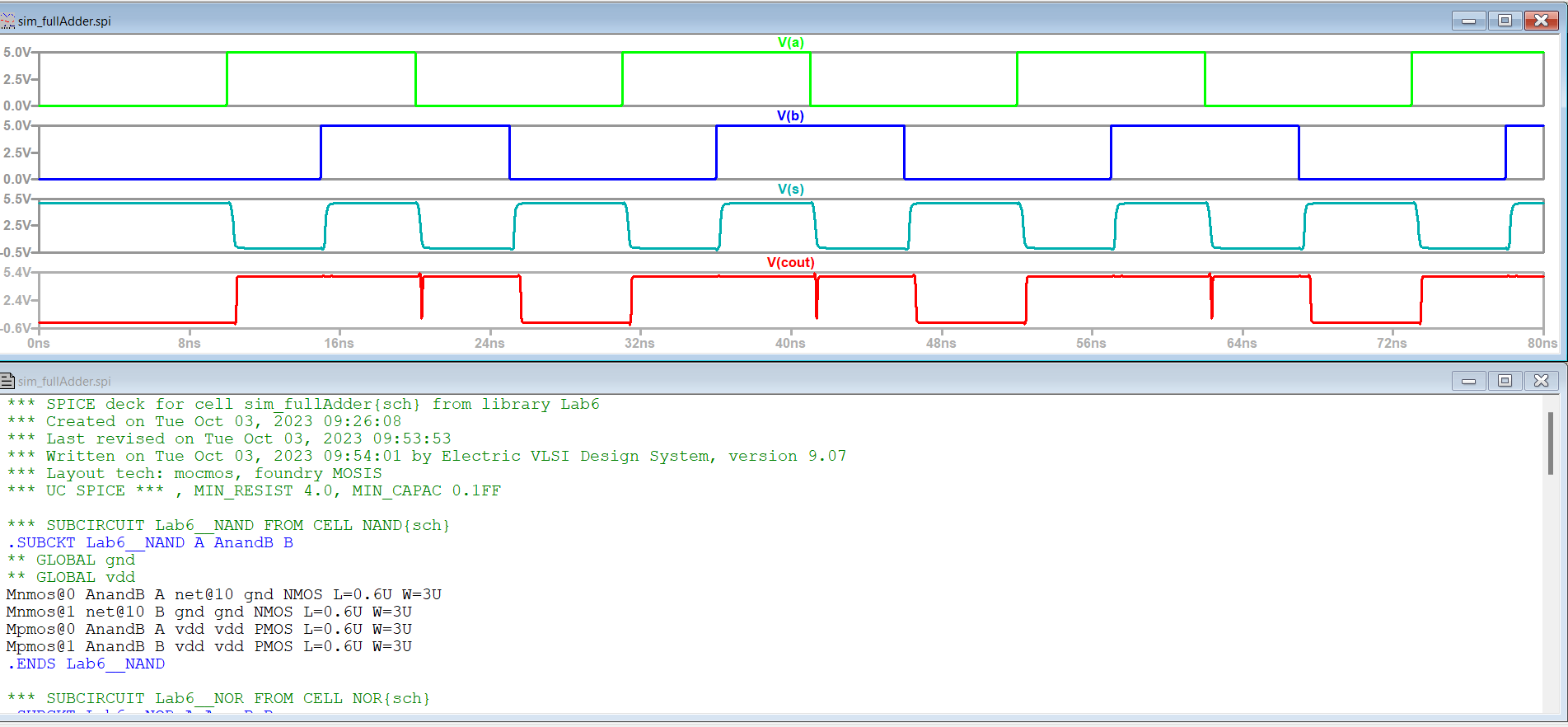

Figure 17: Full Adder spice simulation

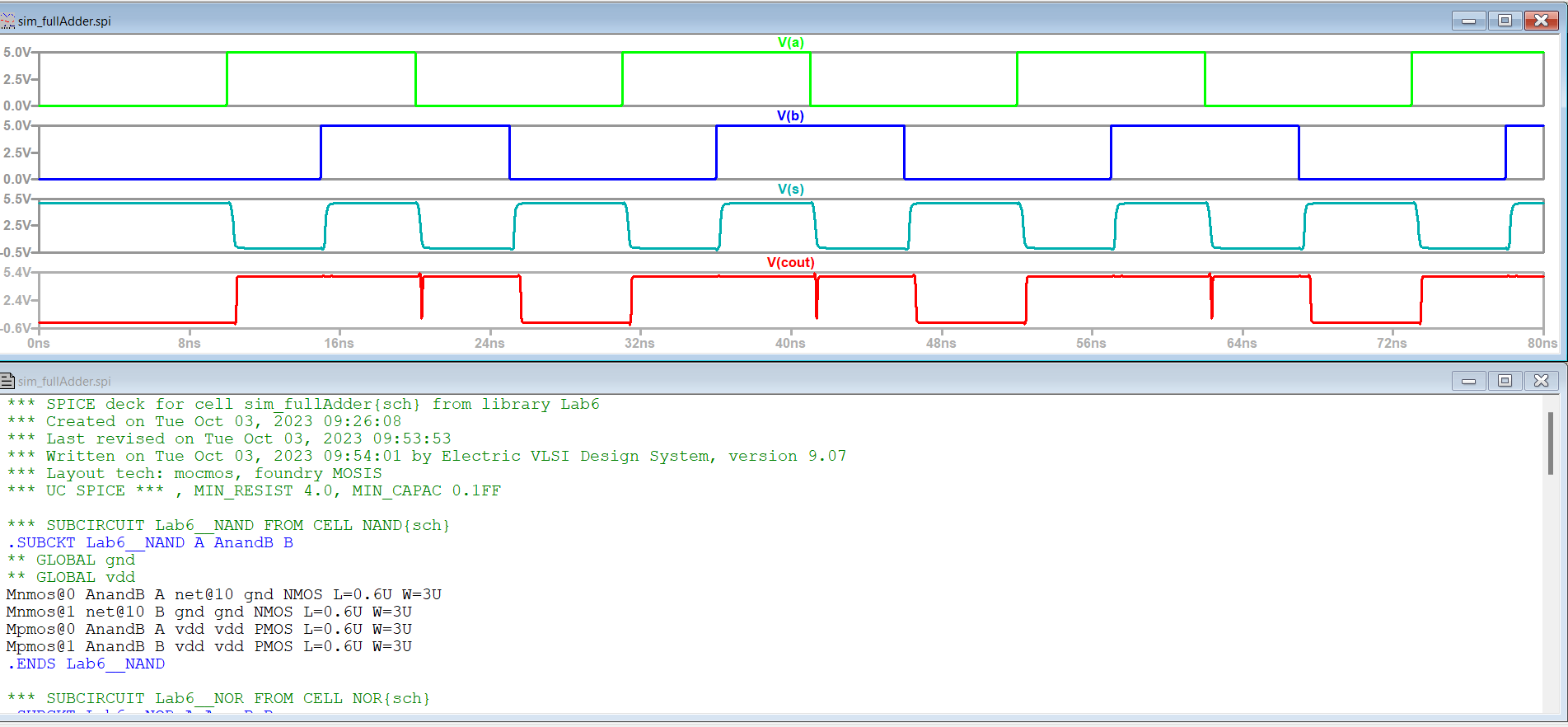

Figure 18: Full Adder spice simulation with Vdd in place of gnd

Conclusion: This lab provided excellent practice with the layout of logic gates