ENGR 338 - Lab 4 2023 Fall

Name: Ian Van Horn

Email: imvanhorn1@gmail.com

Lab 5: The Inverter

This lab coveres the layout and simulation of an inverter in eletric VLSI

This lab requires the Eletric VLSI software

Task 1: Create the schematic of the inverter (30 points).

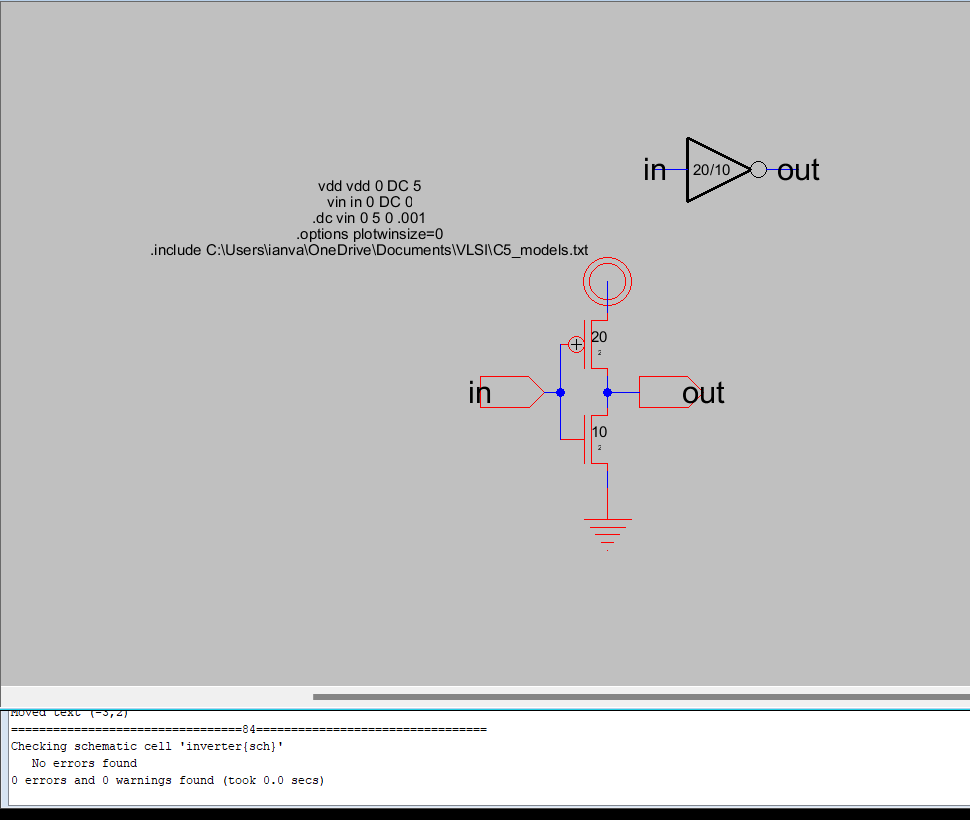

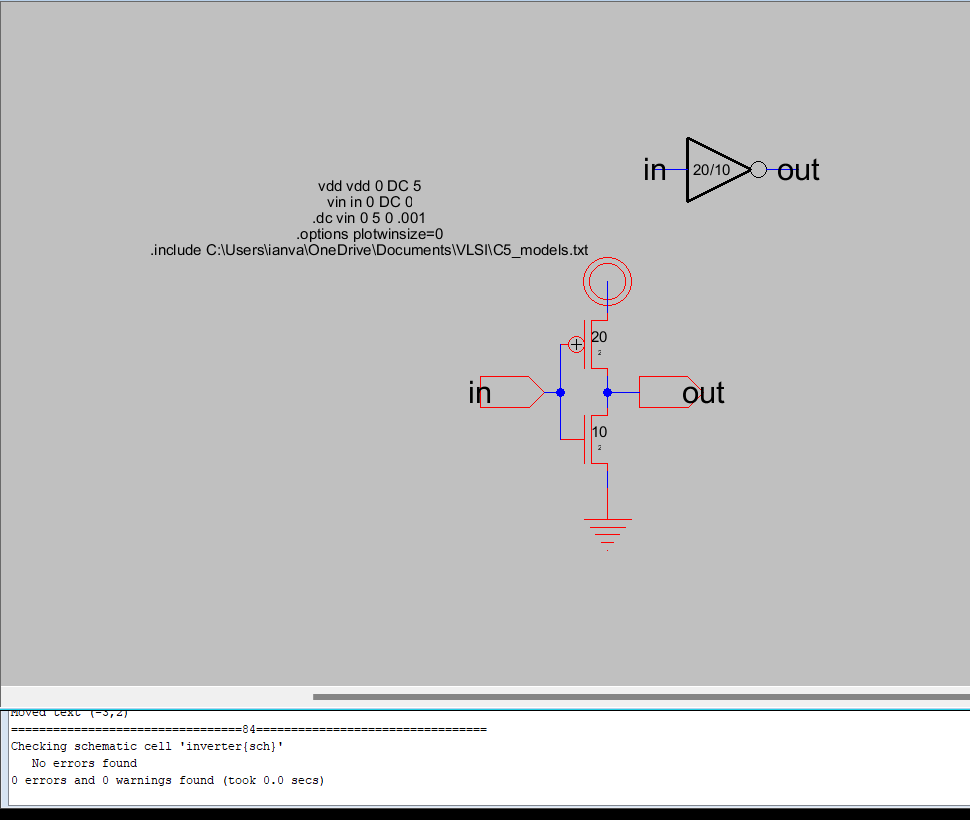

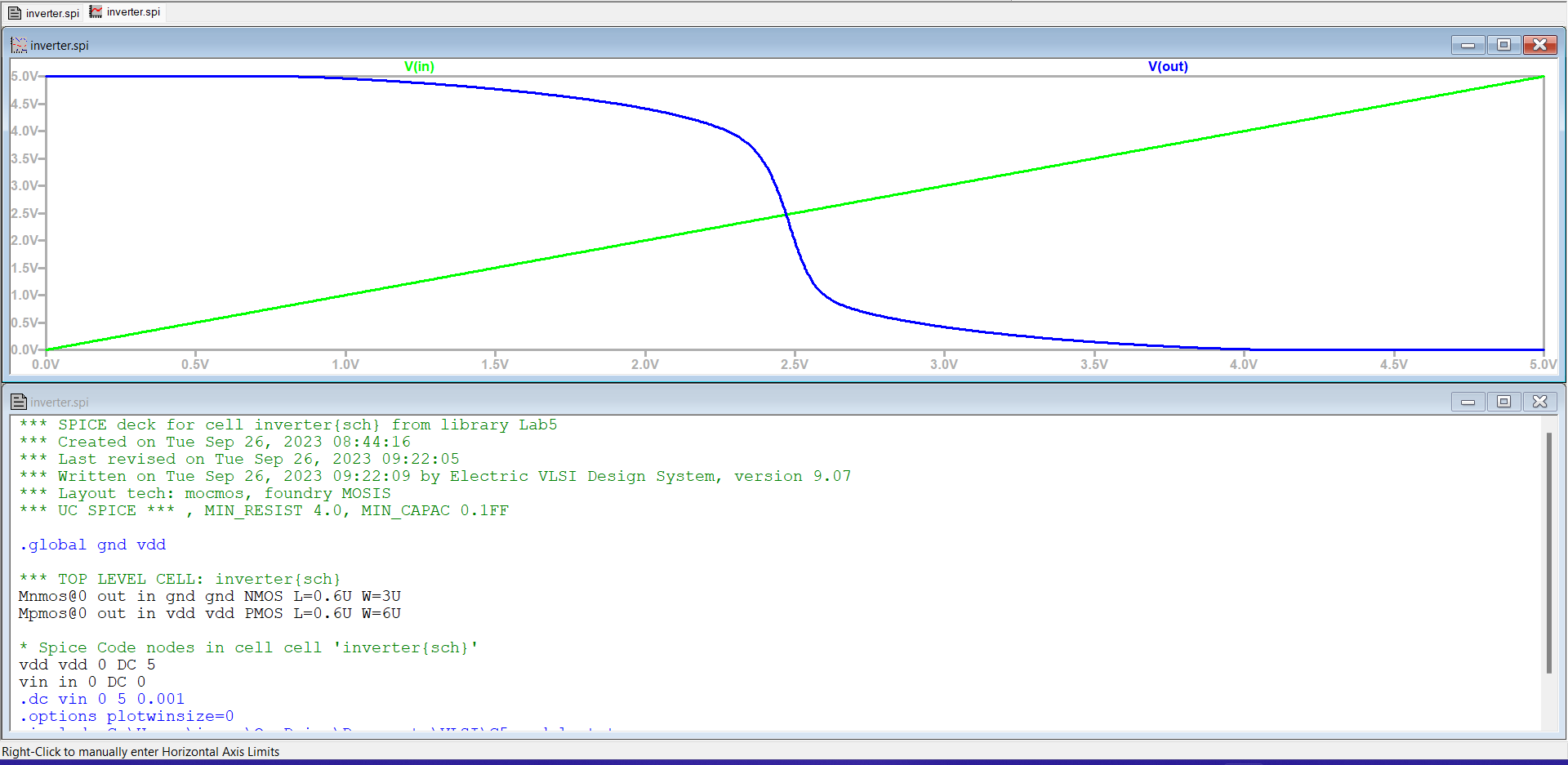

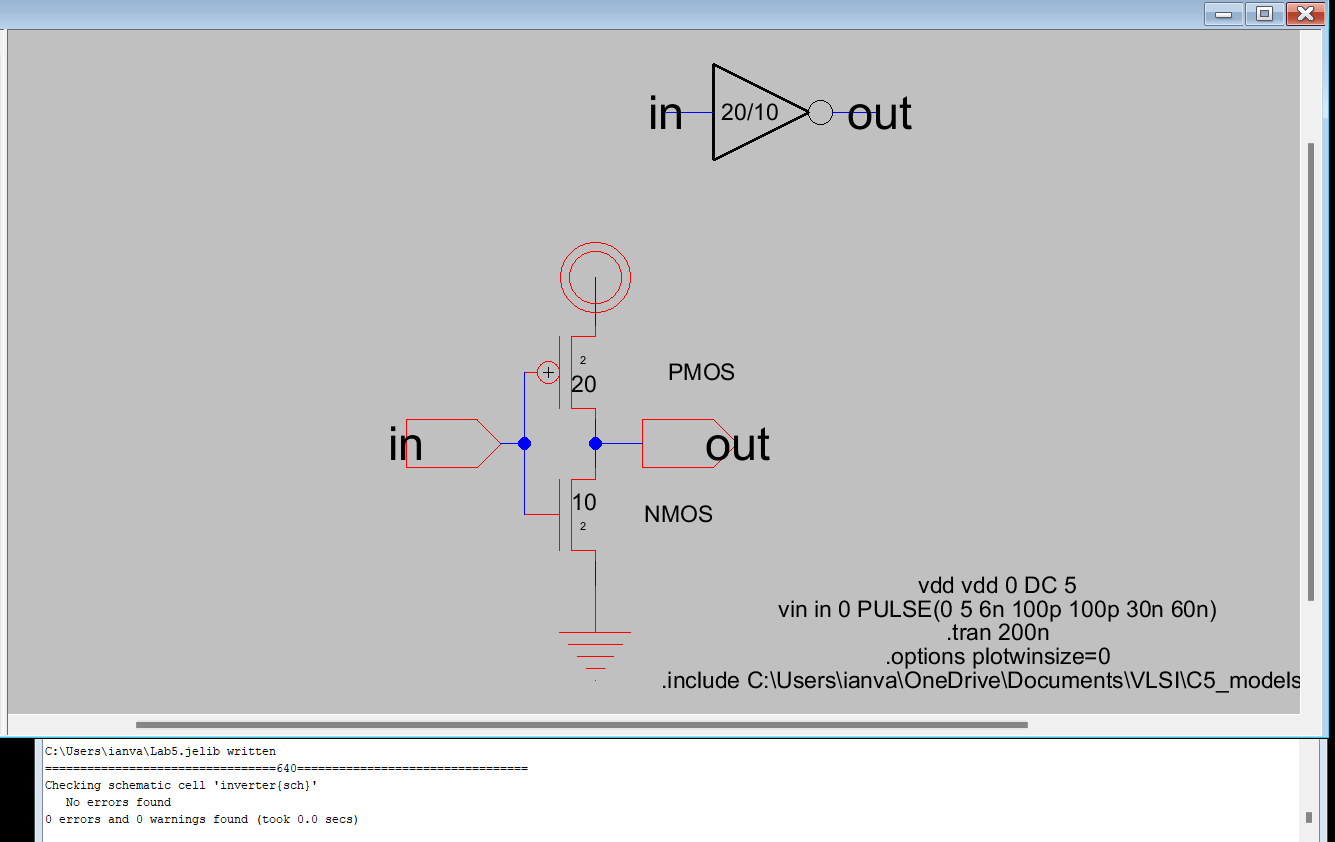

Figure 1: Inverter Schematic (error free) with DC Sweep Spice code

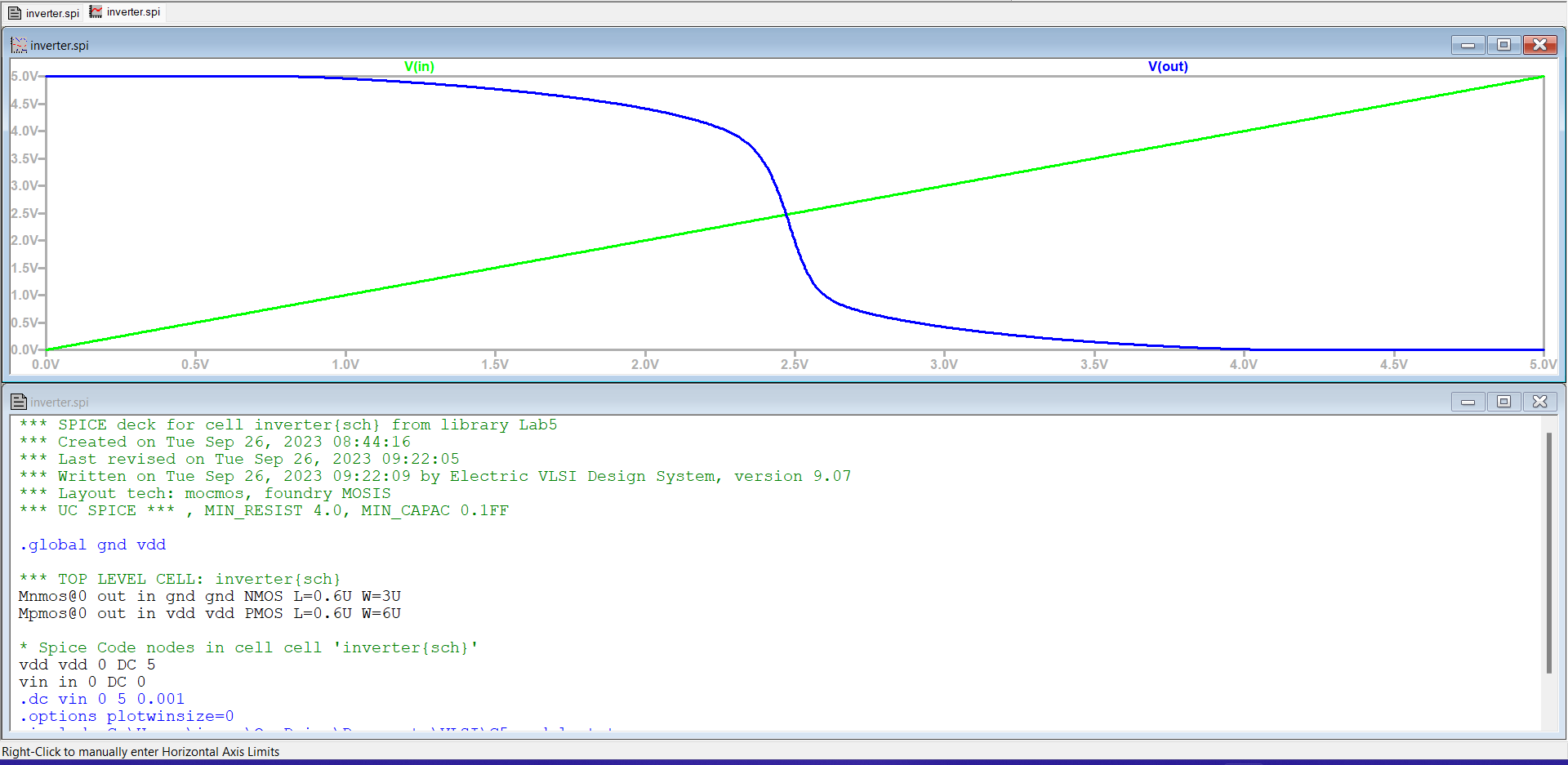

Figure 2. Inverter DC Sweep Spice Sim

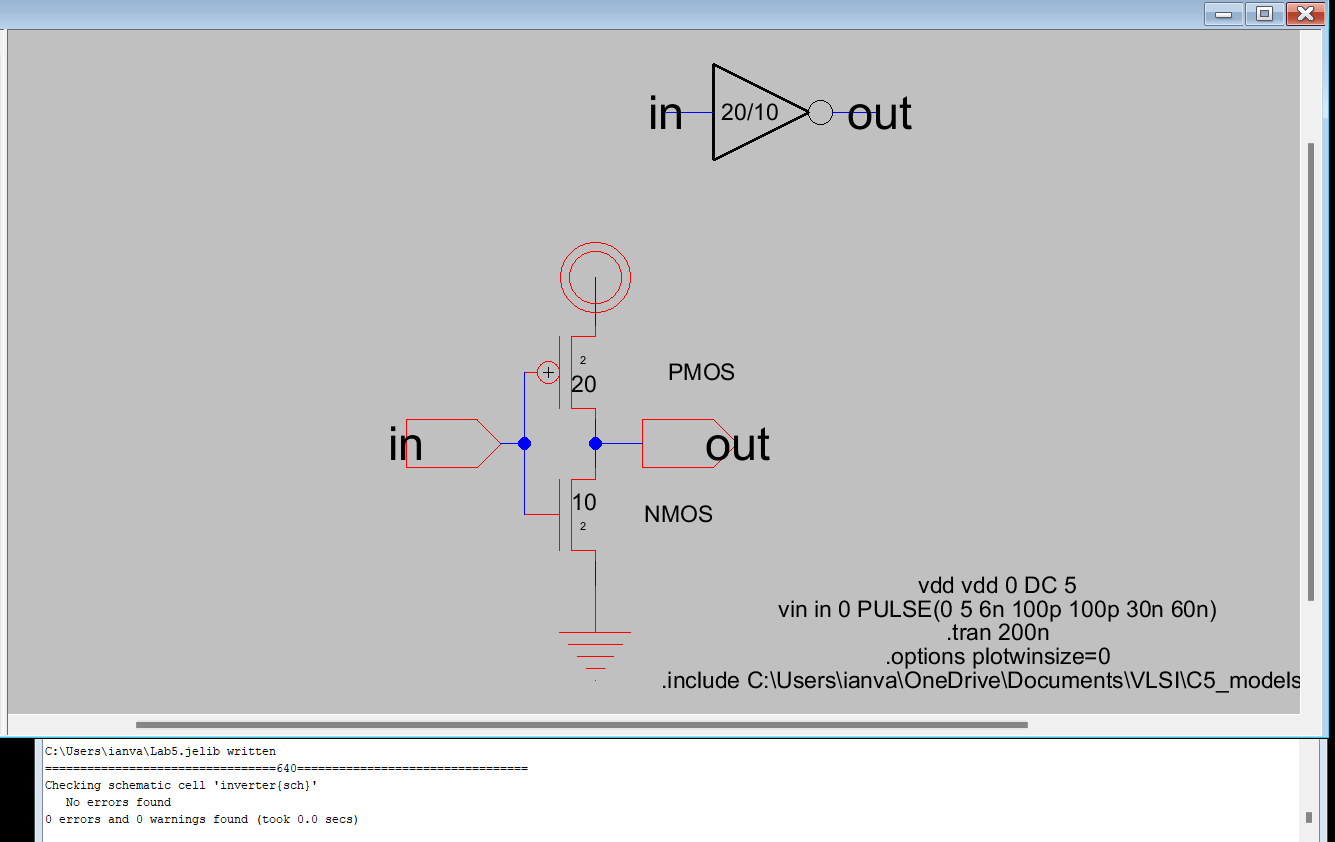

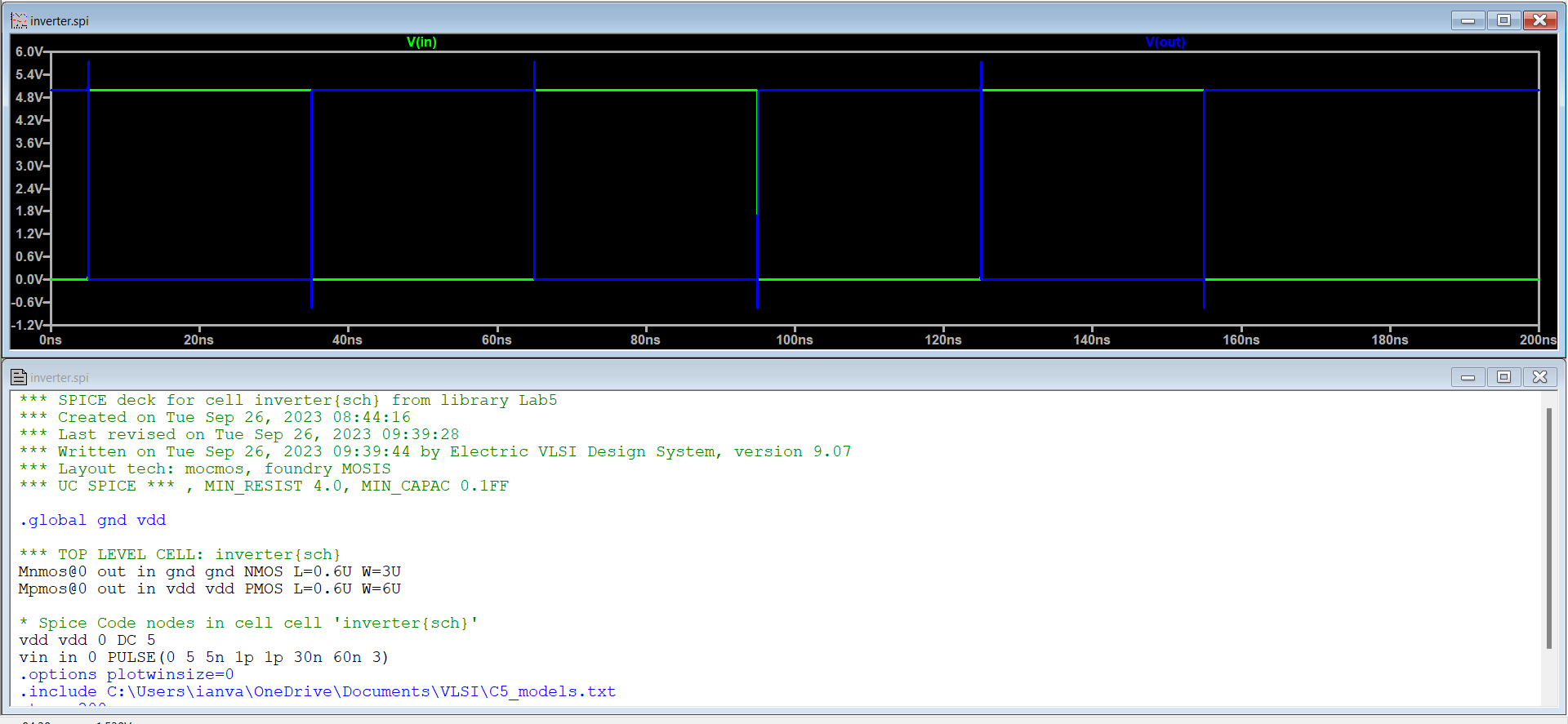

Figure 3: Inverter Schematic (error free) and Pulse Spice Code

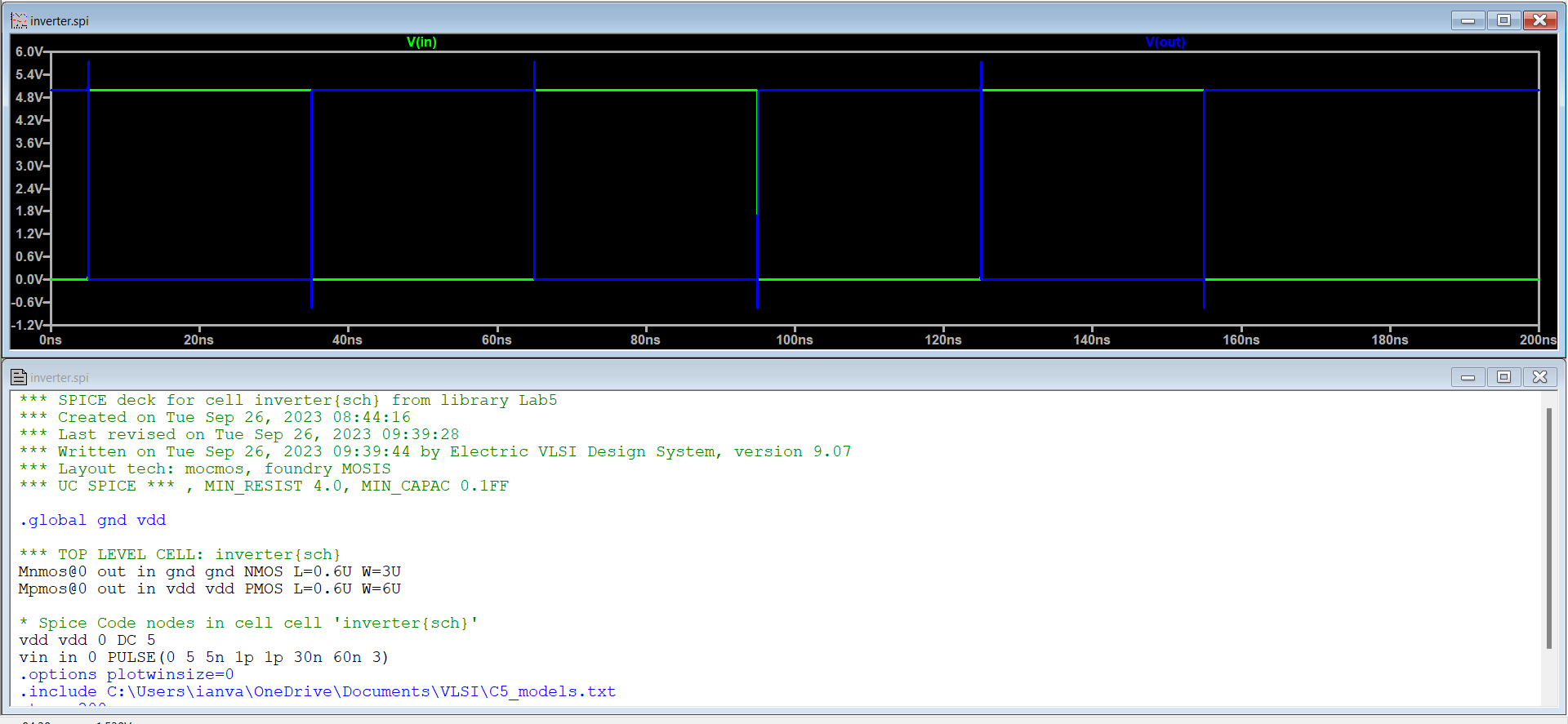

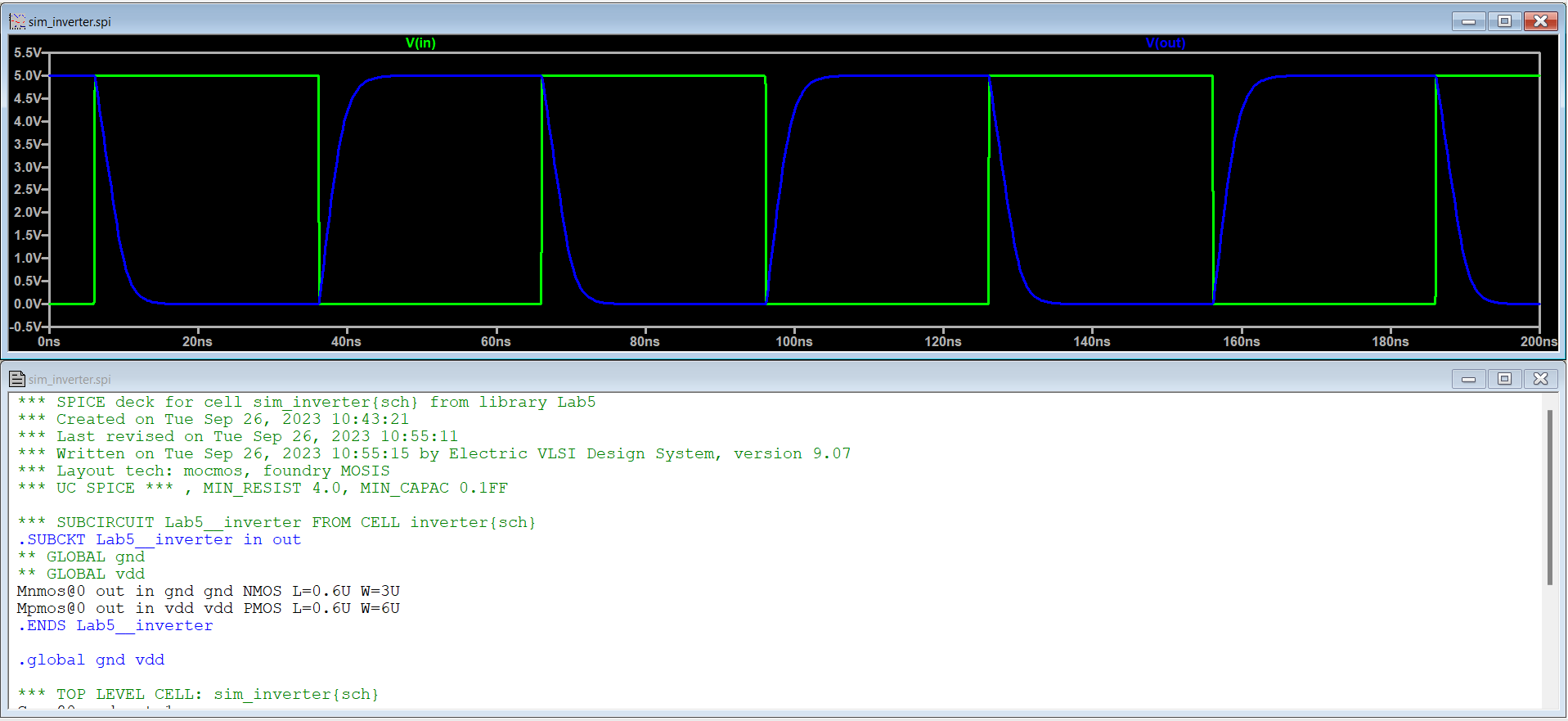

Figure 4: Pulse Spice Simulation

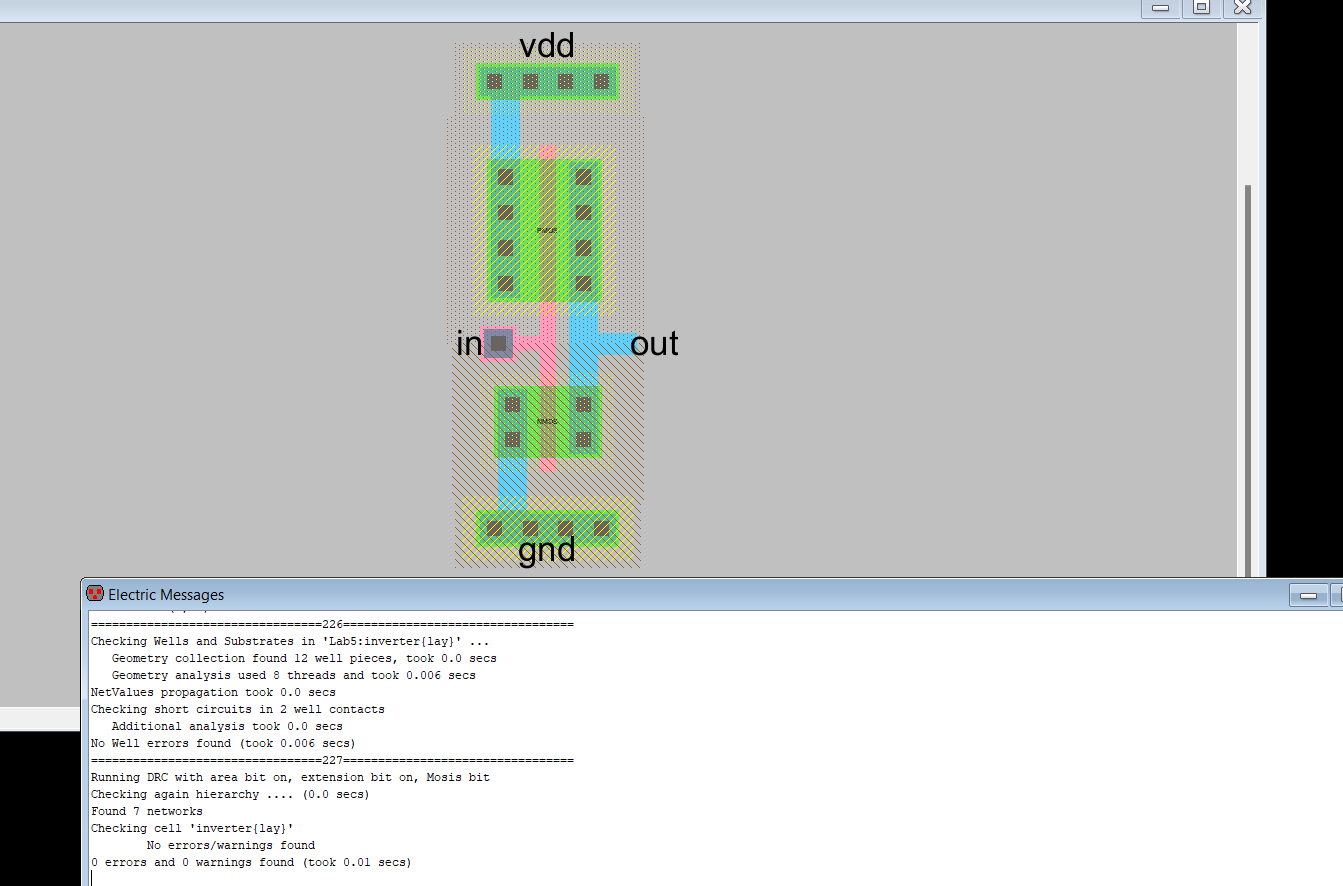

Task 2: Create the layout of the inverter (20 points).

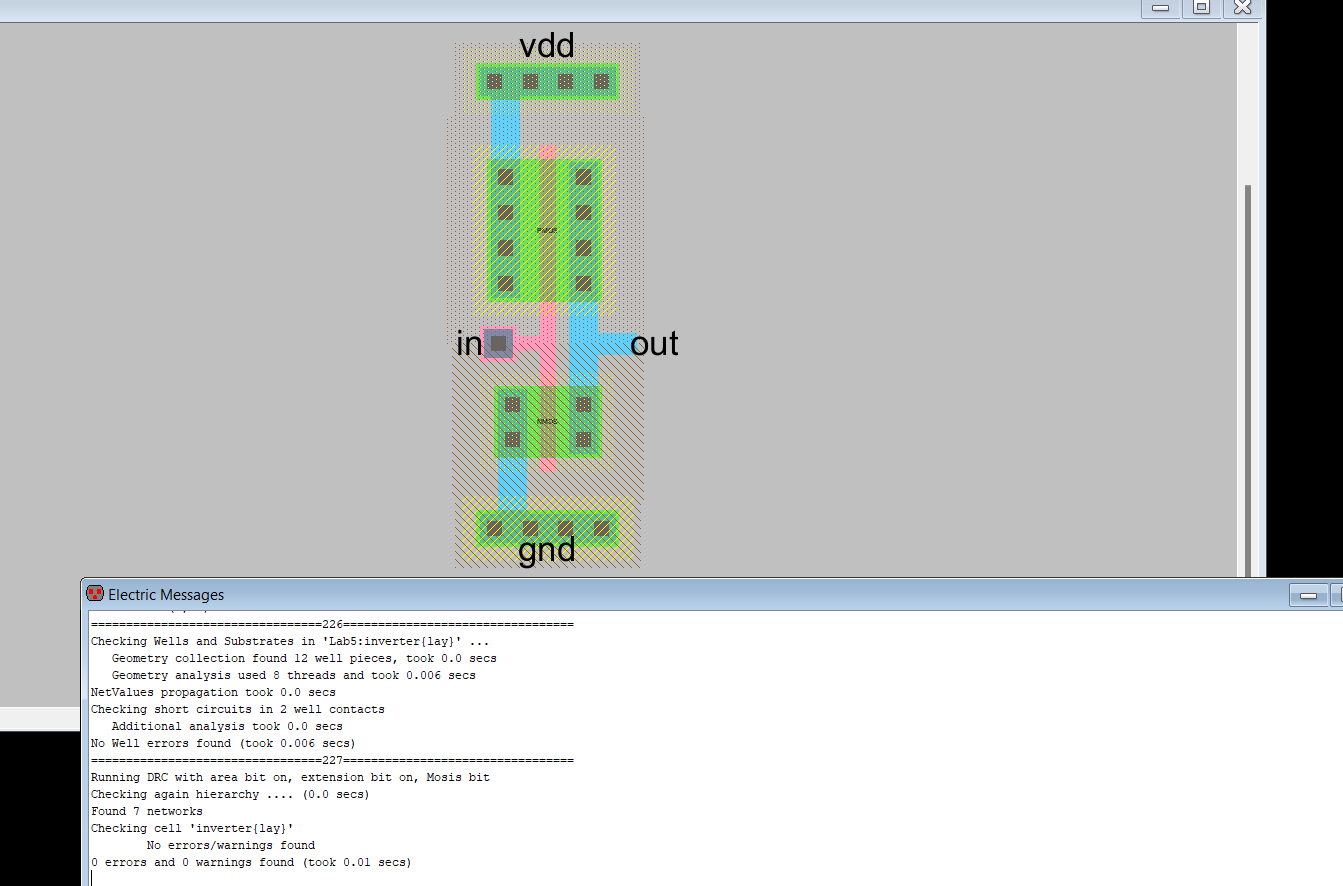

Figure 5: Layout of Inverter(error free)

Task 3: Use multiplier of build large inverter (20 points).

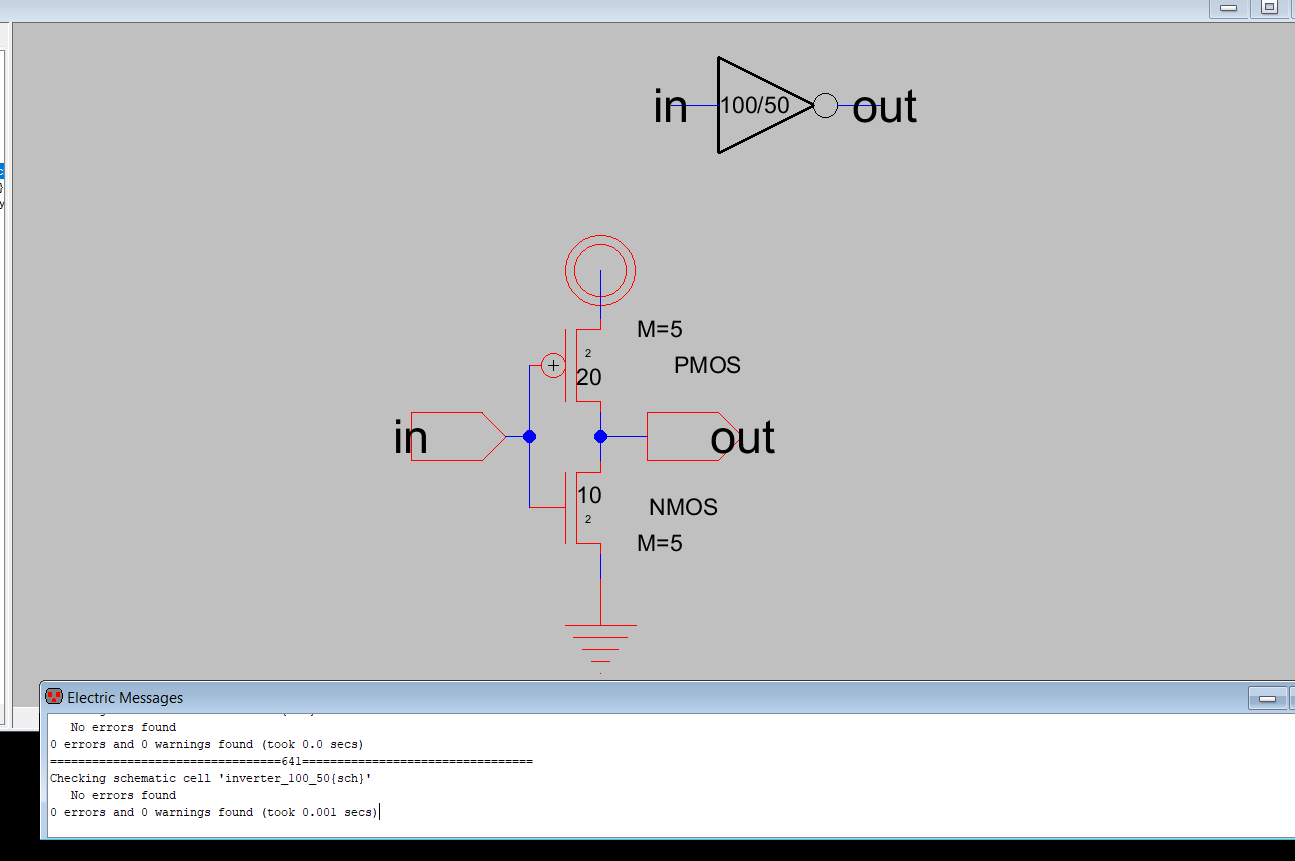

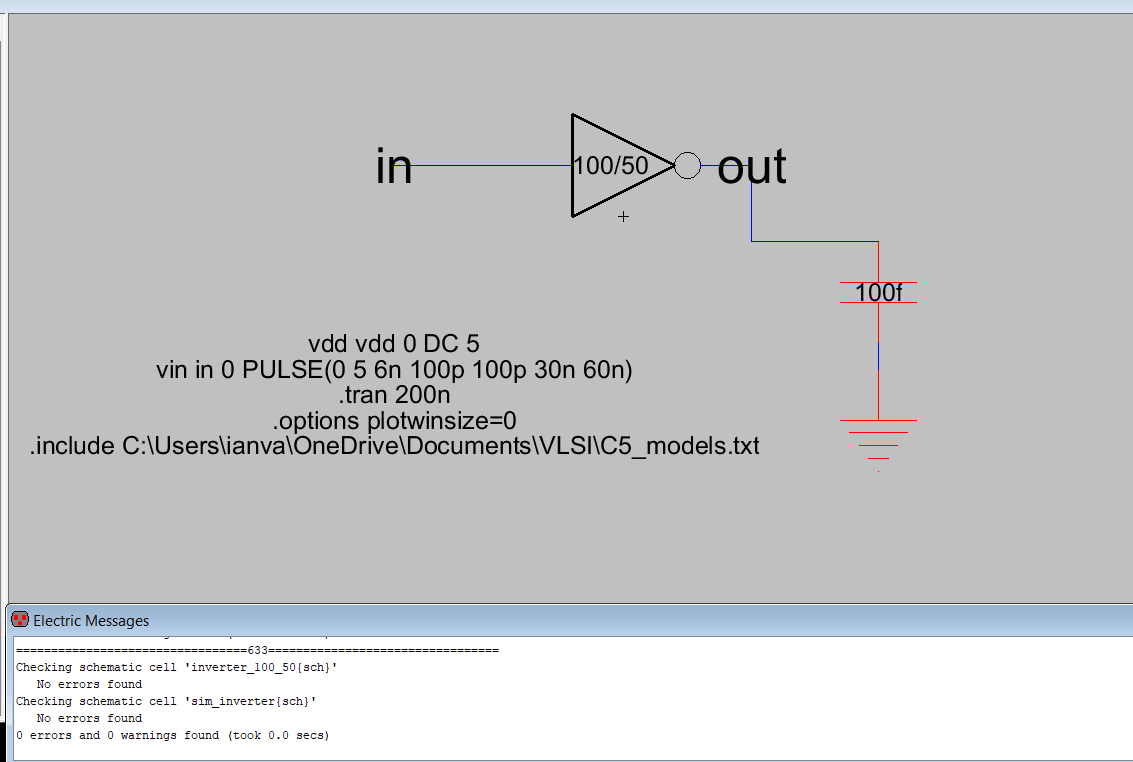

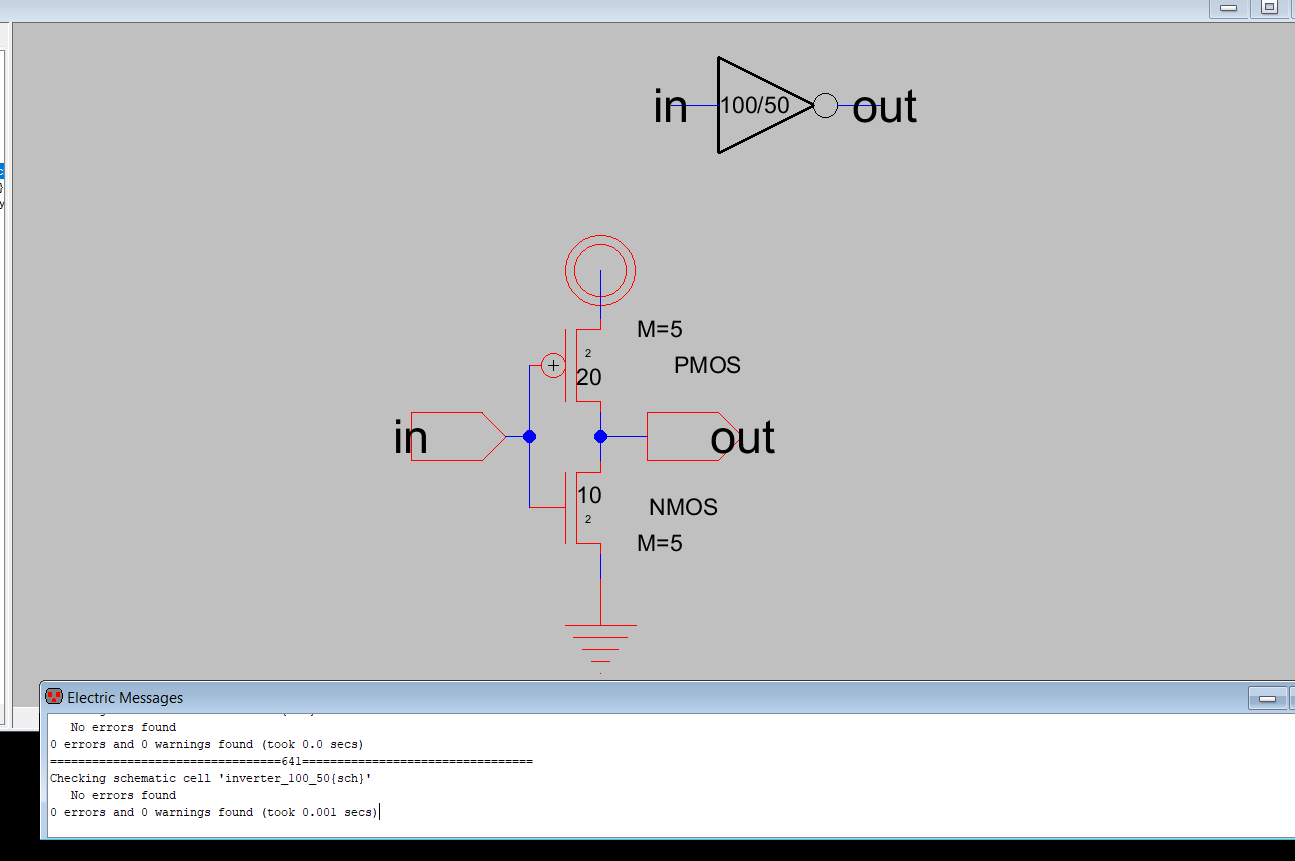

Figure 6: Schematic Using Multiplier to Create 100/50 inverter

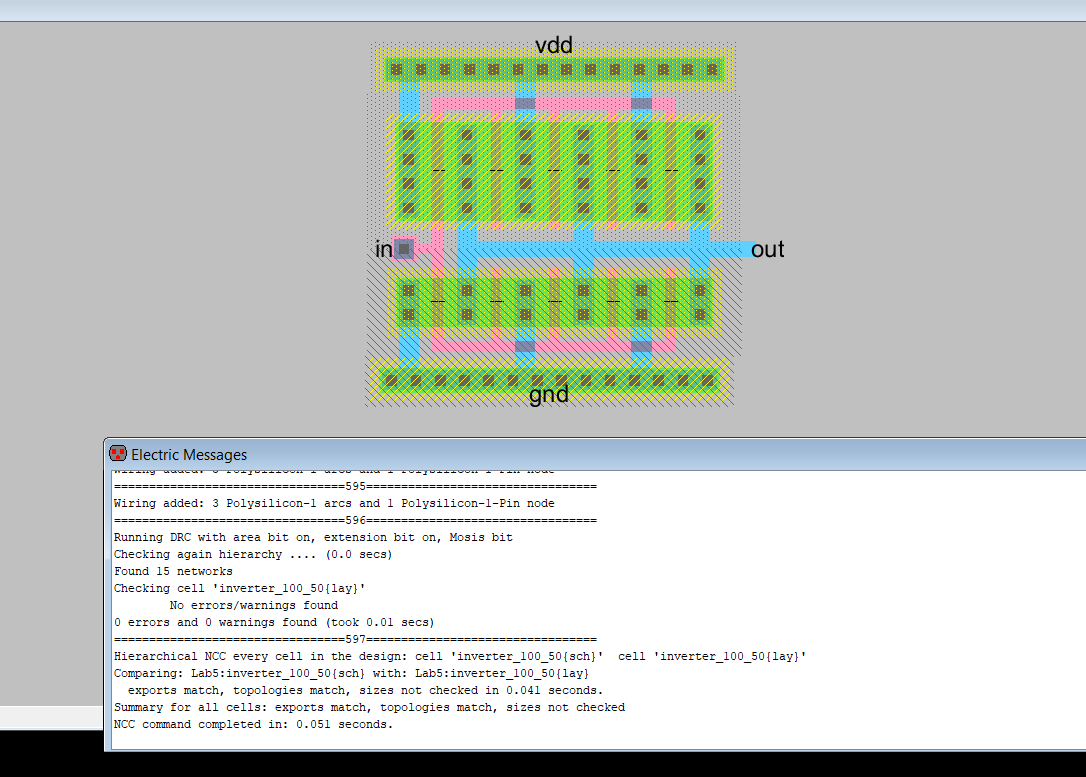

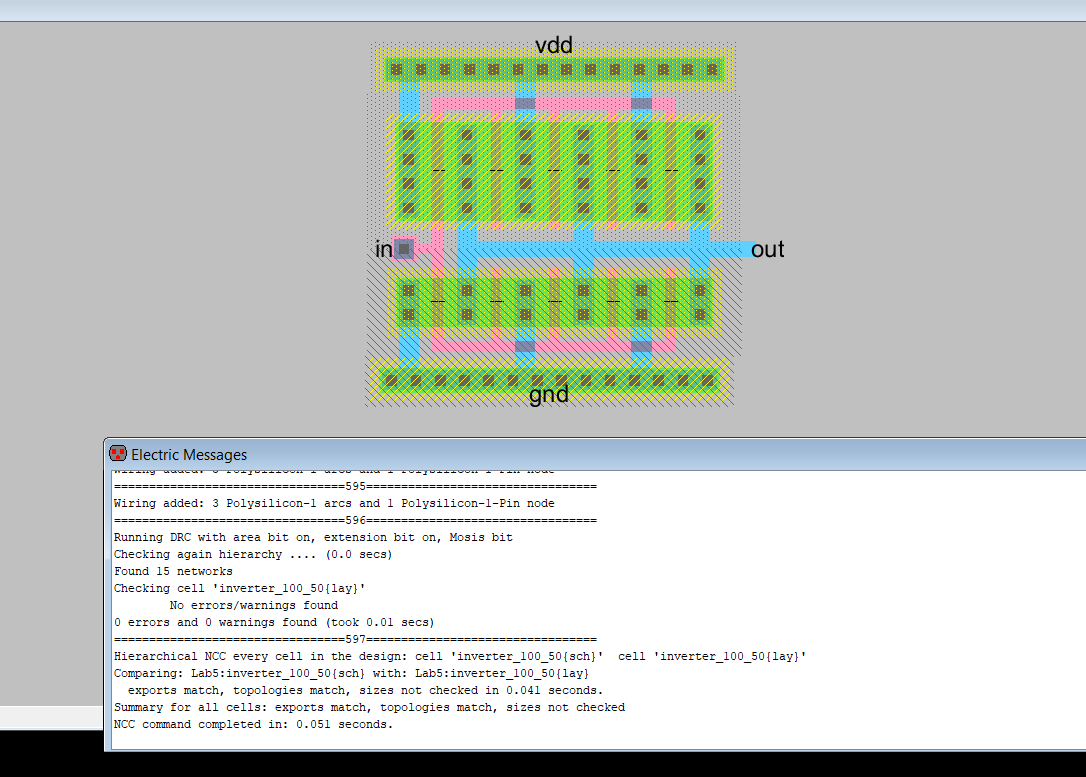

Figure 7:100/50 inverter layout (error free)

Task 3: Run simulations to verify the driving capability of these two different inverters (20 points).

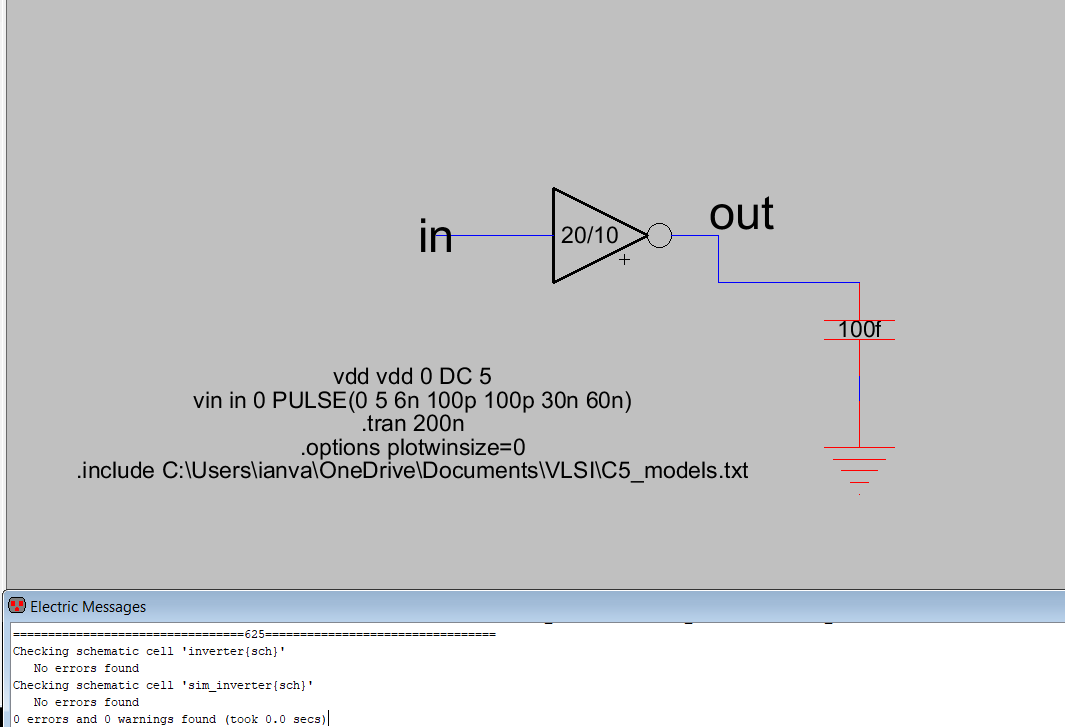

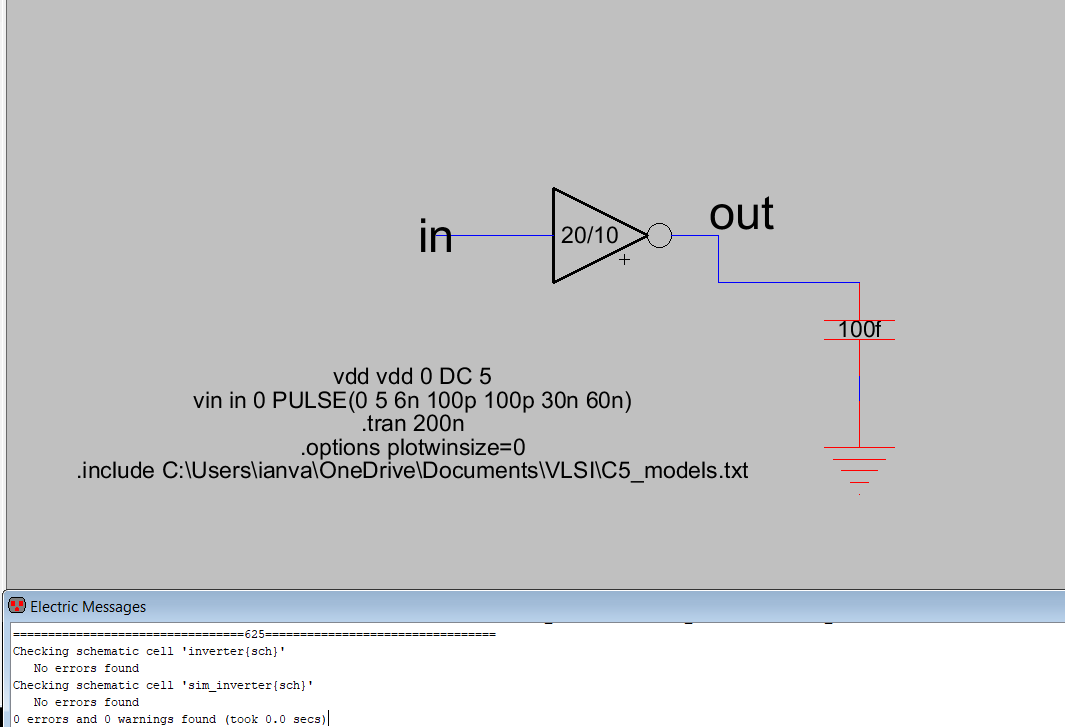

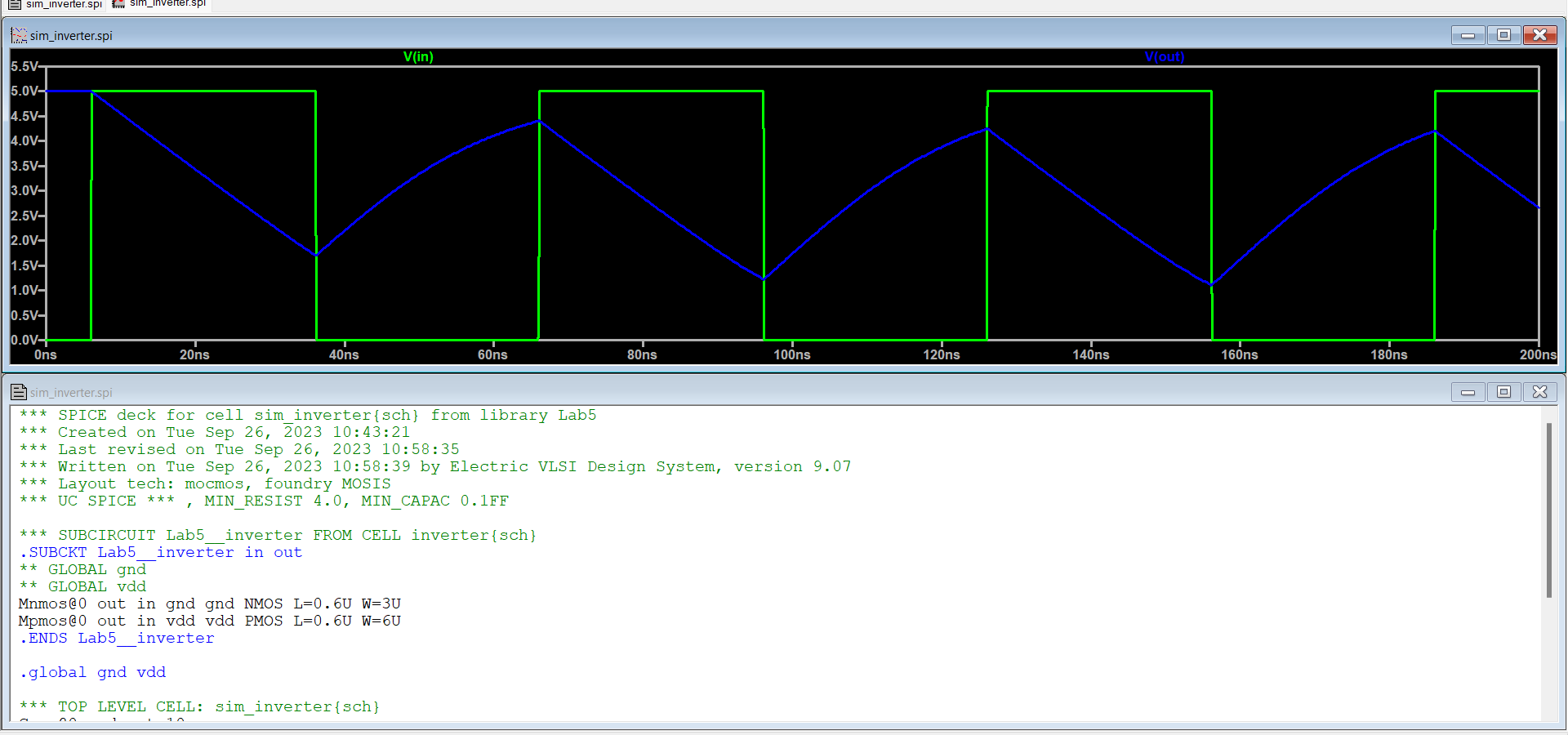

Figure 8: 20/10 Simulation Schematic and Spice code (Capacator value changes 100f,1p,10P)

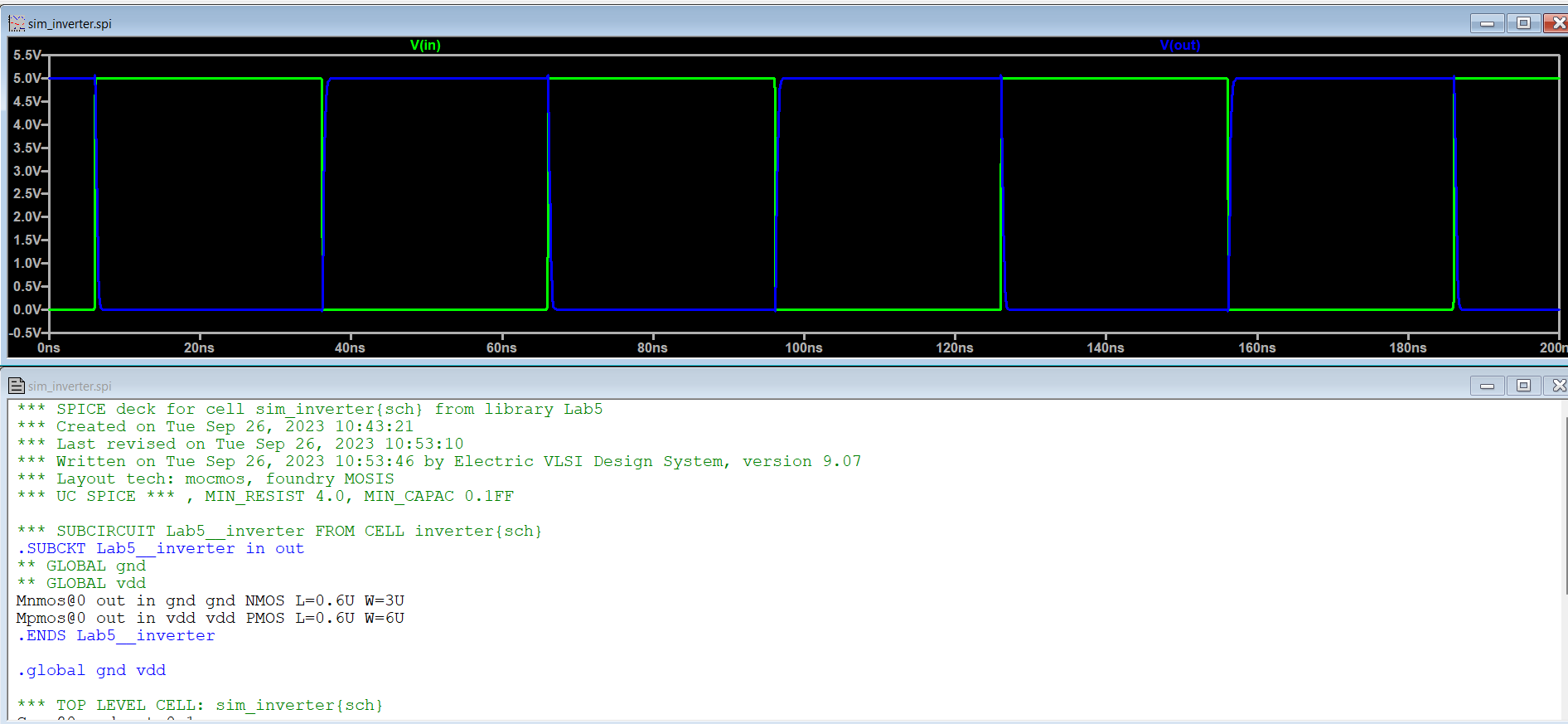

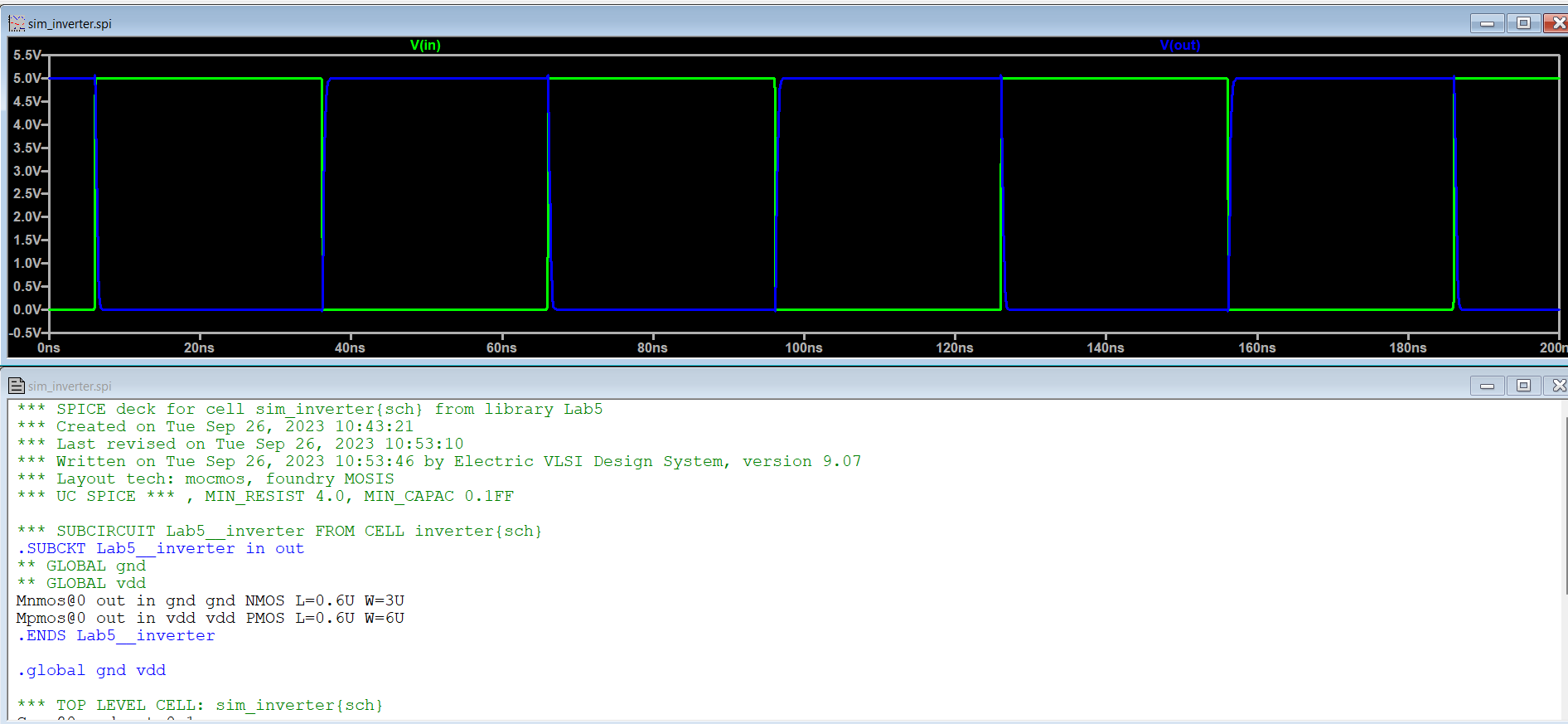

Figure 9:100f Spice Simulation for 20/10 Inverter

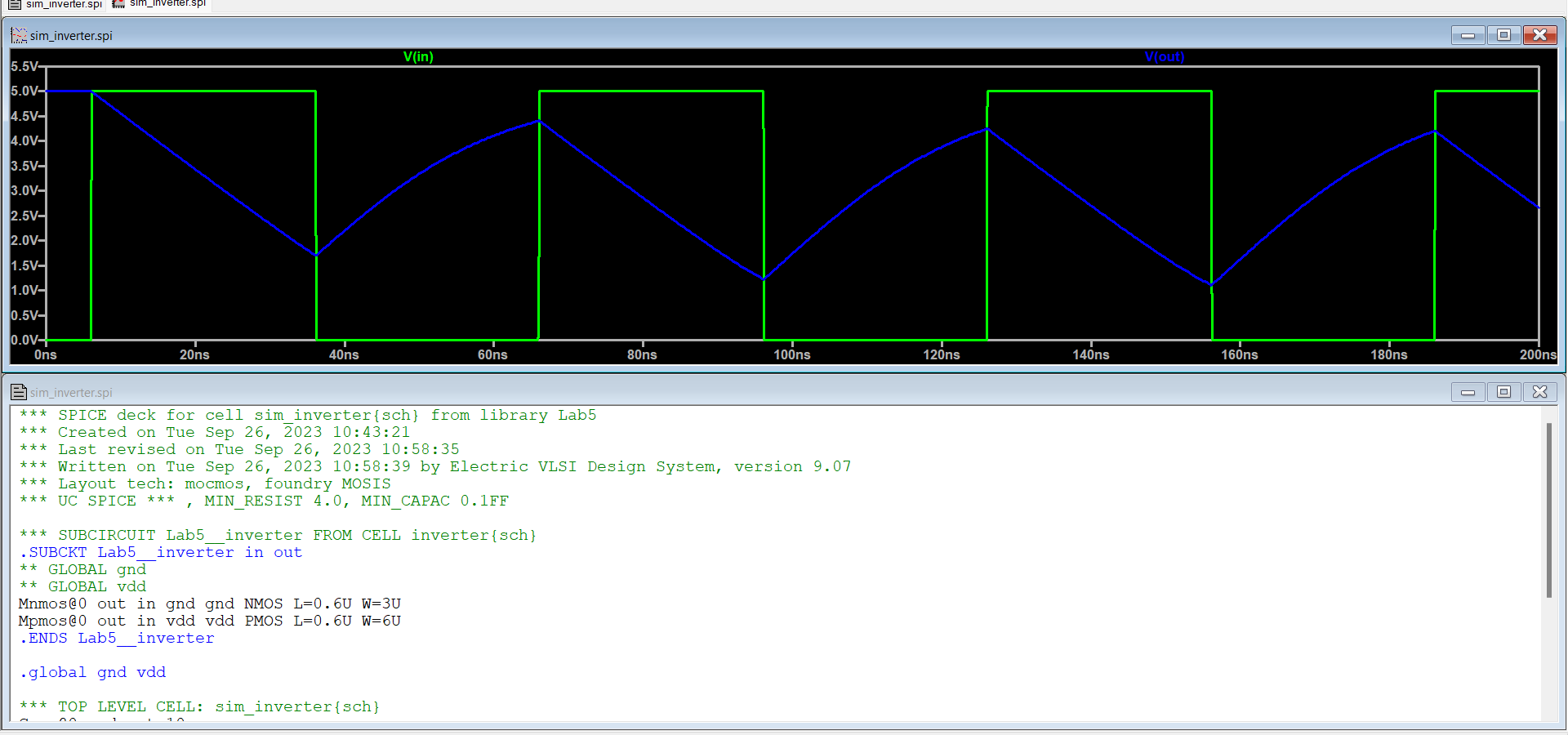

Figure 10: 1p Spice Simulation for 20/10 Inverter

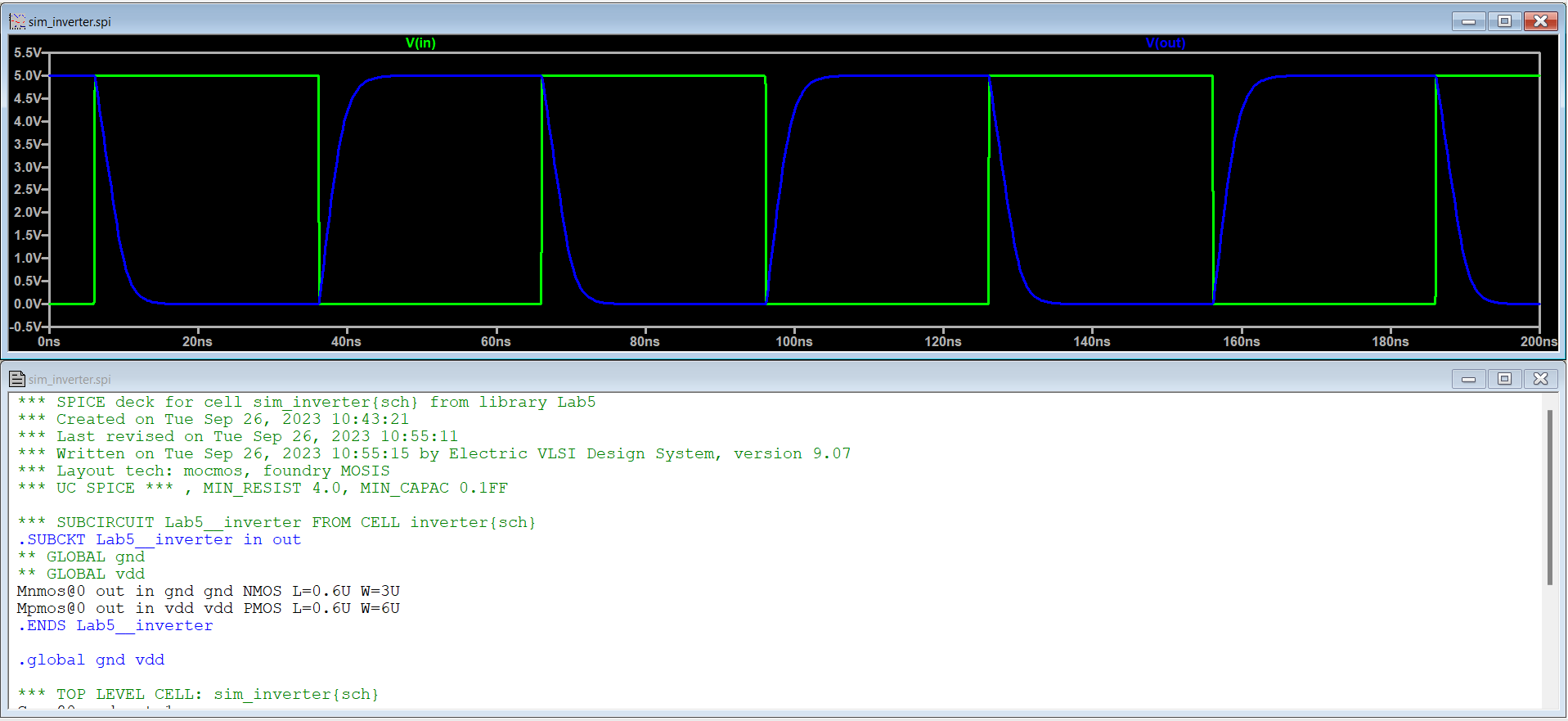

Figure 11: 10p Spice Simulation for 20/10 Inverter

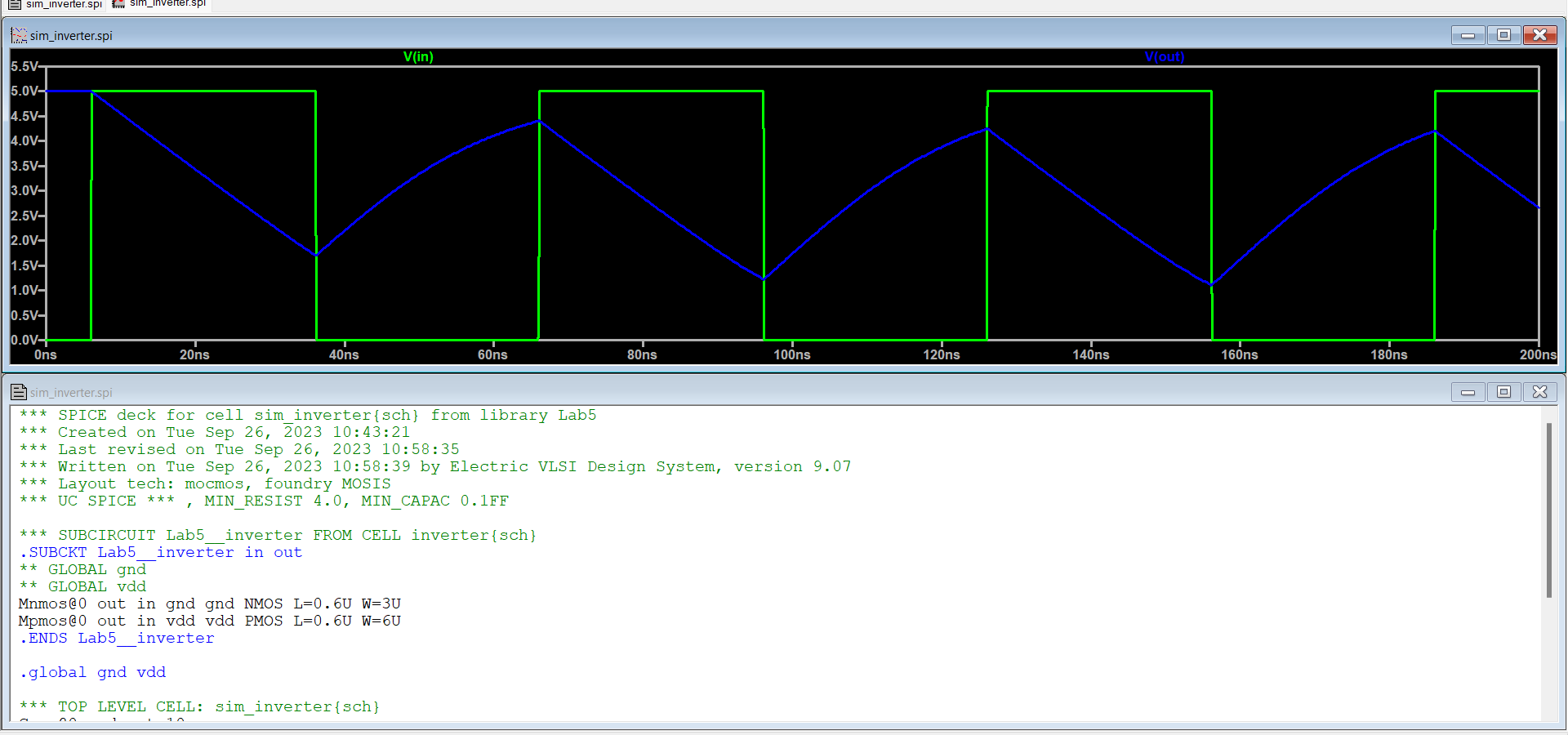

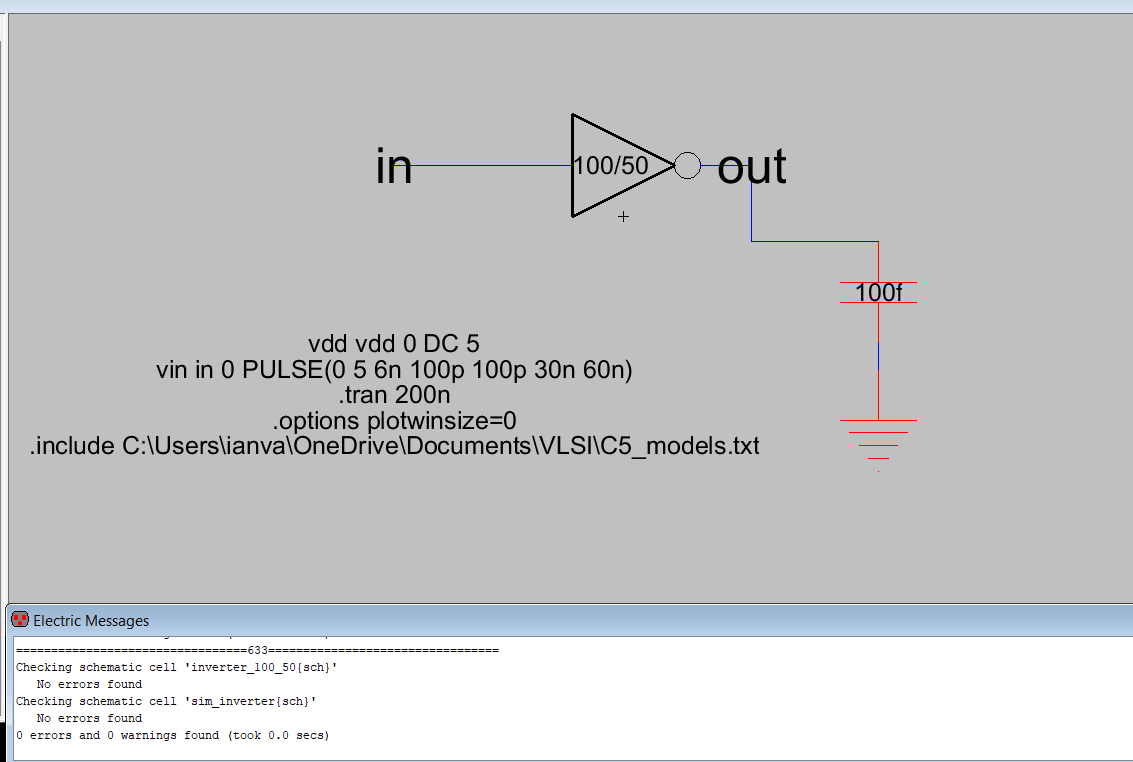

Figure 12: Schemaic for 100/50 Inverter simulation and spice code( Cacpacator varies 100f,1p,10p)

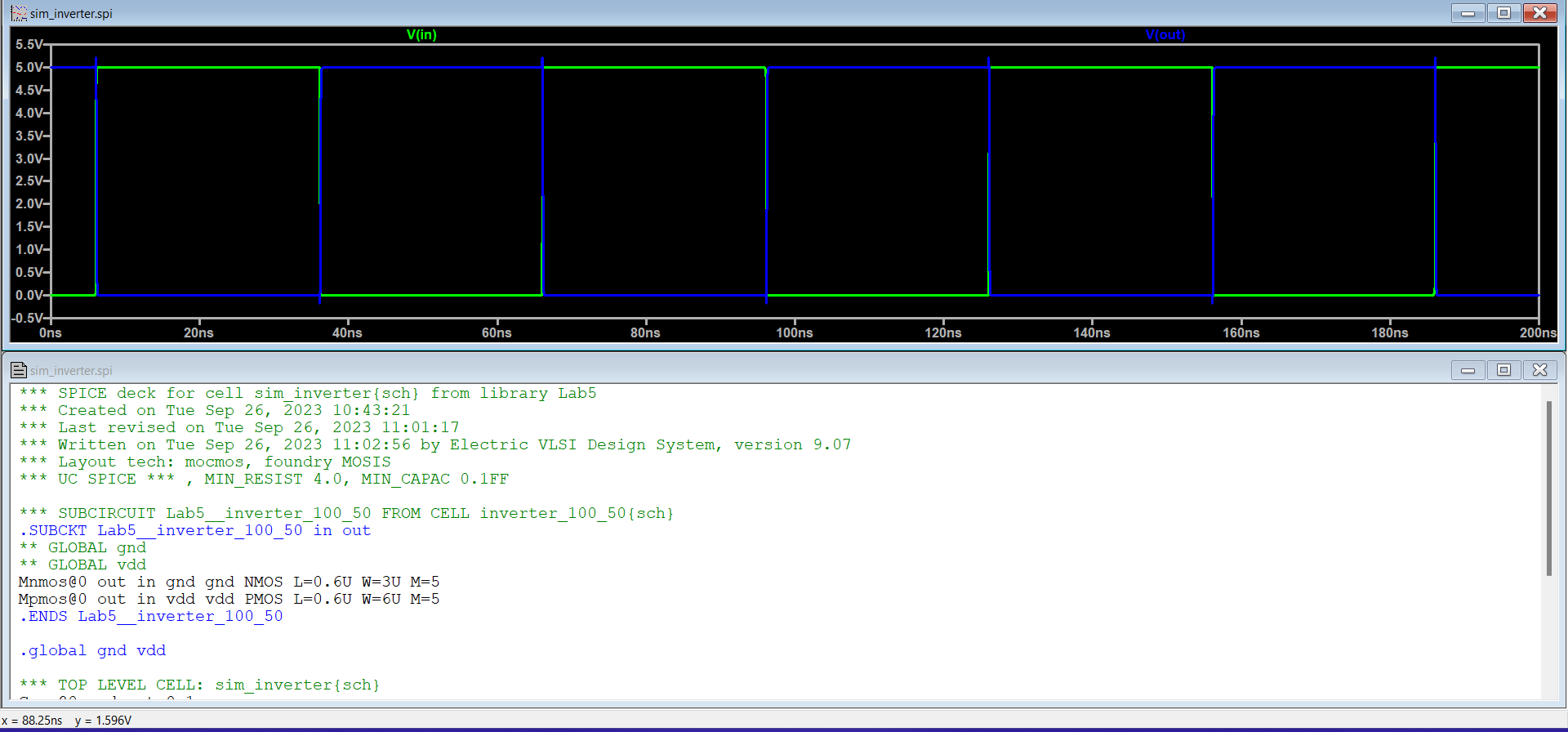

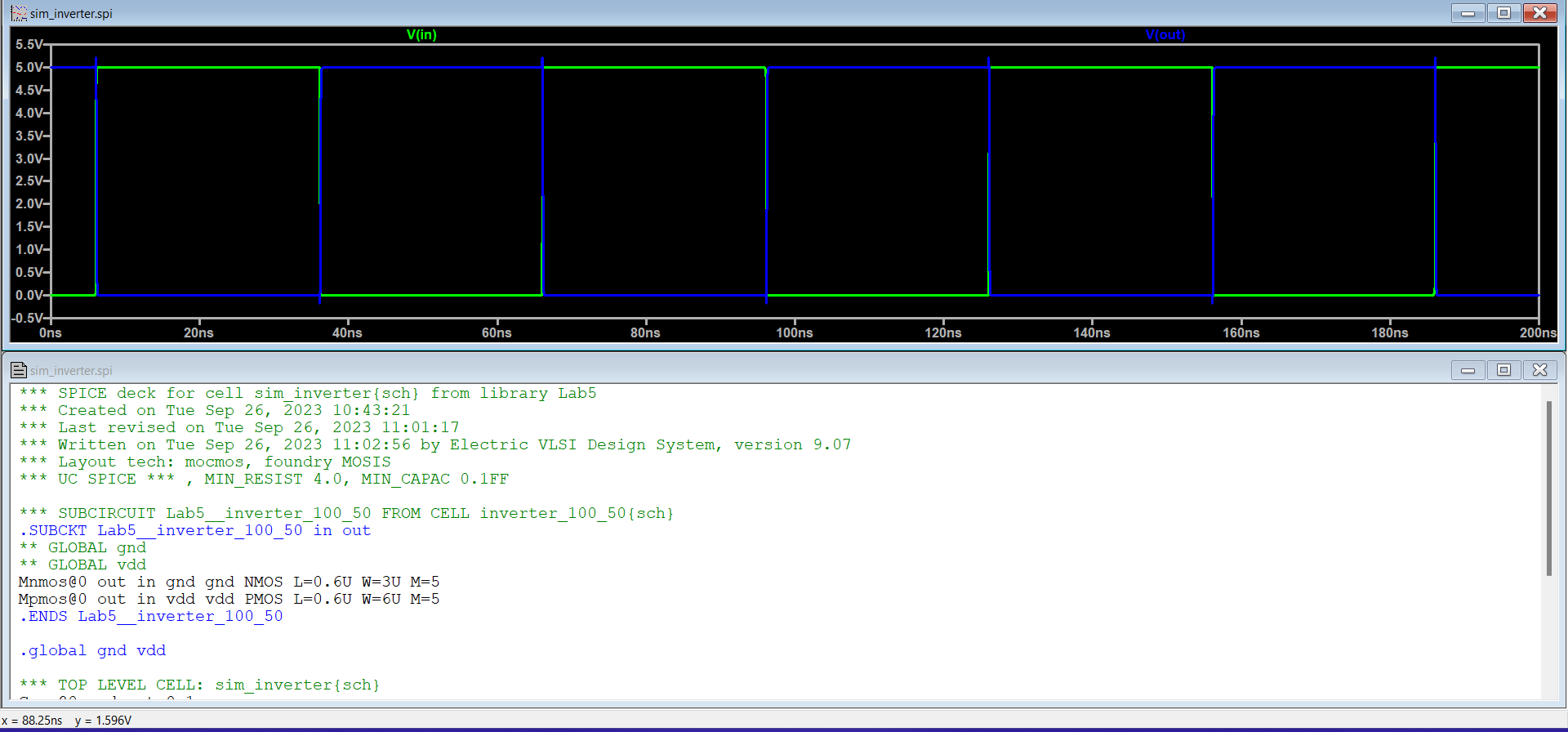

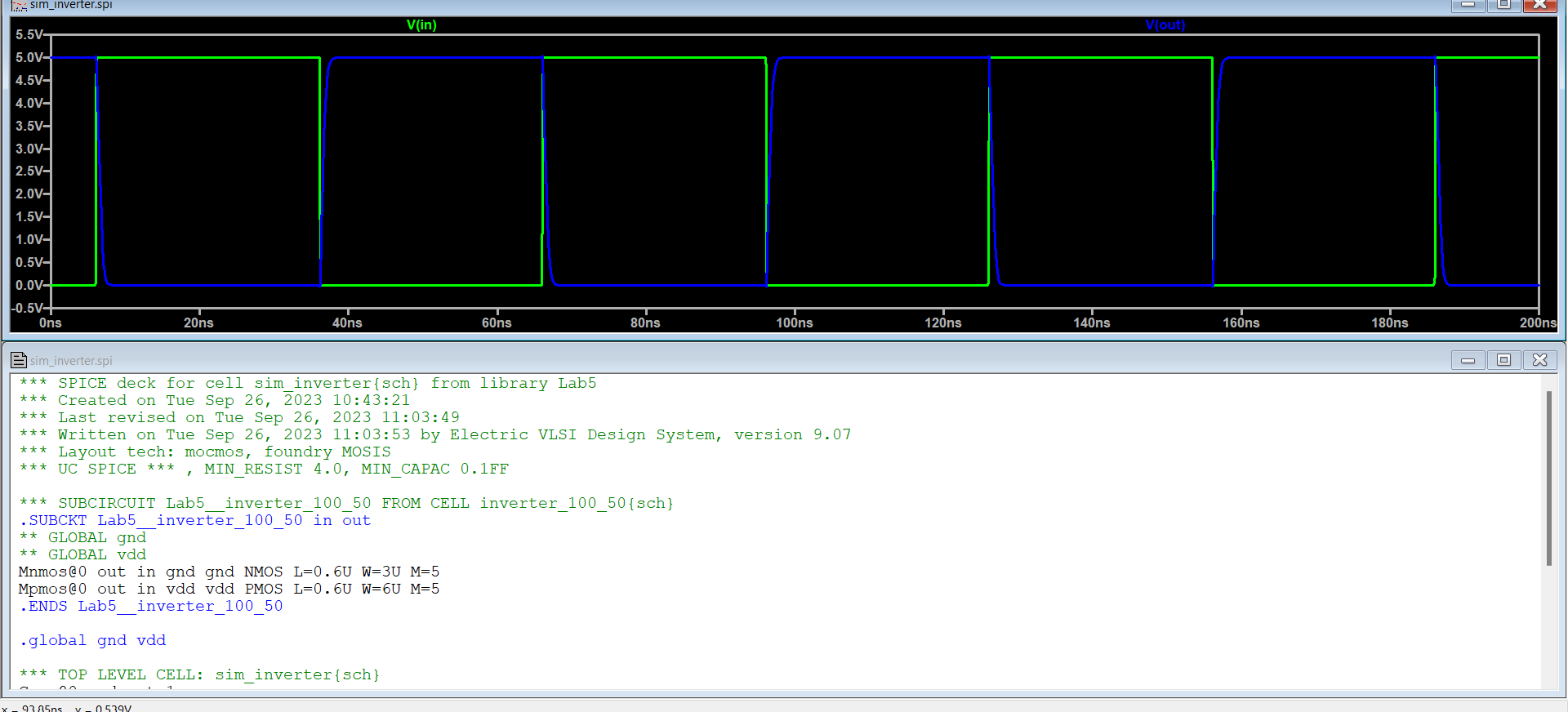

Figure 13: 100f Spice Simulation for 100/50 Inverter

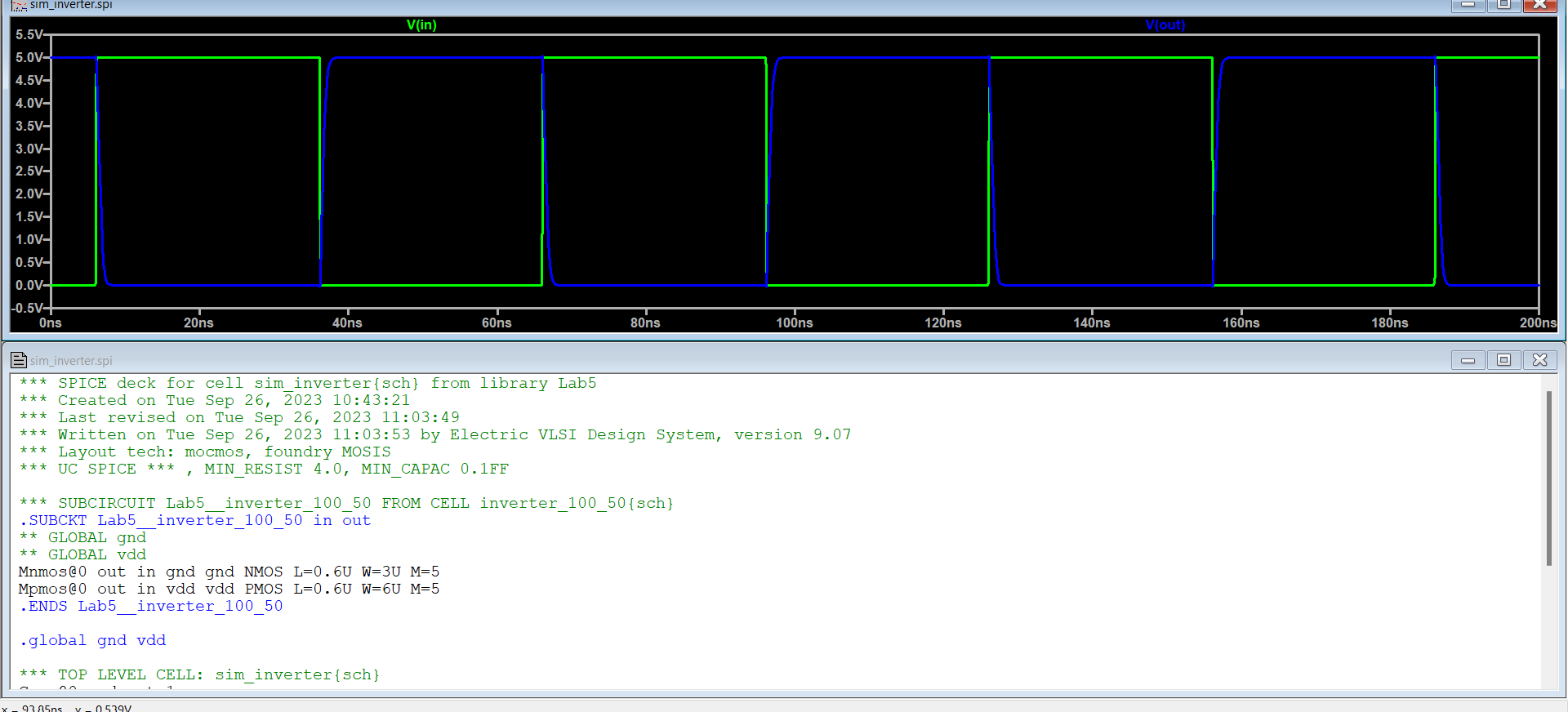

Figure 14: 1p Spice Simulation for 100/50 Inverter

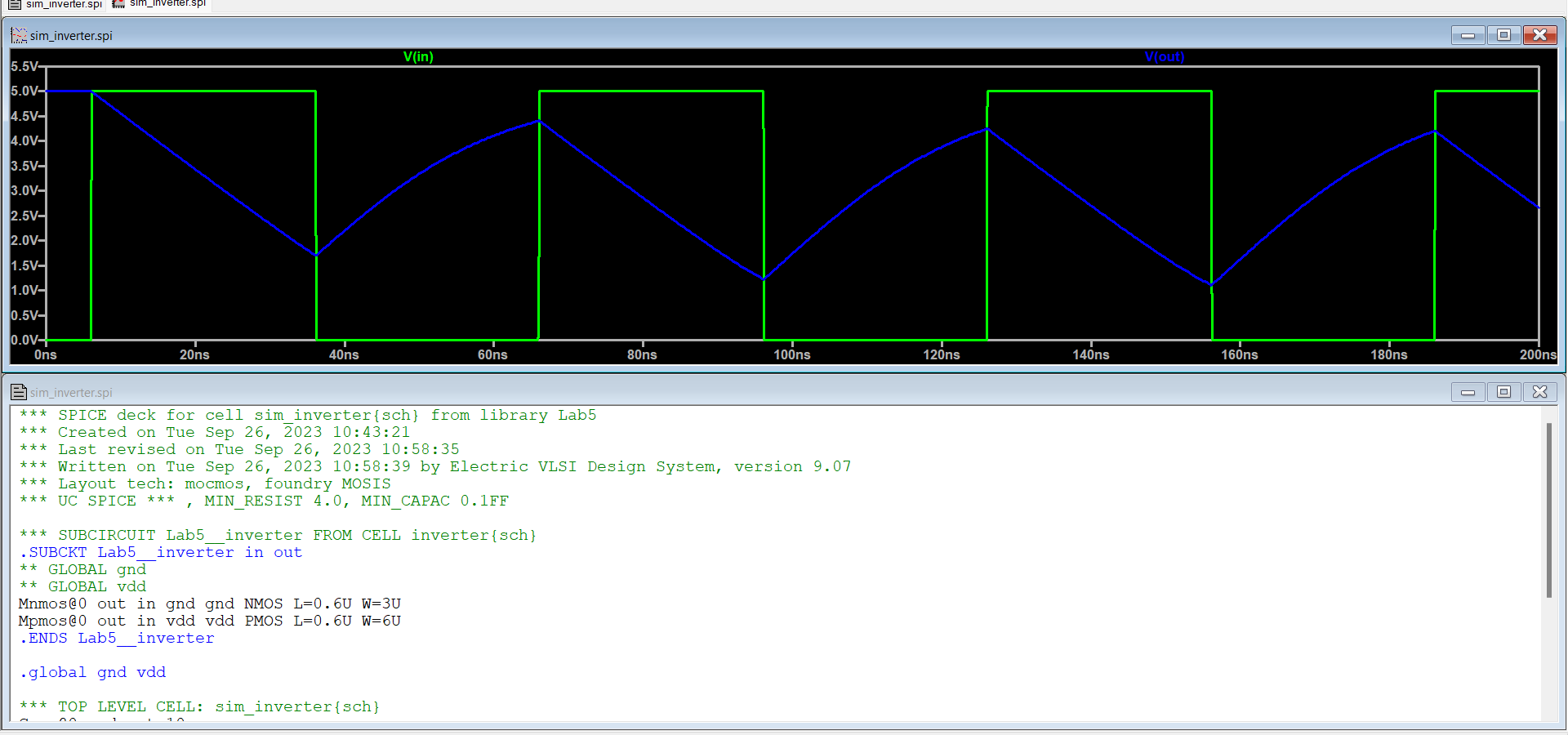

Figure 15: 10p Spice Simulation for 100/50 Inverter

Conclusion:

This lab sucessfully taught how to layout an inverter in eletric

VLSI. The 100/50 inverter proved capable of charging a larger capacator

in the same time as the 20/10 inverter. This is because is uses 5 PMOS

and 5NMOS

transistors in paralell rather than just 1.