ENGR 338 - Lab 2 2023 Fall

Name: Ian Van Horn

Email: imvanhorn1@gmail.com

Layout of R_2R DAC

This lab taught how to create layouts and subcells in eletric VLSI

This lab requires the eletric VLSI software

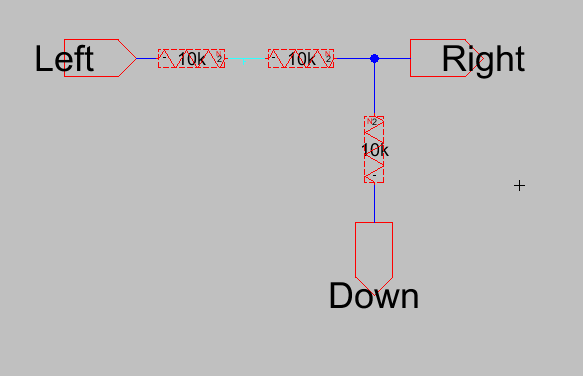

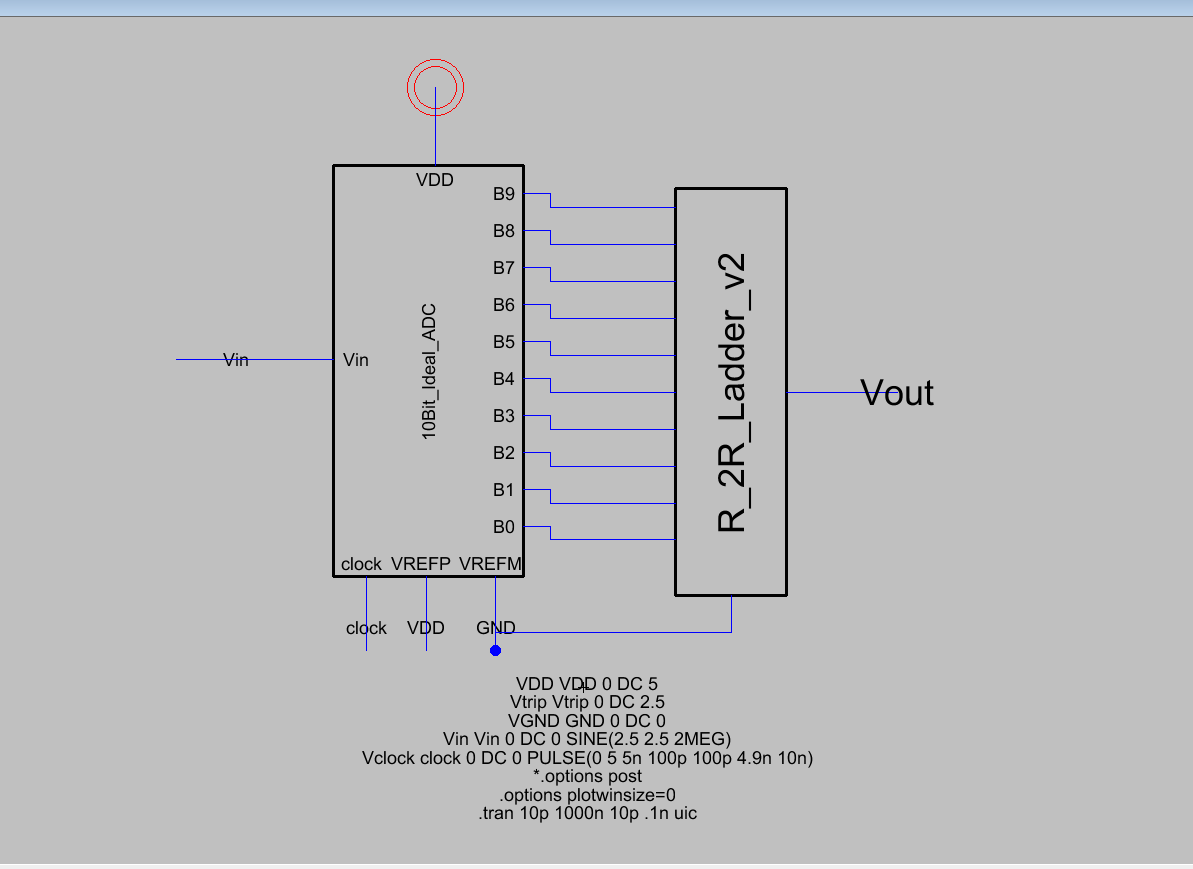

Task 1: Create the schematic of the subcells for the R-2R ladder. (40 points).

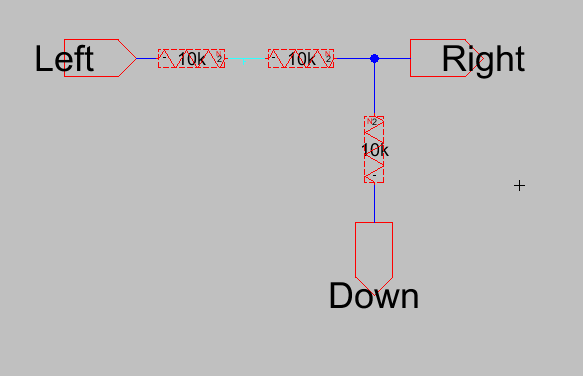

Figure 1:Schematic of Subcell for R_2R

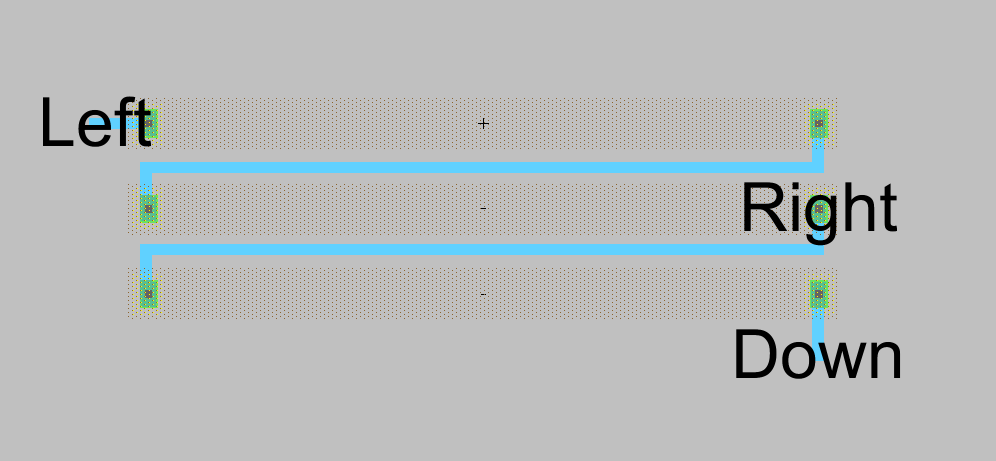

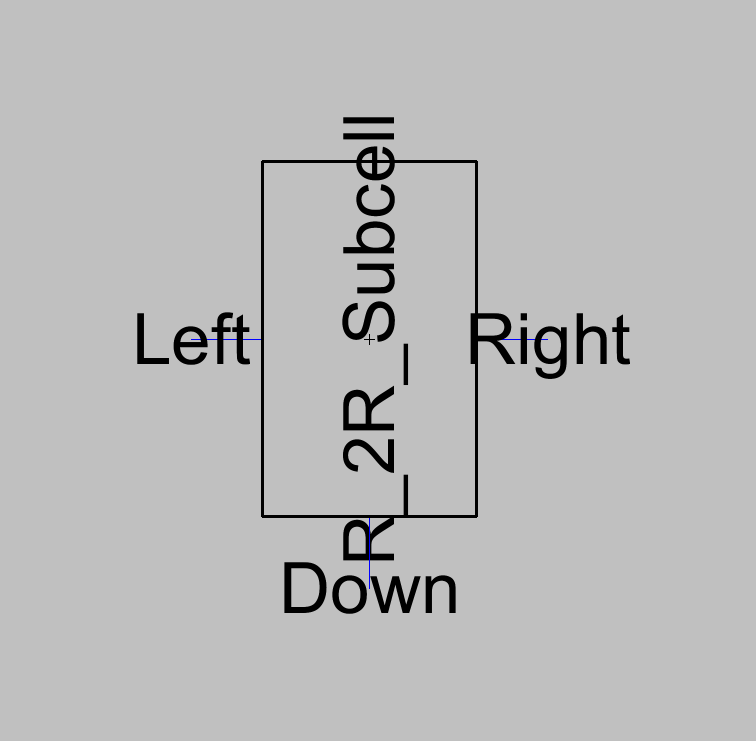

Figure 2. Icon for Subcell of R_2R

Figure 3: Schematc of R_2R Ladder using Subcells

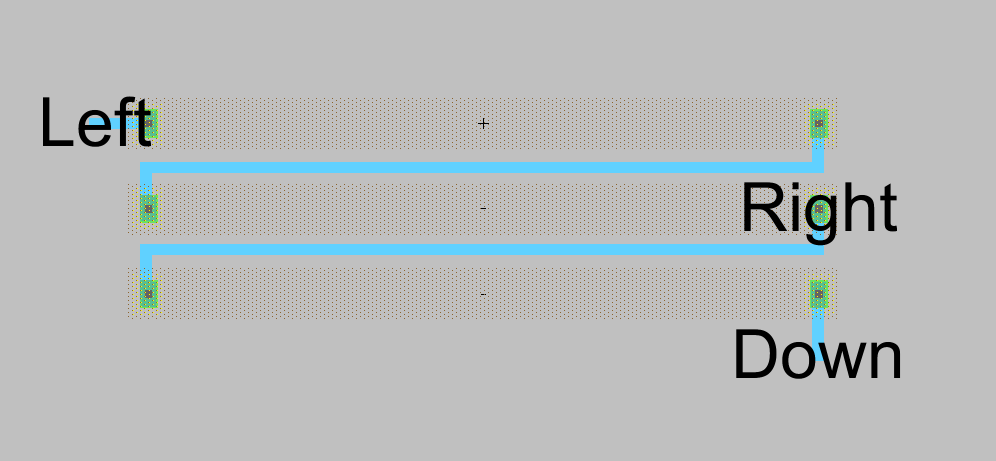

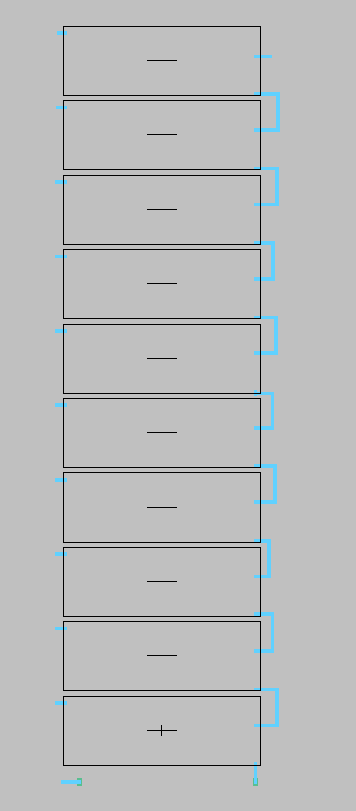

Task 2: Create the layout of the subcells for the R-2R ladder. (50 points).

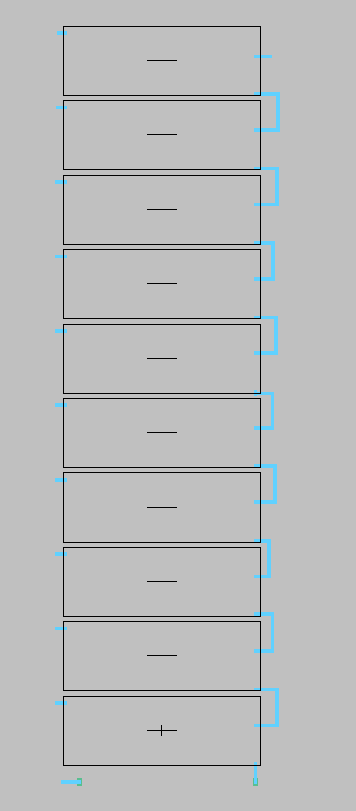

Figure 4: Layout of R-2R DAC Subcell

Figure 5: Layout of R-2R Ladder

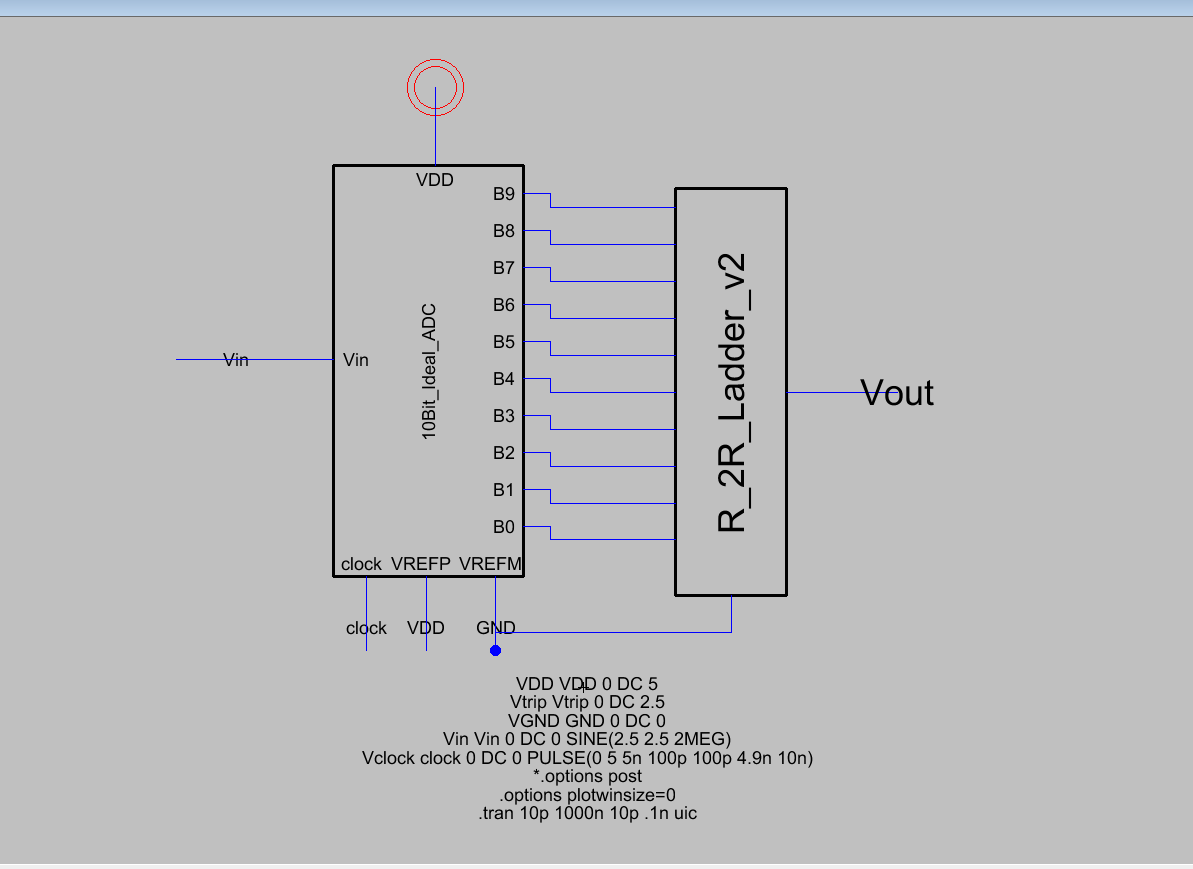

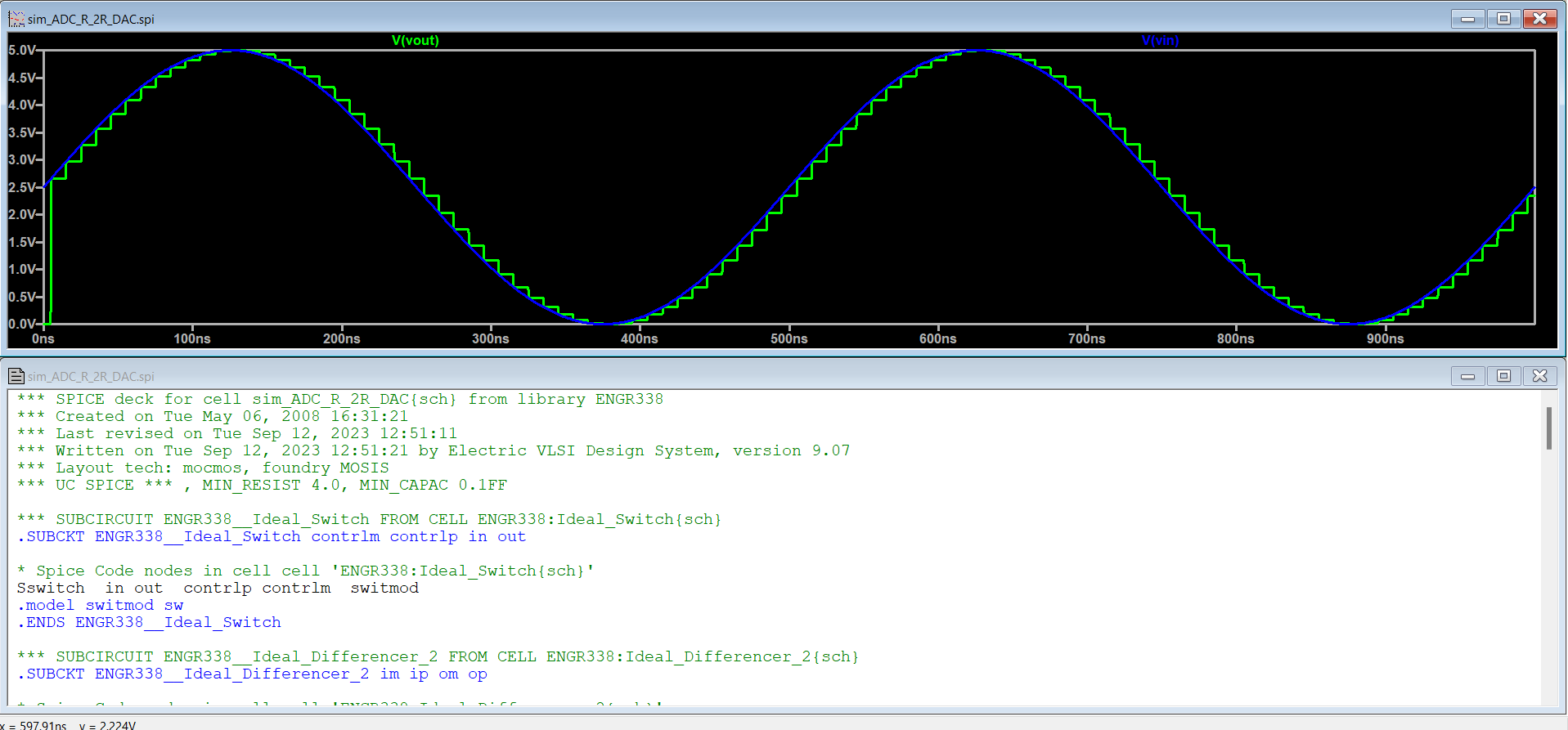

Figure 6: Icon of R_2R Layout Set up for simulation in LT Spice

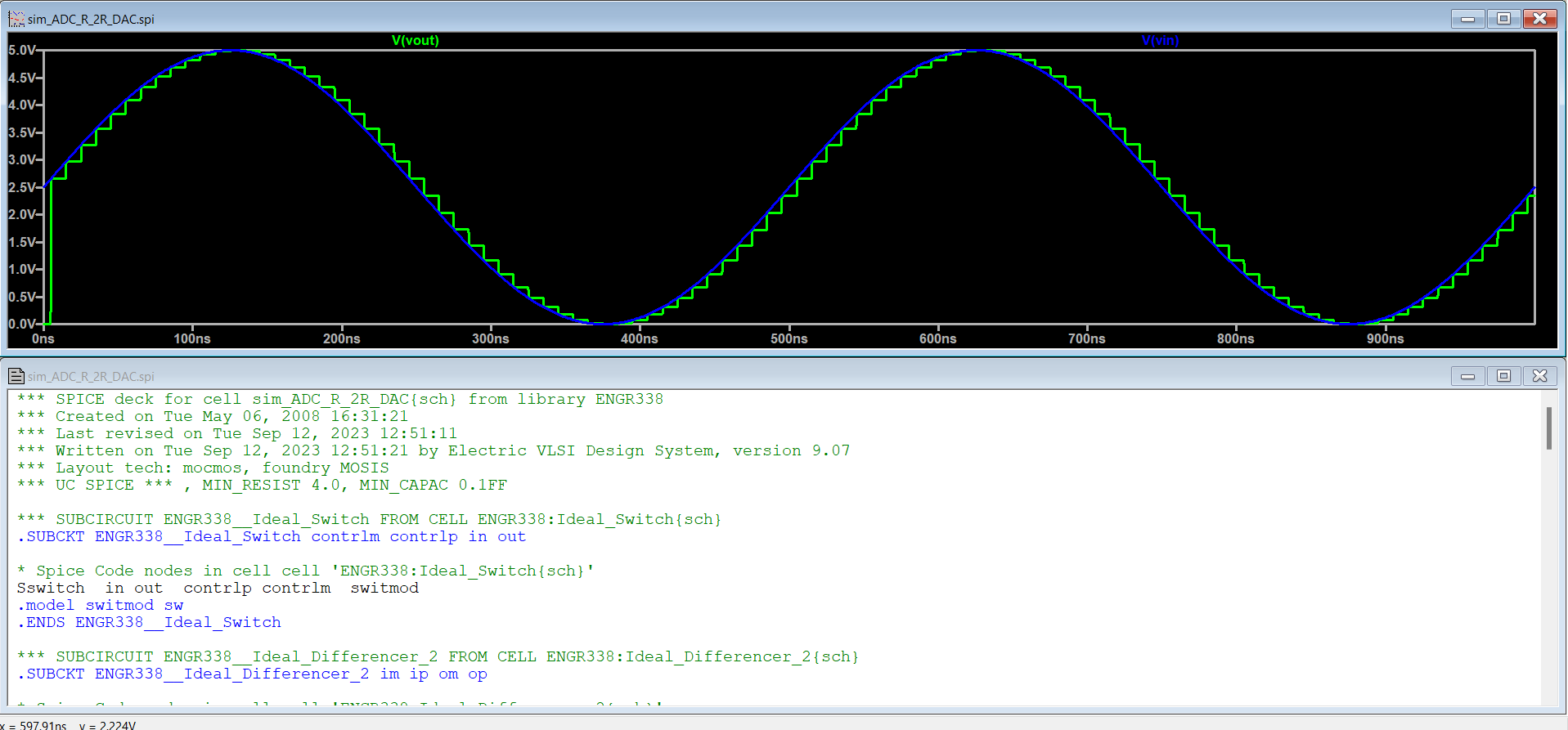

Figure 7: Results of Spice Simulation

Conclusion: The use of subcells allows for more neat and efficent

design. The layout sucsefully simuelated the DAC with the same results

as the schematic