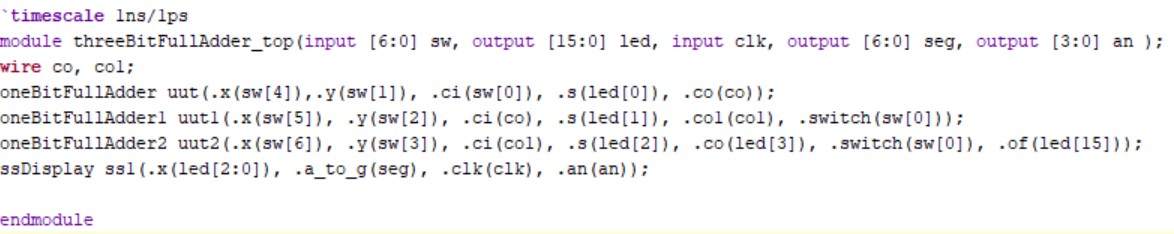

Figure 1. Top module for the 3-bit full adder, being the 2's compliment top.

(a)

(b)

(c)

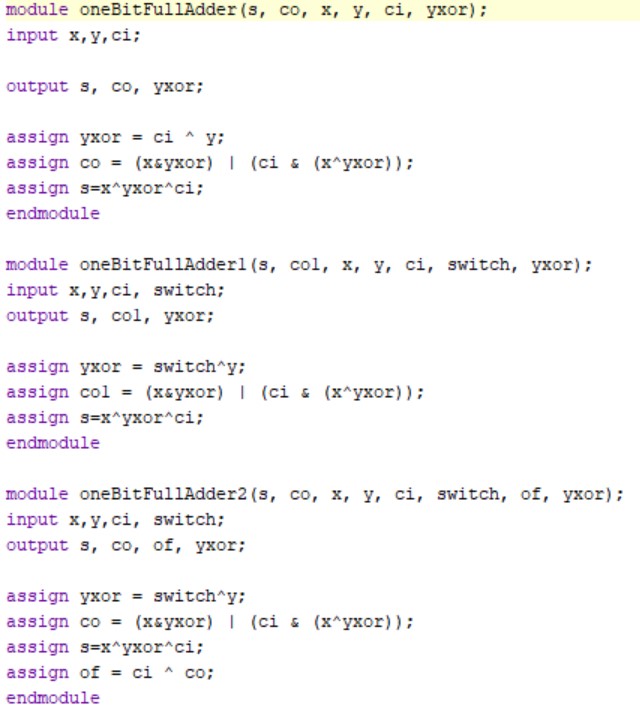

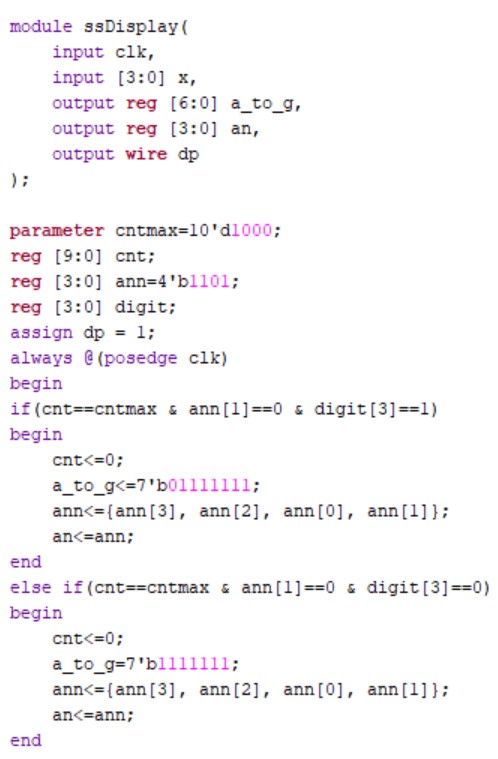

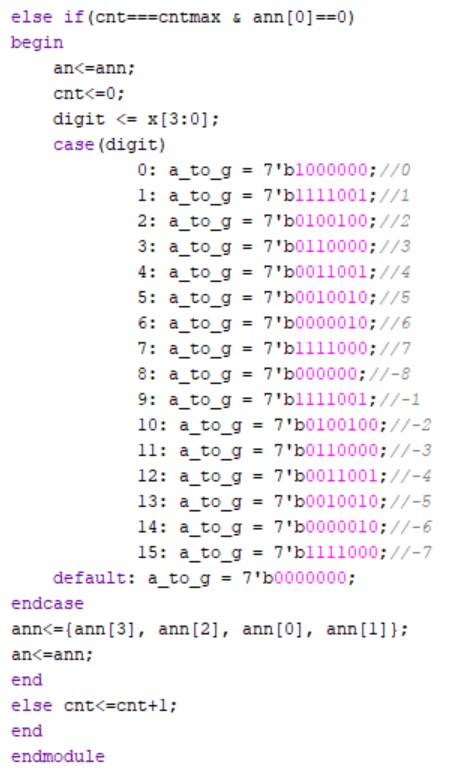

Figure 2. The 3-bit full adder module (a) and the seven segment display module (b).