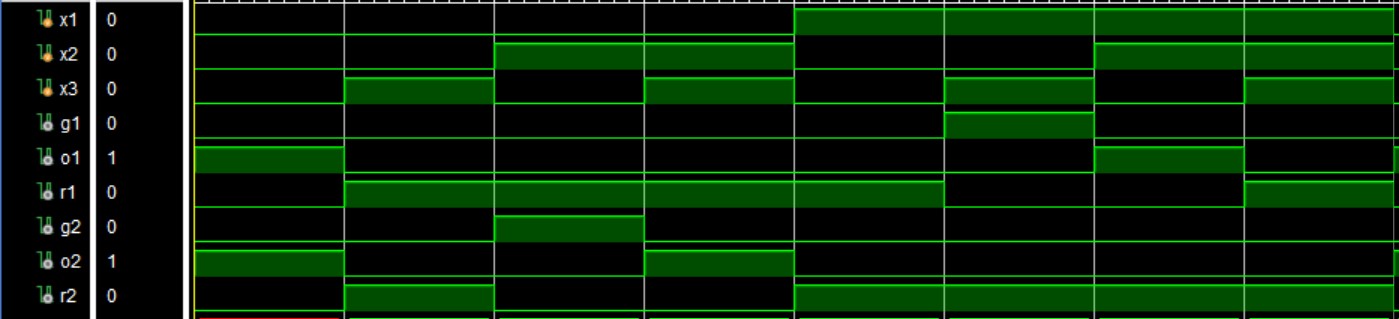

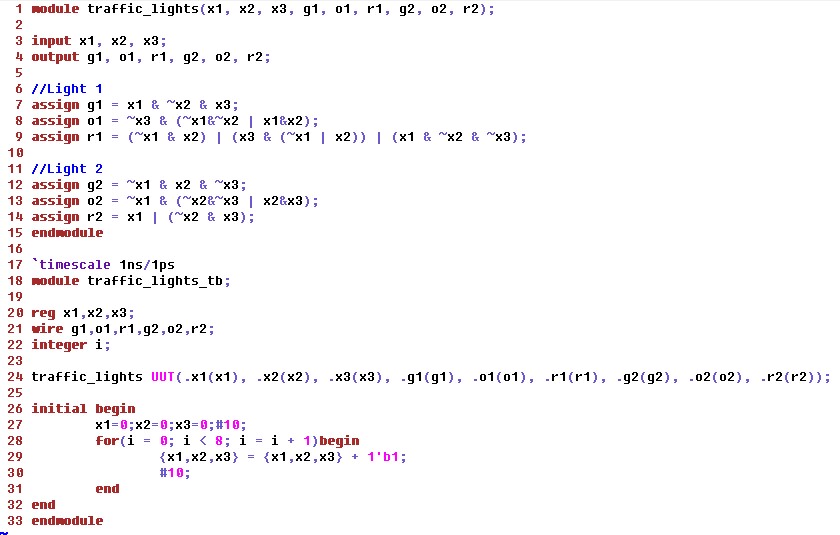

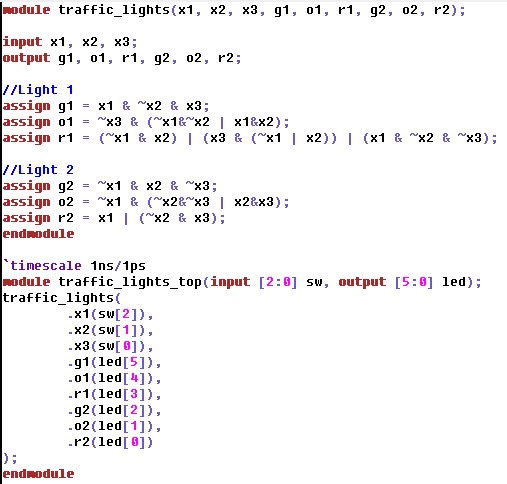

Figure 1. Verilog code for the light cycle simulation.

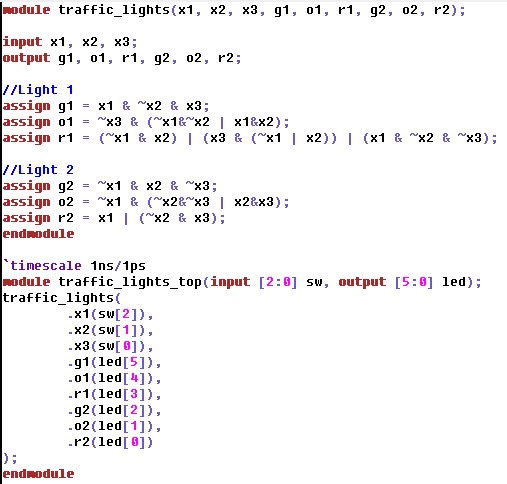

The light cycle may also be written for FPGA implimentation, seen in Figure 2.

Figure 2. Verilog code for the light cycle using the FPGA.

Figure 2. Verilog code for the light cycle using the FPGA.

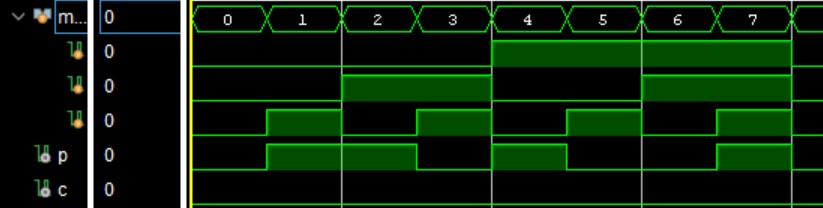

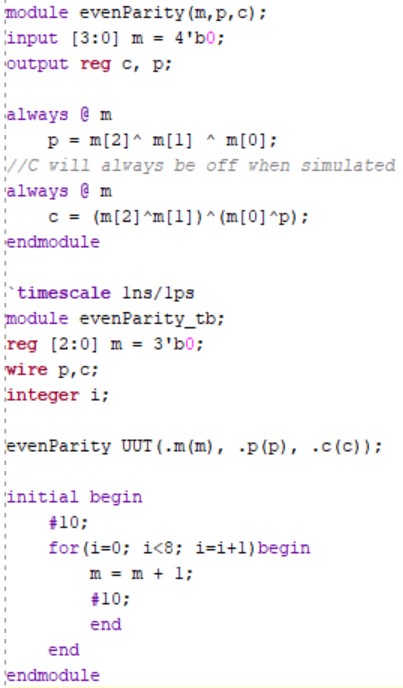

The verilog code for the even parity simulation is then written, see in Figure 3.

Figure 3. Verilog code for the even parity simulation.

Figure 3. Verilog code for the even parity simulation.