ENGR-433 Spring 2023

Lab 4: Combinational Logic Blocks

Name: Cheyenne Tucson

Email: crtucson@fortlewis.edu

Combinational Logic Blocks on a FPGA

1. Introduction

Proficiency with combinational logic is crucial for an ASIC engineer. Through

this lab, a traffic light controller and an even-parity checker/generator system

were described in Verilog, simulated in Vivado, and implemented on a FPGA via a

Basys3 protoboard.

2. Materials

- Basys 3 FPGA board

- Computer equipped with Vivado, a raw text editor, and a USB port.

- Micro-USB cable.

3. Procedure

Vivado was opened on a PC; a new RTL project was created,

the appropriate chipset was selected for compatability with the Basys 3 board,

a .xcf constraint file was attached to the project.

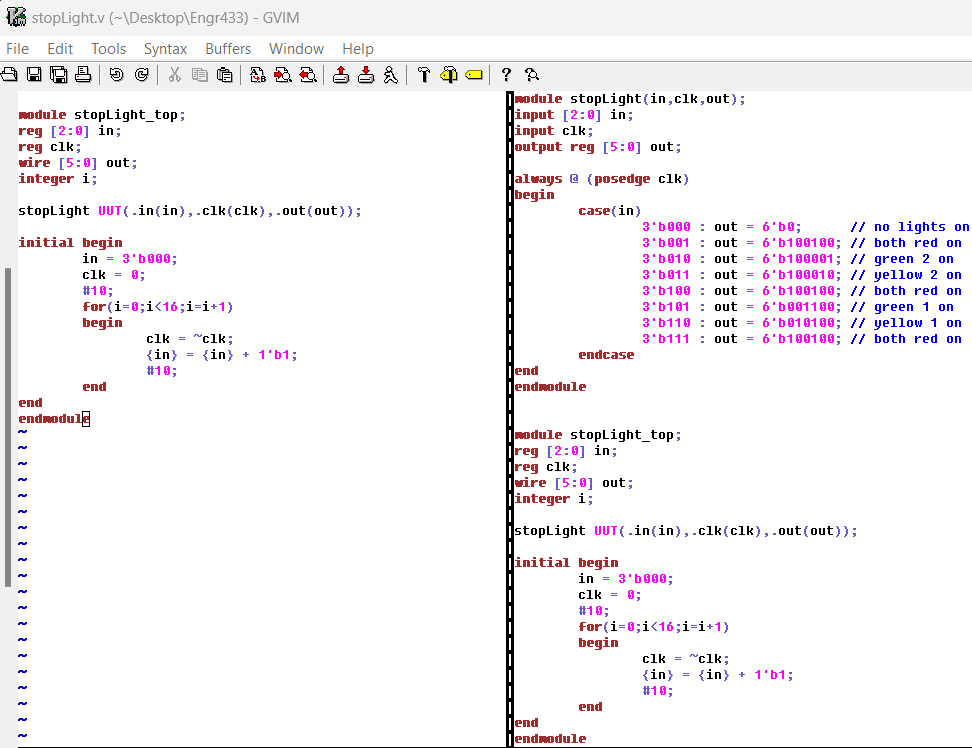

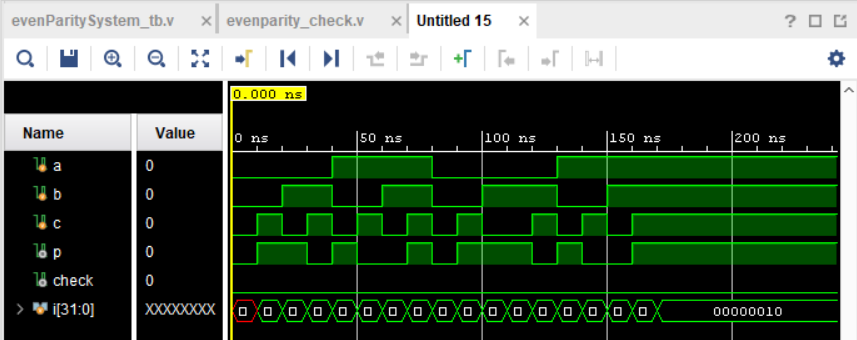

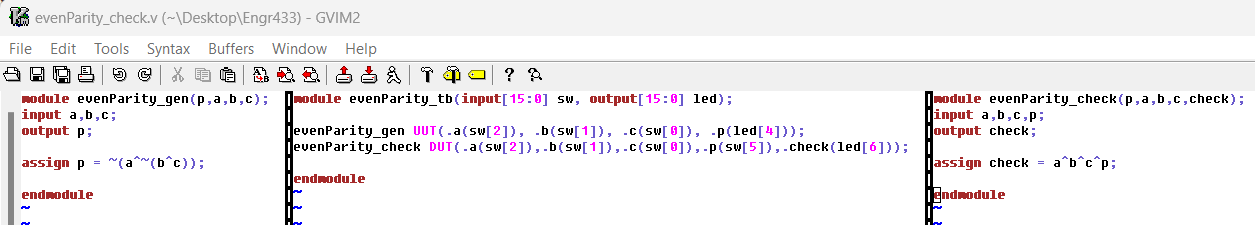

Verilog scripts for the following combinational logic blocks were written in gVim: a traffic light controller, and an even-parity generator/checker.

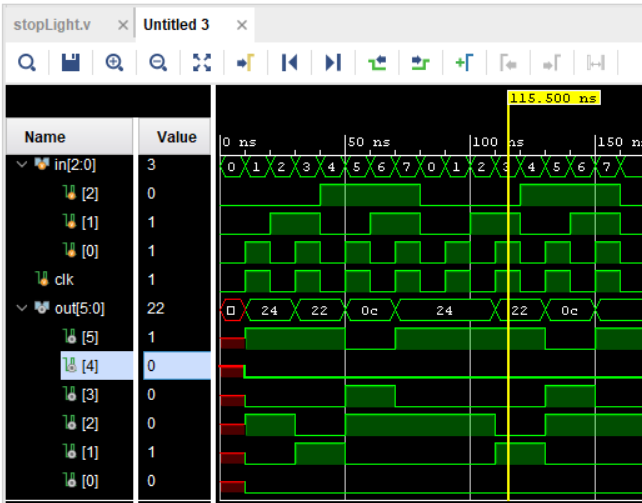

The digital circuit for the traffic light controller was described in gVim with Verilog HDL.

Testbench scripts were then written in Verilog for both behavioral simulation and FPGA implementation for each combinational logic block.

Once these scripts were completed, they were added to the project in Vivado and simulated/synthesized and the Basys 3 board was programmed with the

bitstream files generated for each digital circuit described.

5. Discussion

Being able to implement combinational logic blocks within digital circuits

is not as intimidating as it seems. The skills polished through completing this lab

will surely help me in the future as an ASIC Engineer in the industry.