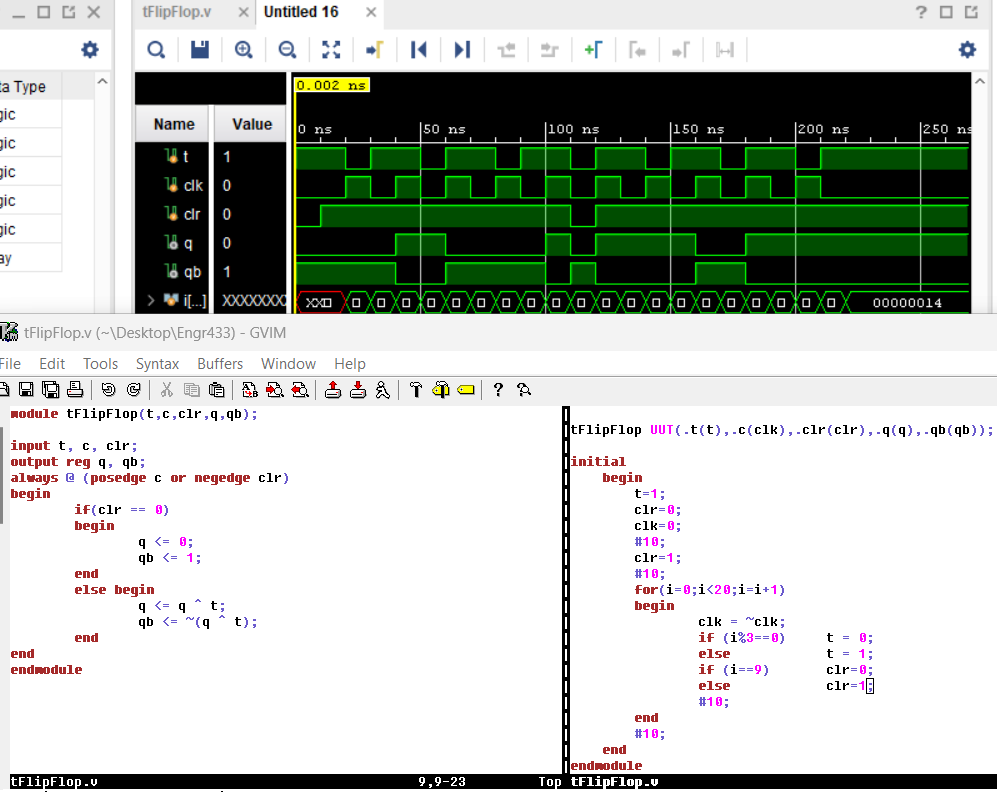

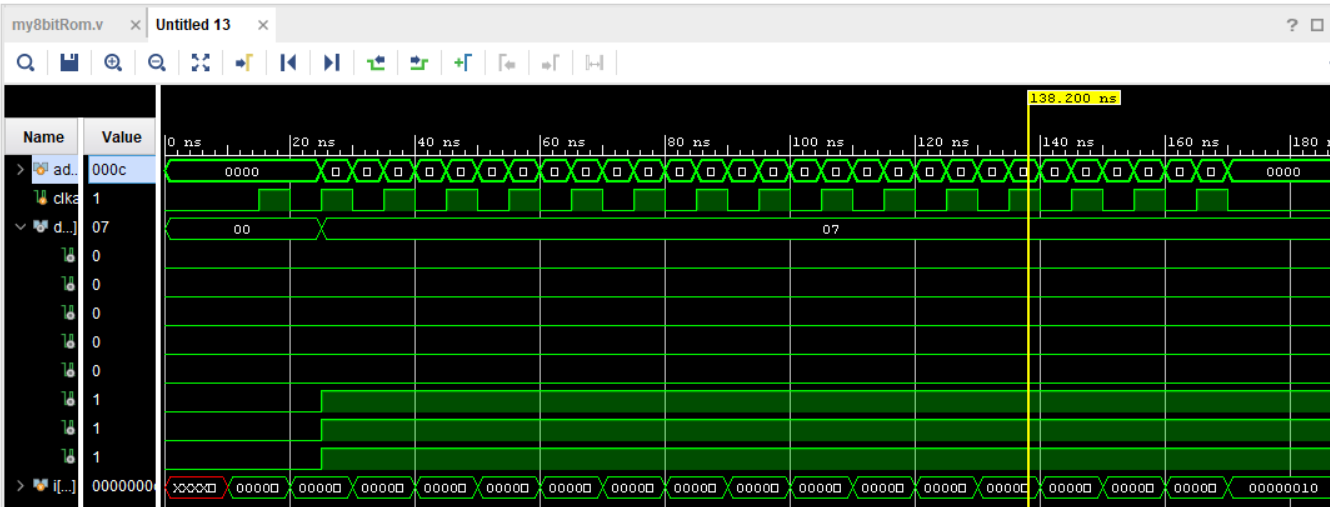

Task 1

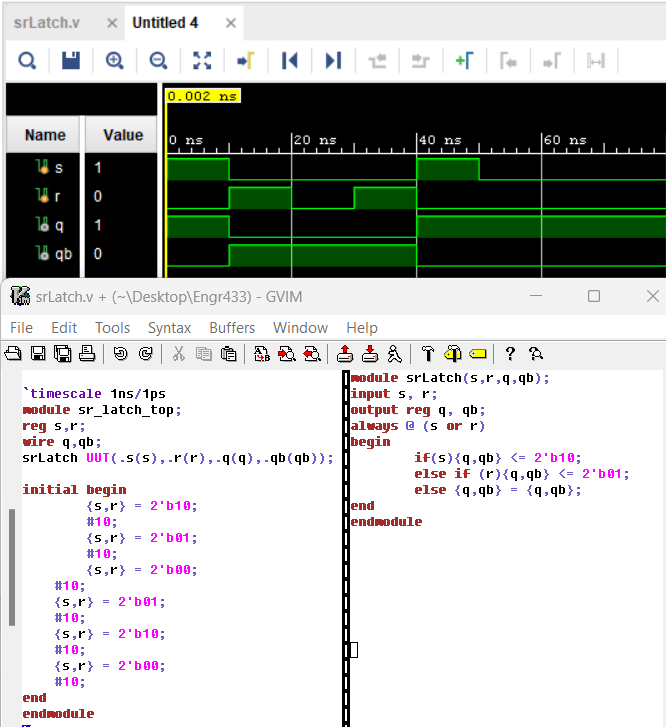

For the first task, a level-triggered SR Latch/Flip-flop was described in Verilog

and simulated in Vivado. The script and results of the simulation for the SR Latch can be found in Figure 1 below.

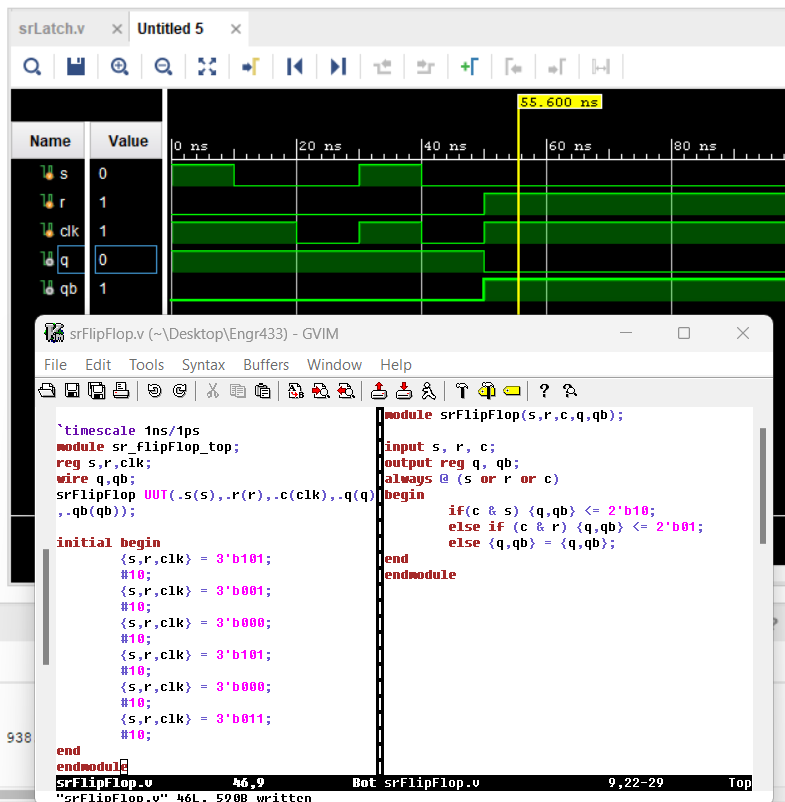

The SR Flip-flop script and simulation results can be found in Figure 2 below.

Figure 1. This is a screen-snip that contains the script and simulation results for the SR Latch. Figure 2. This is a screen-snip that contains the script and simulation results for the SR Flip-flop.

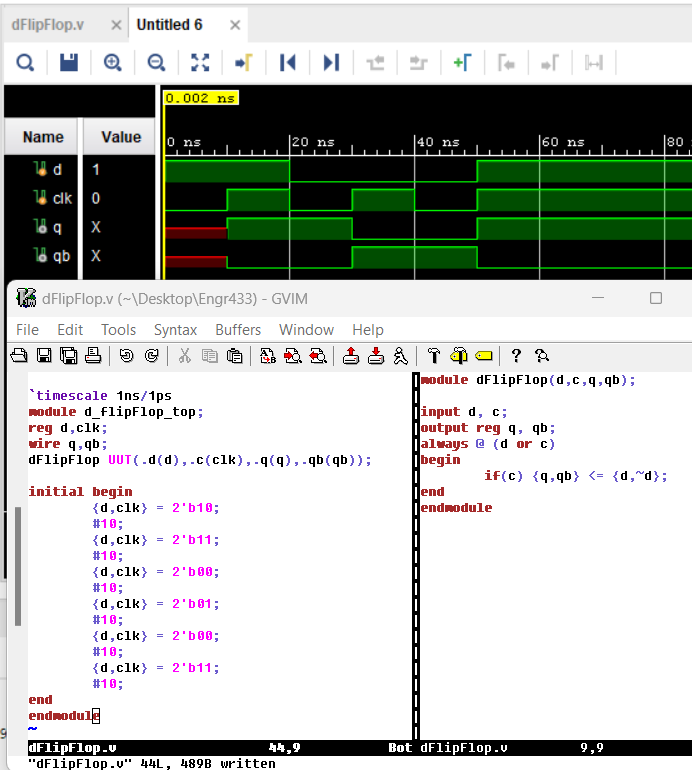

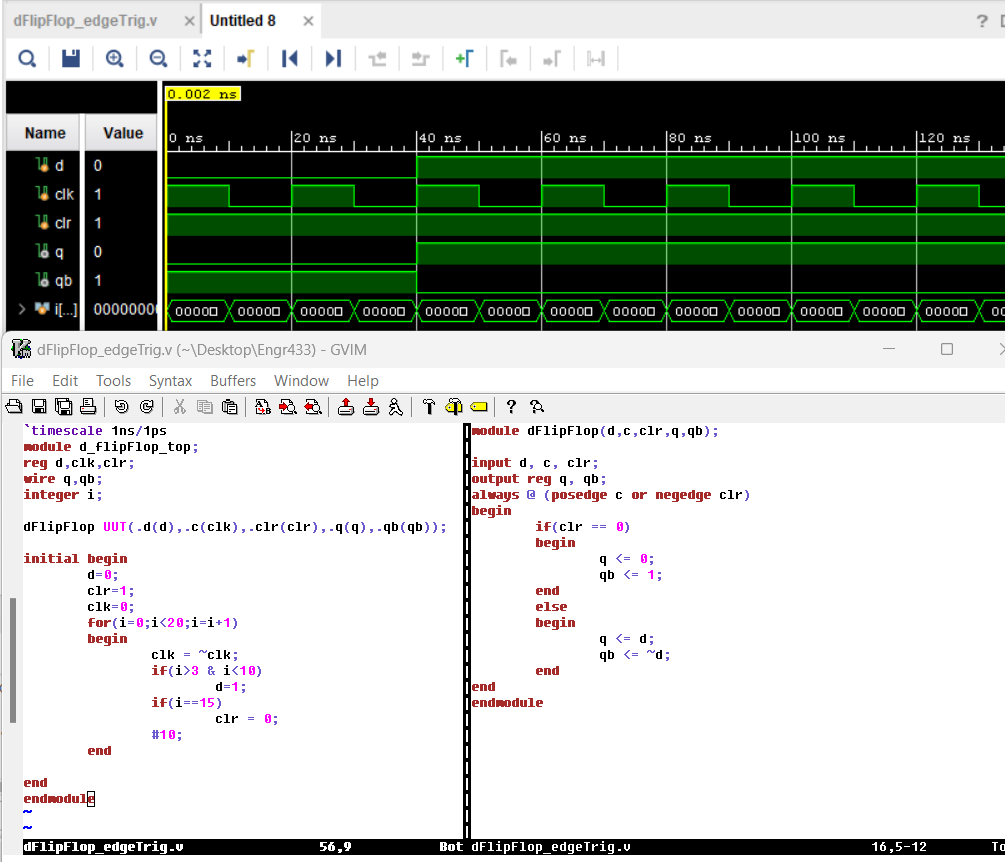

After the SR Latch and Flip-flop were done, a Data Flip-flop (D Flip-flop) was described in Verilog and simulated in Vivado. Both the level-triggered and edge-triggered versions were described in Verilog and simulated in Vivado. The results for the Level-triggered D Flip-flop can be seen in Figure 3 below. The Edge-triggered verision of the D Flip-flop can be seen in Figure 4 below.