CE 338 Lab 2023 Fall

Lab 3 Layout the R-2R DAC

Name: Vann Montoya

Email: bvmontoya

Layout the R-2R DAC

Introduction

- The purpose of this lab is to continue working with Electric VLSI and view different approaches to creating schematics.

Materials and Methods

- Electric VLSI

Results

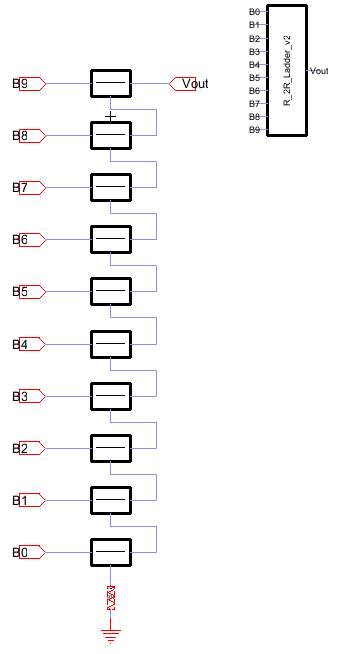

Task 1: Create the schematic of the subcells for the R-2R ladder. (40 points).

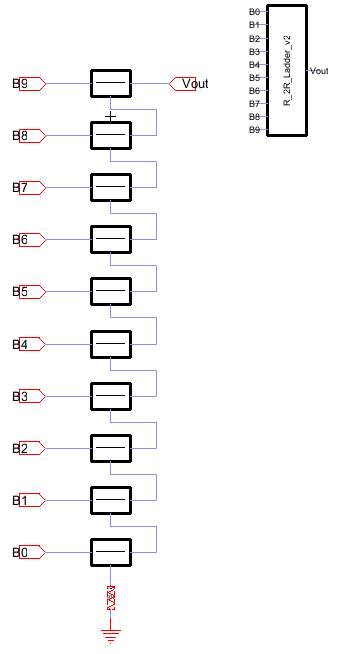

For the first task, we are to re-create the R-2R ladder from the previous lab but using subcells.

Here is my schematic and icon:

Figure 1: R-2R ladder schematic created using subcells.

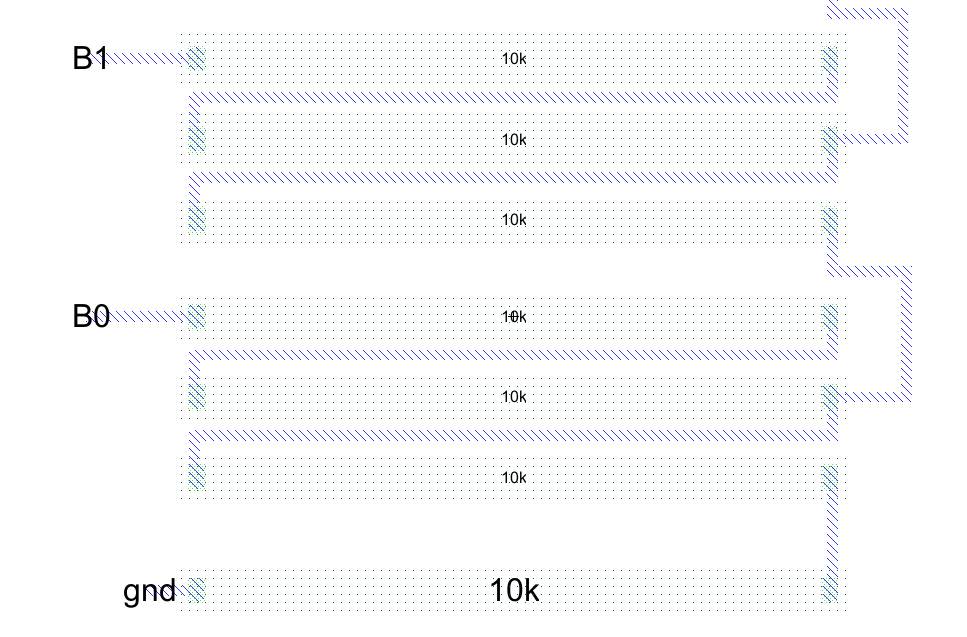

Task 2: Create the layout of the subcells for the R-2R ladder. (50 points).

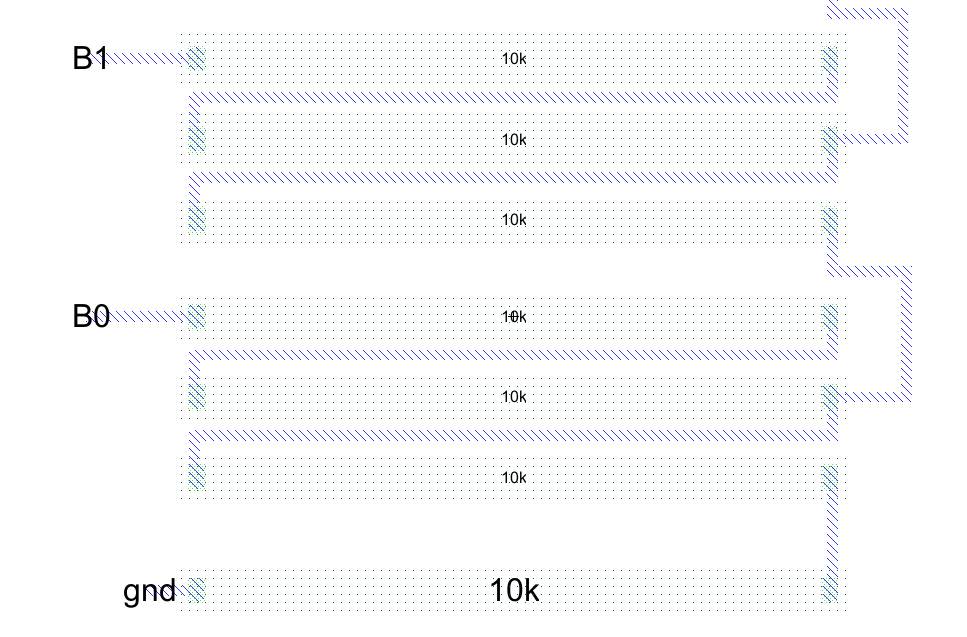

First, we created the layout of the R-2R subcells:

Figure 2: Layout of the subcell.

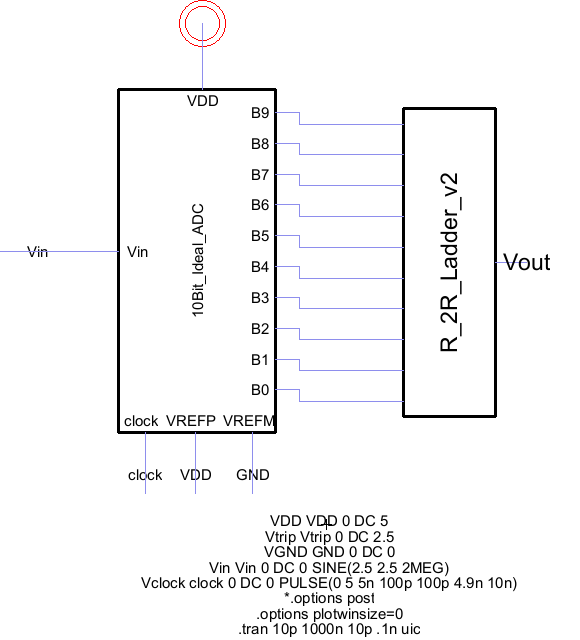

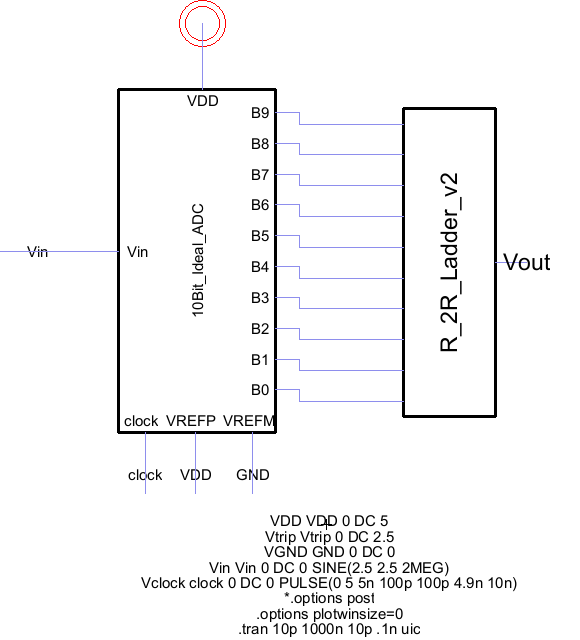

Then built the schematic for the R-2R v2:

Figure 3: Schematic of the R-2R Ladder v2.

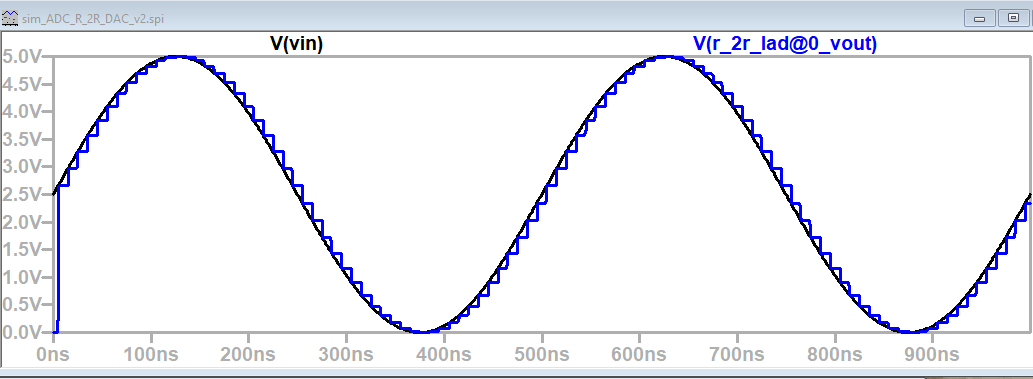

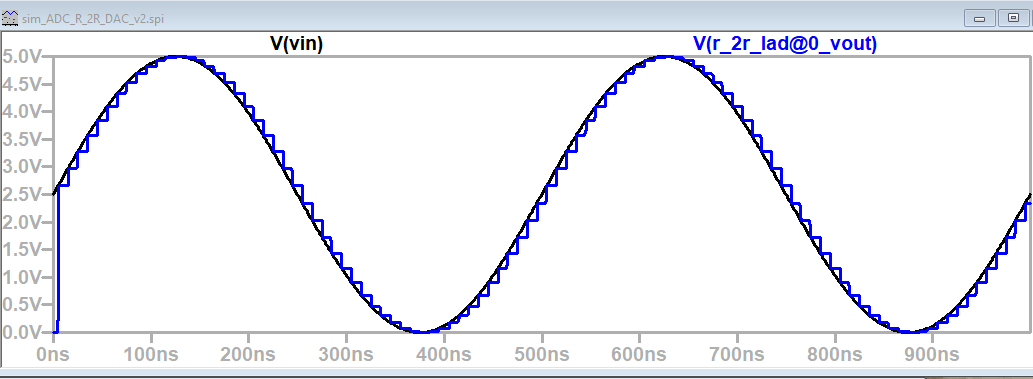

Here are the results from the simulation:

Figure 4: Results from the R-2R Ladder v2 simulation.

Discussion

This lab was a great way to practice using Electric VLSI.