Results

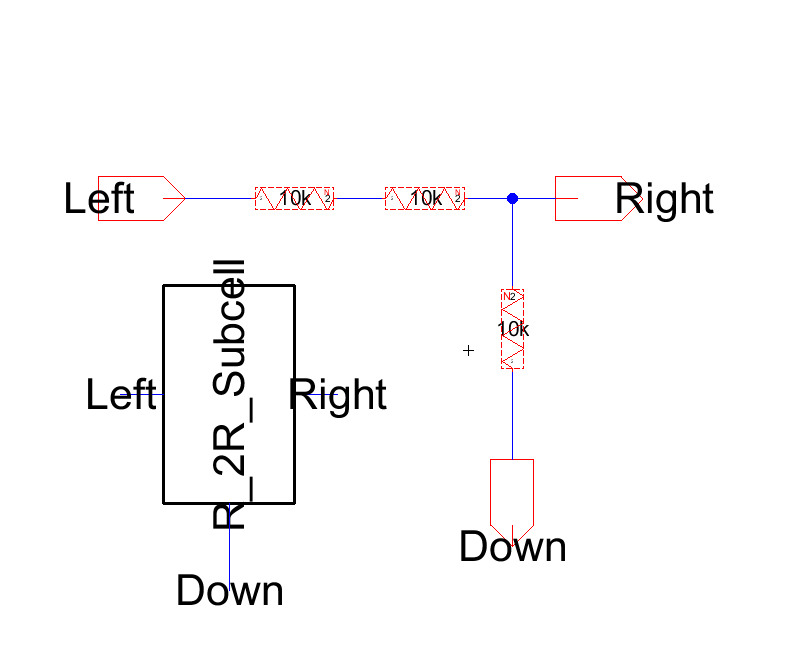

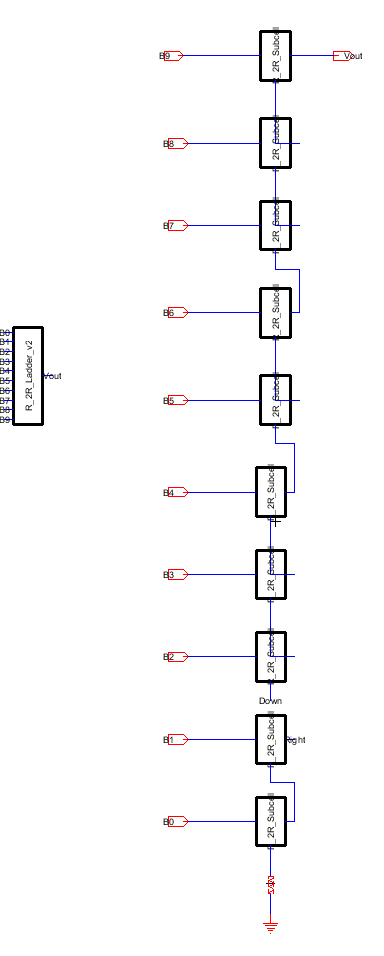

Task 1

Figure 1. Schematic of the Subcell and icon

Figure 2. Schematic of the R 2R ladder with subcells from Figure 1 and icon.

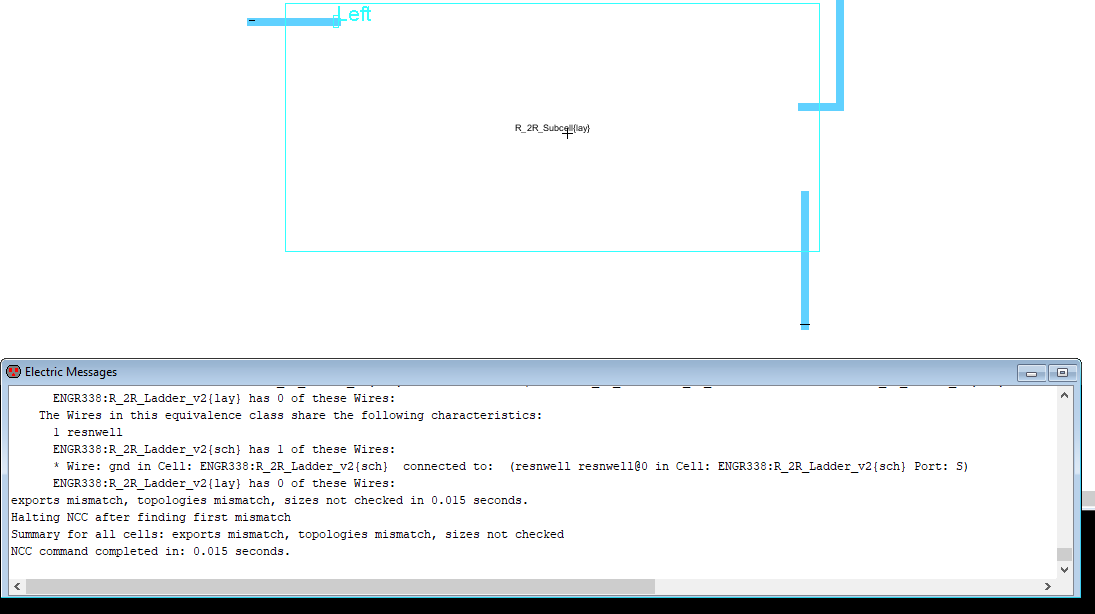

Task 2

Figure 3. Layout of the R 2R Ladder with R 2R subcell and Electric messages.

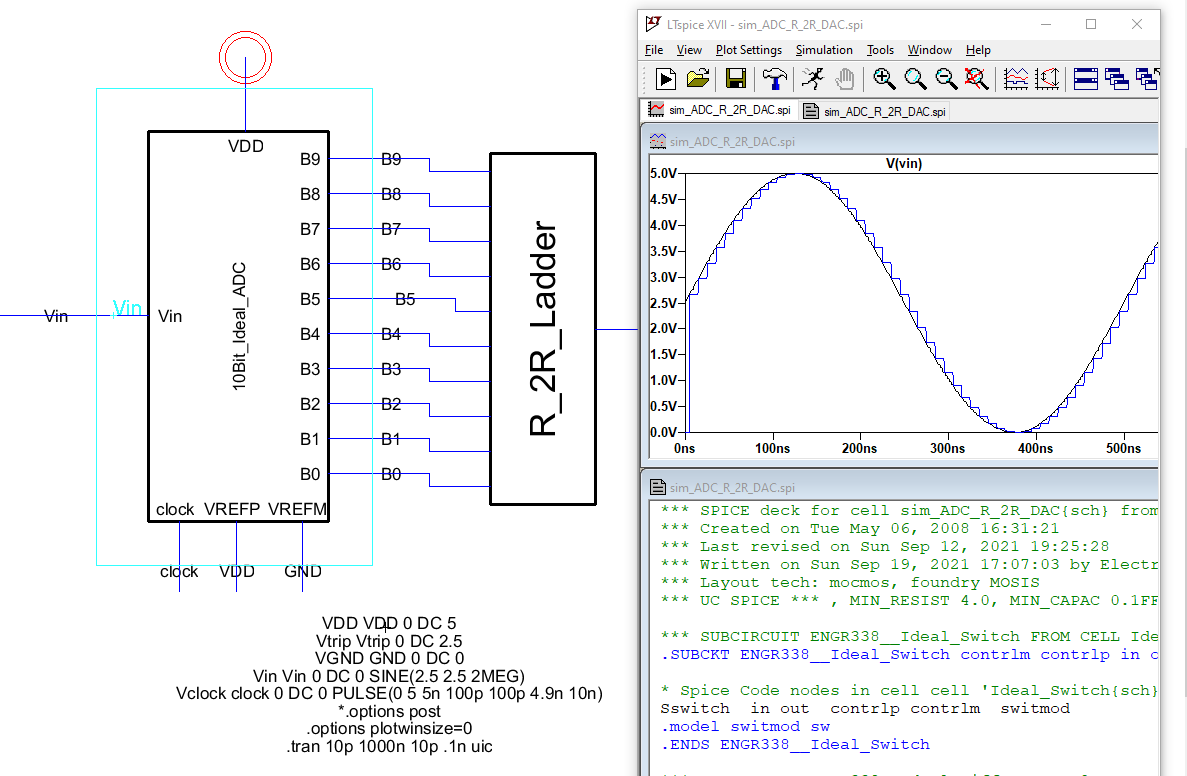

Figure 4. R 2R ladder version 2 connected with the 10 bit ideal ADC and

Discussion

This lab show two different ways of creating an R 2R ladder. Both in schematic and layout mode. Because the R 2R ladder has repeating resistor

pattern, we were able to create that resistor pattern and copy it as many times as needed. In this case it was ten times. This helped in creating

the circuit with minimal errors. It may also cut down on the acutal build time.