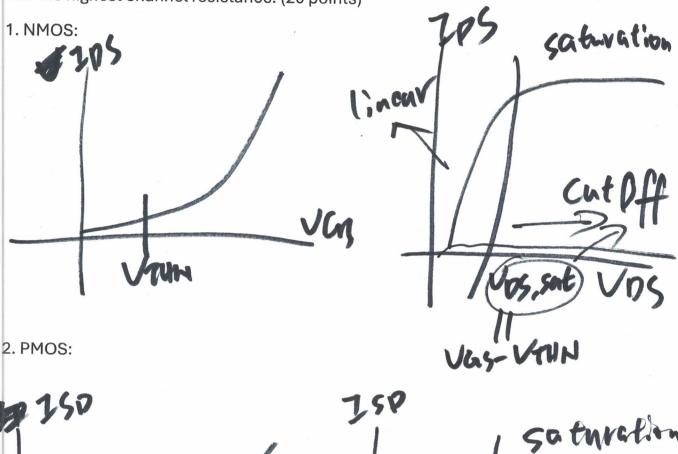

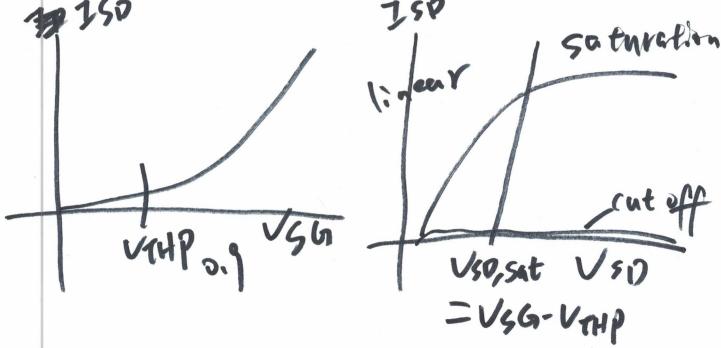

1. Sketch the two I-V curves of NMOS and PMOS. Label  $V_{THN}$ ,  $V_{THP}$ ,  $V_{DS,sat}$ ,  $V_{SD,sat}$ , all three operating regions for each type of transistor, and explain which region has the highest channel resistance. (20 points)

on Equation Wobility oxide layer tame

2 f electrons unit confacitance

KPn=120NA/V2 60V6, -95VGS+36x4=0 0.933V V1HV =0.8V

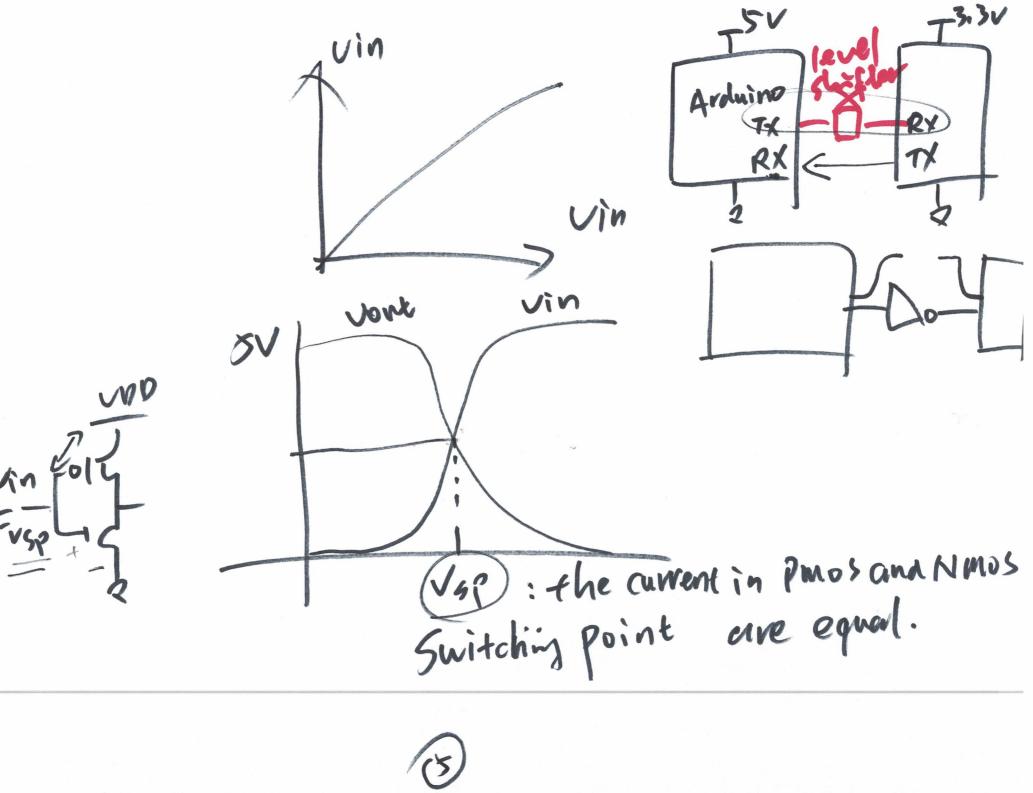

NMOS is good at

UDD-(Mo-With) passing 0's - UZHN Puros is good at Vow Vout

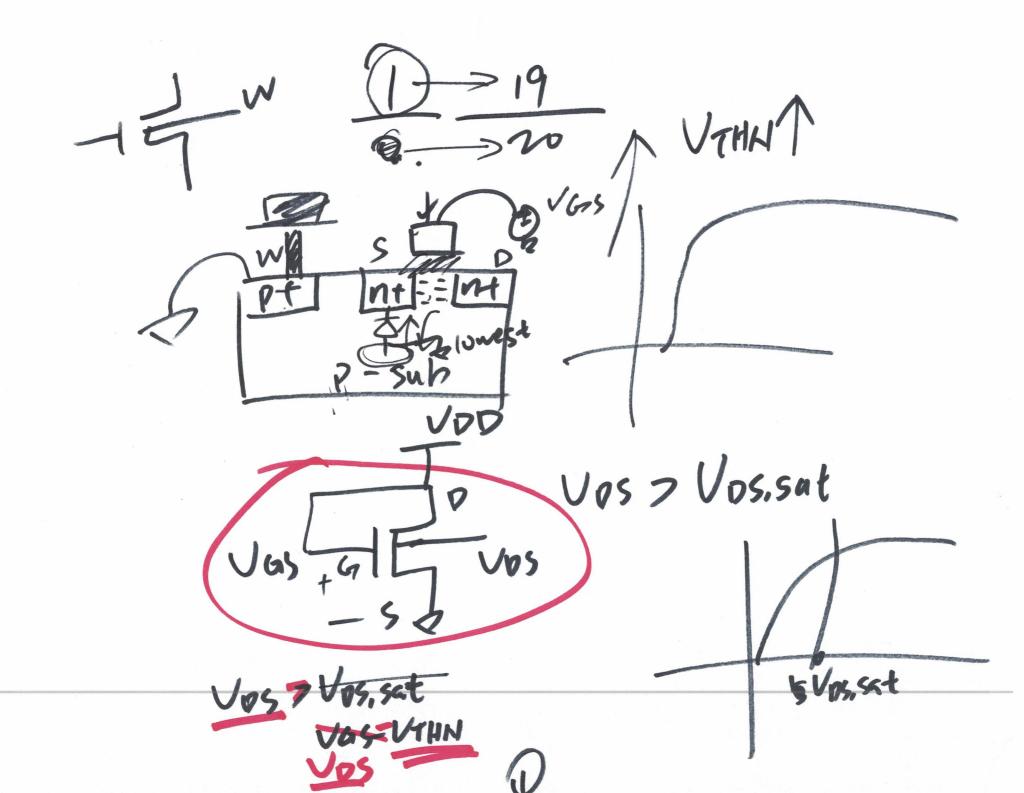

$$\frac{\beta_{n}}{2} \left(V_{65} - V_{7HN}\right)^{2} = \frac{\beta_{p}}{2} \left(V_{56} - V_{7Hp}\right)^{2}$$

$$\frac{\beta_{n}}{2} \left(V_{5p} - V_{7HN}\right)^{2} = \frac{\beta_{p}}{2} \left(V_{60} - V_{5p} - V_{7Hp}\right)^{2}$$

$$\frac{\beta_{n}}{\beta_{p}} = \frac{\left(V_{5p} - V_{7Hp}\right)^{2}}{V_{5p} - V_{7Hp}}$$

$$\frac{\beta_{n}}{\beta_{p}} = \frac{V_{5p} - V_{7Hp}}{V_{5p} - V_{7Hp}}$$

$$\frac{\beta_{p}}{\beta_{p}} = \frac{V_{5p} - V_{7Hp}}{V_{5p} - V_{7Hp}}$$

$$\frac{\gamma_{5p}}{\beta_{p}} = \frac{\gamma_{5p}}{\gamma_{7h}} = \frac{\gamma_{7h}}{\gamma_{7h}} = \frac{\gamma_{7h}}{\gamma_{7h}}$$