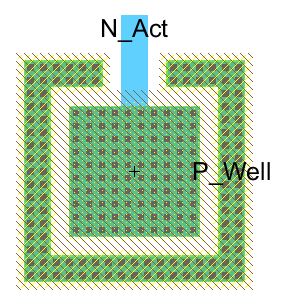

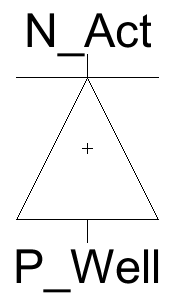

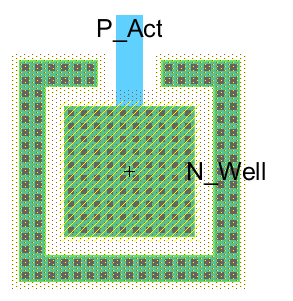

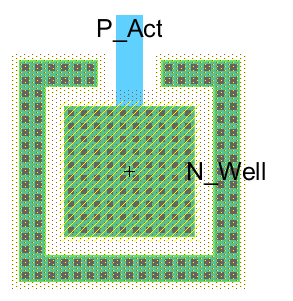

Nact_PWell_diode:

Layout and Schematic of a P-well based diode.

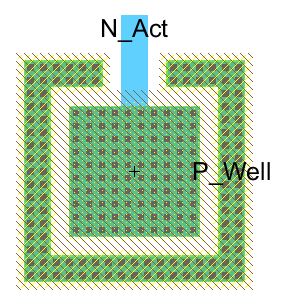

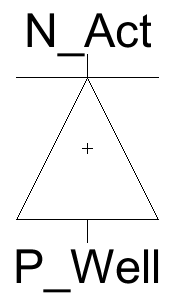

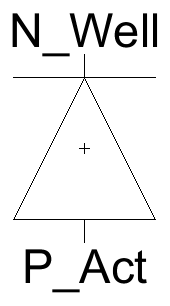

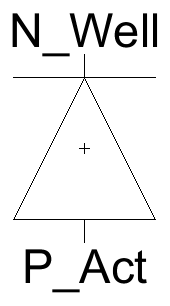

Pact_NWell_diode:

Layout and Schematic of a N-well based diode.

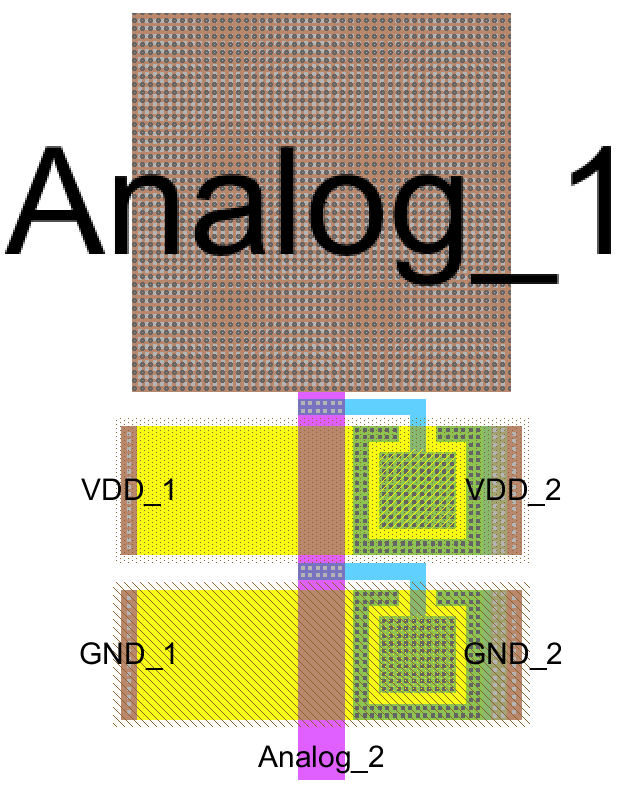

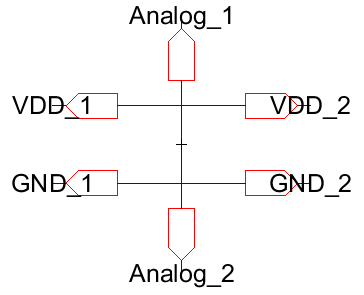

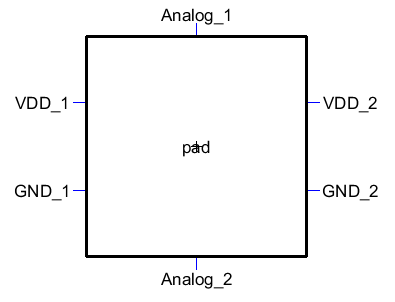

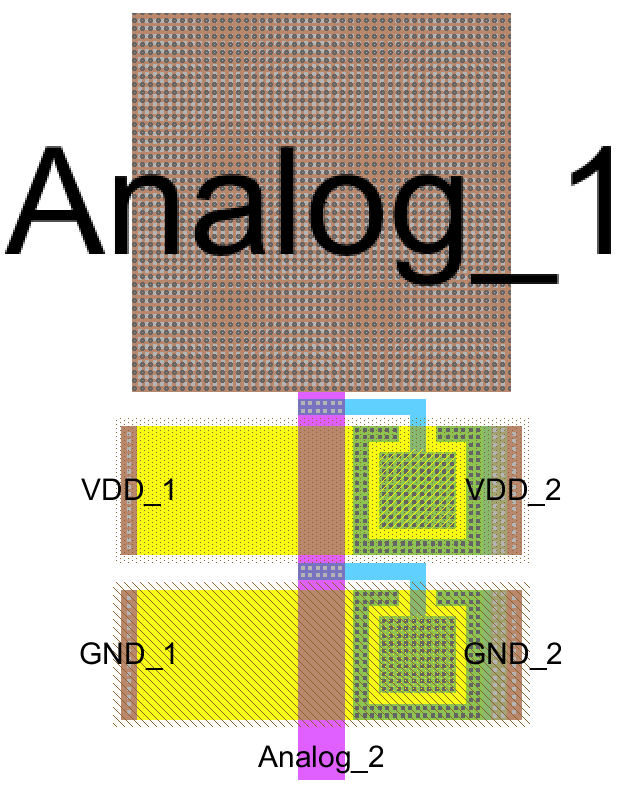

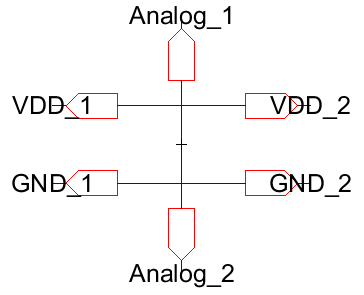

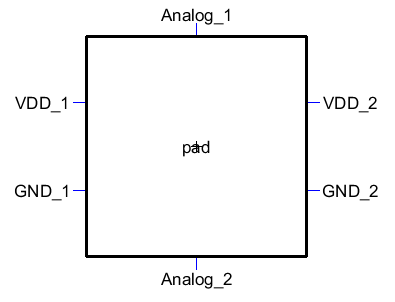

pad:

Layout and Schematic for a pad with ESD protection.

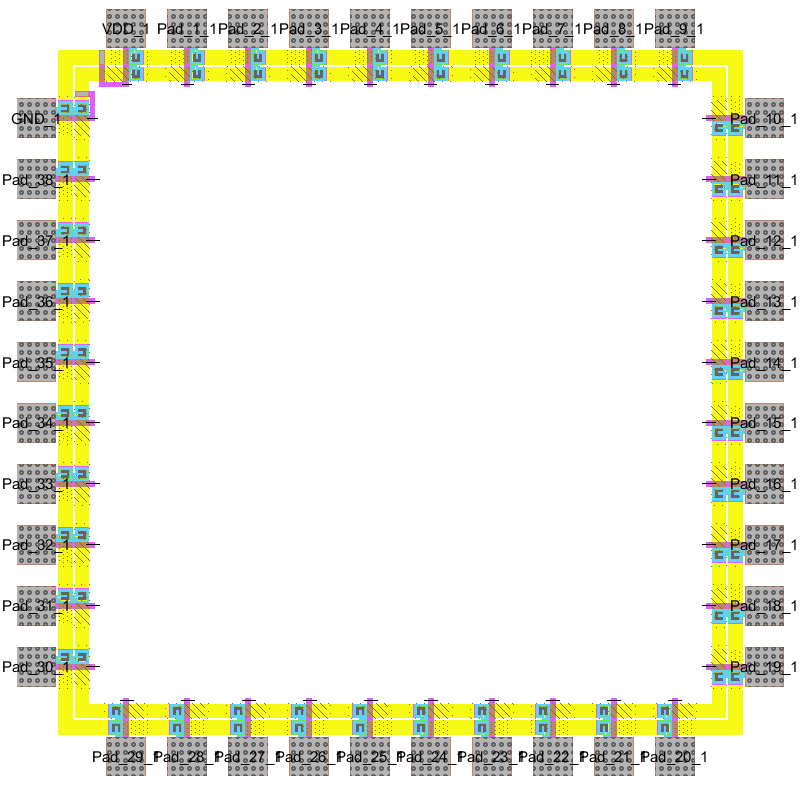

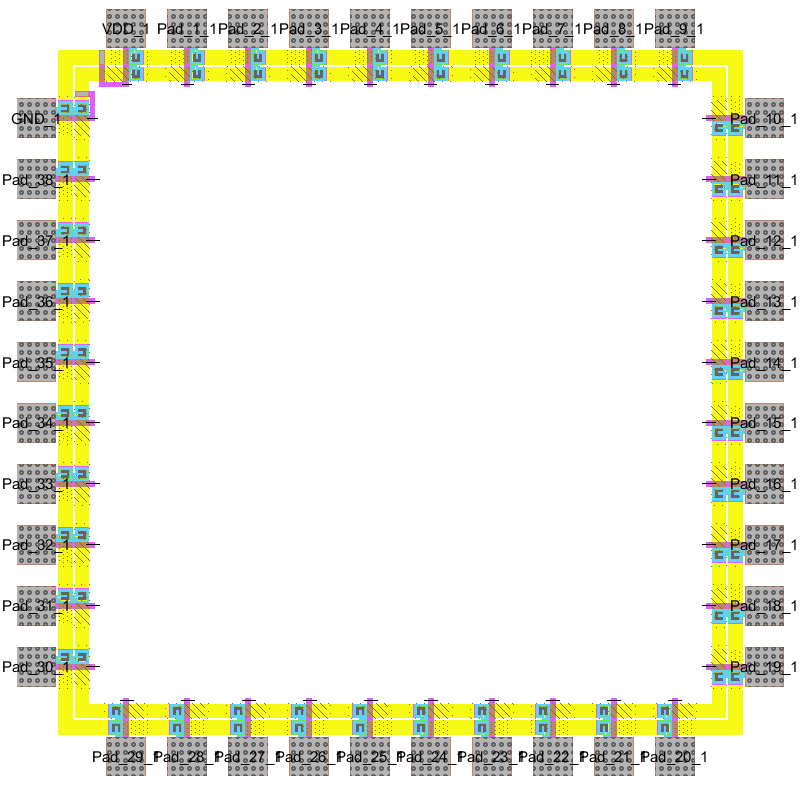

pad_frame:

Layout and Schematic for a pad fram ESD protection with pads for VDD, GND, and 38 generic pads.

inverter_20_10_pad: