ENGR337 Lab 2020 Spring

Lab 6 Layout an N-Well Resistor and Voltage Divider in ElectricVLSI

James Ferguson

jwferguson@fortlewis.edu

Lab 6 Layout an N-Well Resistor and Voltage Divider in ElectricVLSI

Objective:

The goal of this lab is to begin learning IC design with ElectricVLSI and to design a N-Well voltage divider as well as simulate the designs in LTspice. The tutorial followed for this lab can be found here.

Methods:

Setup of ElectricVLSI consisted of and providing the location of the LTspice executable and sxetting the chip fabrication process to C5 via MOSIS SCN3ME_SUBM.

Scematic:

The folowing Scematic is composed of two 10kΩ resistors to create a voltage dividor that has a transfer function of 1/2.

Layout:

The folowing shows the physical layout of the above schematic. Dotted regoins are N dopped semiconductors to act as resistors.

Results:

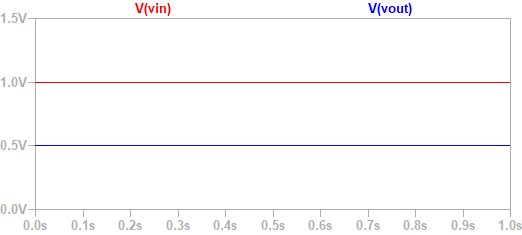

The following shows a LTspice simulation of the N-Well voltage dividor.

The circut performed as expected and divided the voltage in half.

The circut performed as expected and divided the voltage in half.