Lab 4 Combinational

Logic Blocks (updated 2/23/2022)

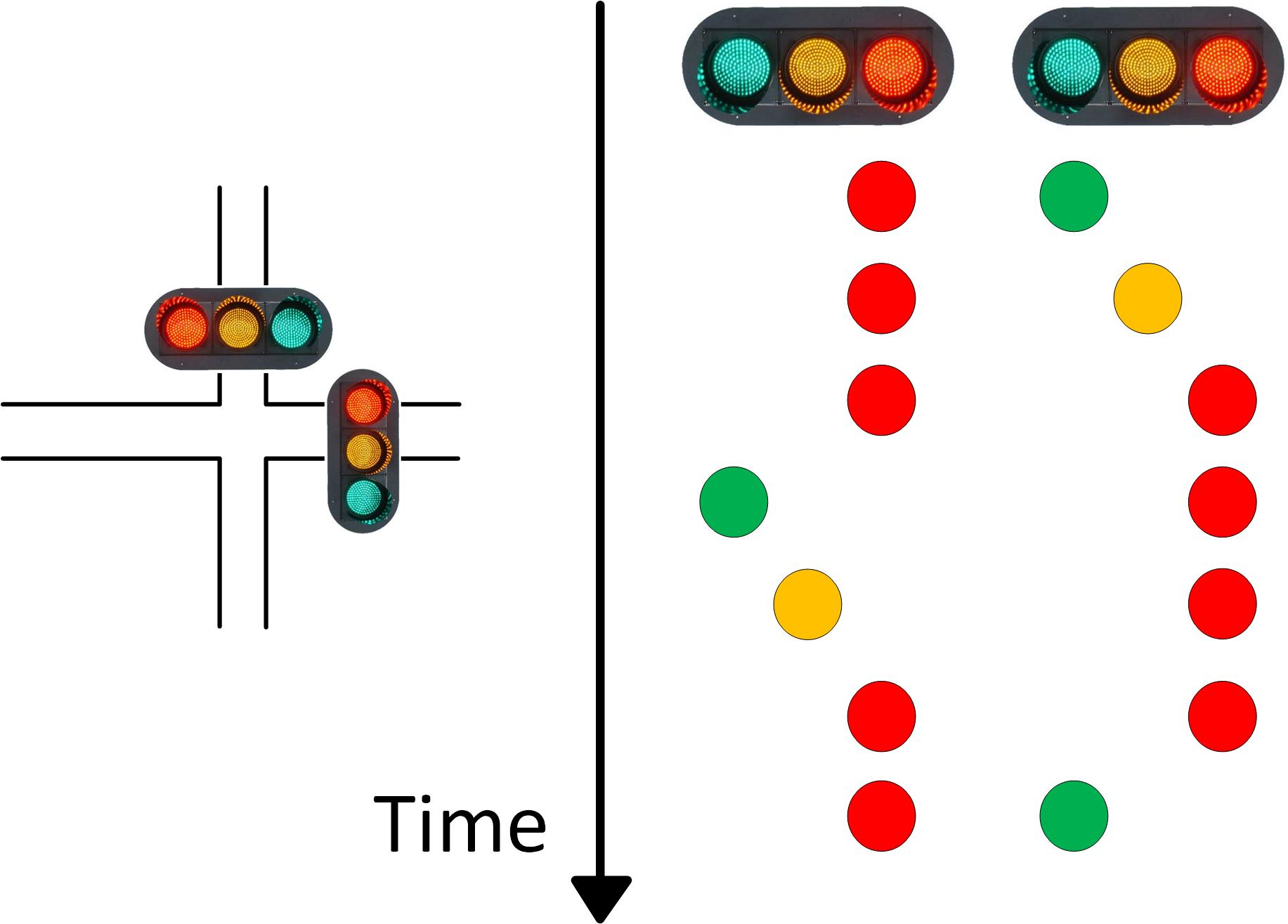

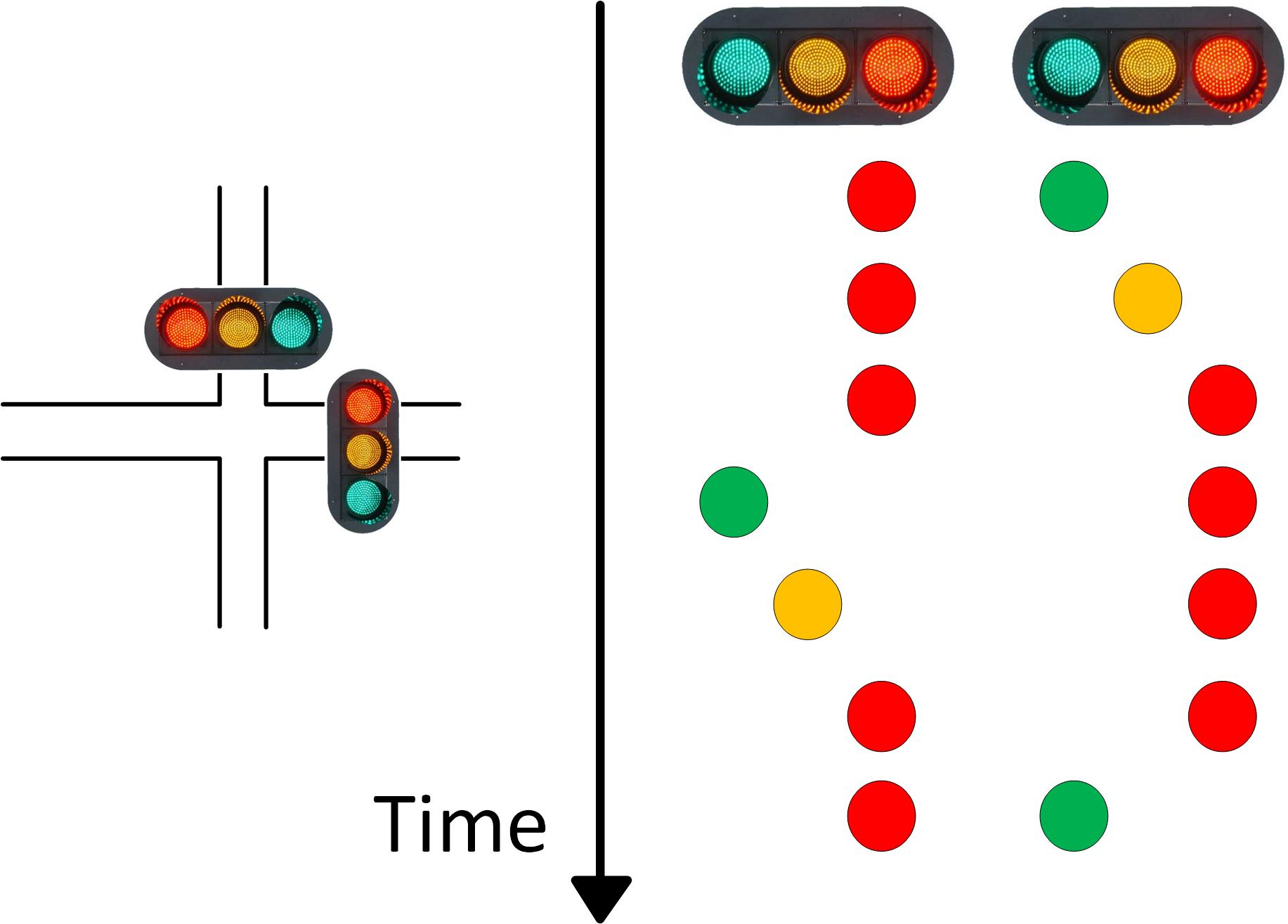

1. Think about how many

states the two-way traffic lights may have for each cycle.

The green light on one side truns yellow and then turns red before

the other light changes to green from red.

Draw the truth table for

all the states in one cycle of the traffic light change. Simplify

the logic equations for each light using the K map. Design the Verilog

model and the testbench, show the simulation results in Vivado. Use 6

leds on your Basys 3 board to implement the design. Show the demo video for credits. (50 points)

2. Design the Verilog models

of one even parity generator (3-bit

message with 1 parity bit) and one even parity checker. Put these two

models in one chip, use 'wires' to make connections. Design a testbench

to feed some binary numbers into the whole block and verify the

functionality of the system in vivado simulation. Implement it on your

Basys3 board, use switches as inputs and use LEDs as outputs. Show

simulation and board demo videos for credits. (50

points)